Forming method of shallow groove isolation and grinding method of semiconductor structure

A technology of isolation structure and grinding method, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems affecting the reliability of components, and achieve the effect of improving uniformity and reducing height difference

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

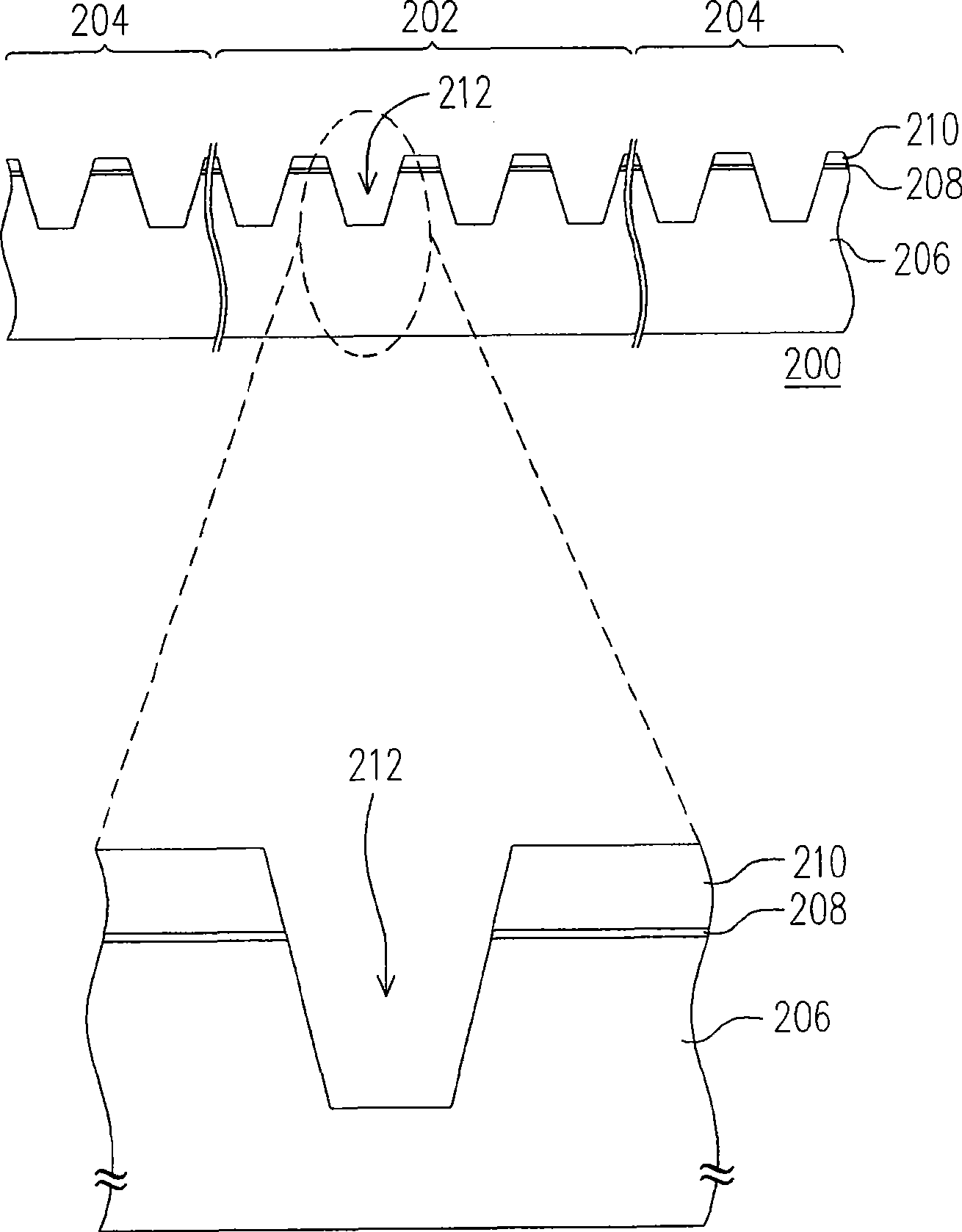

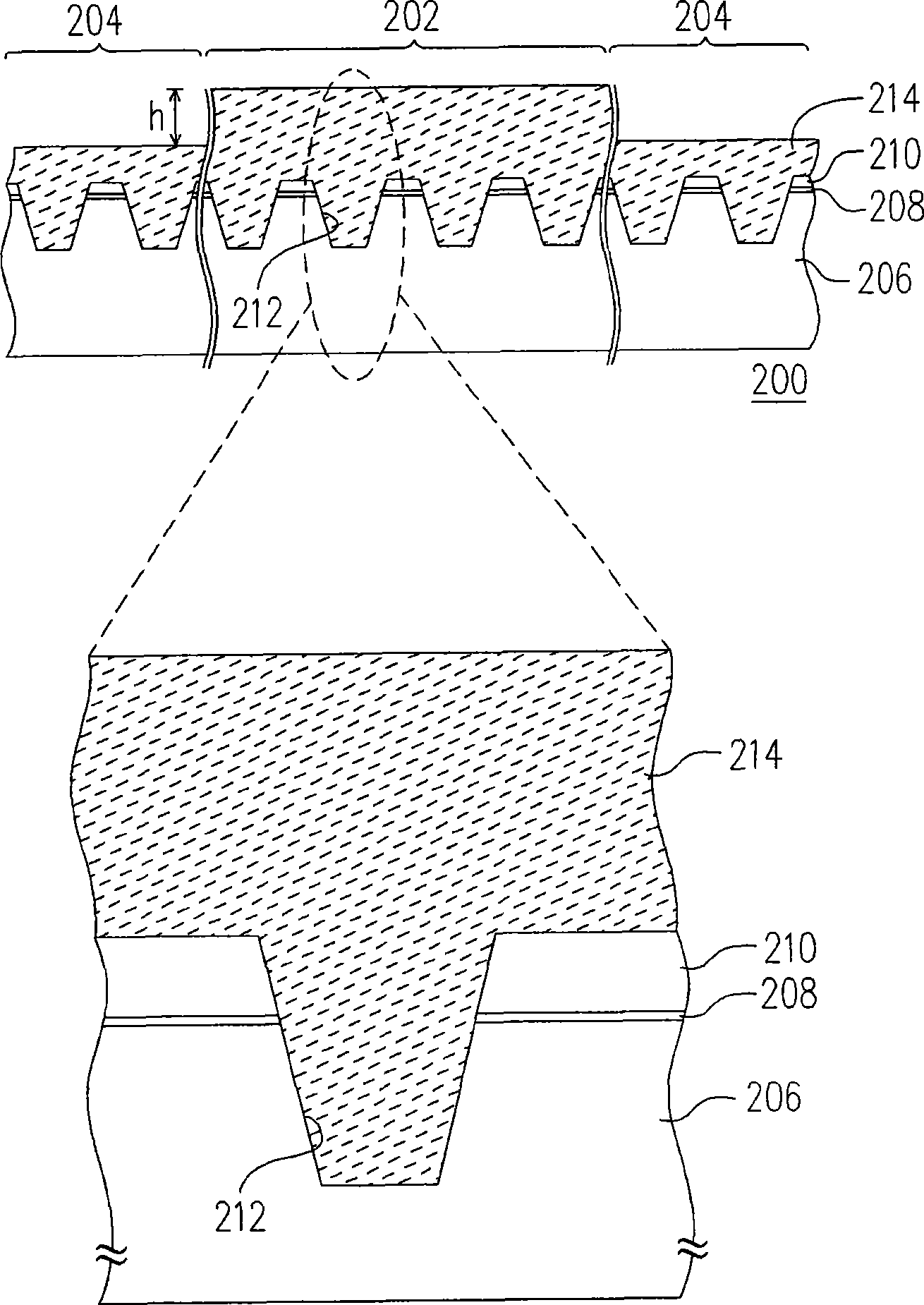

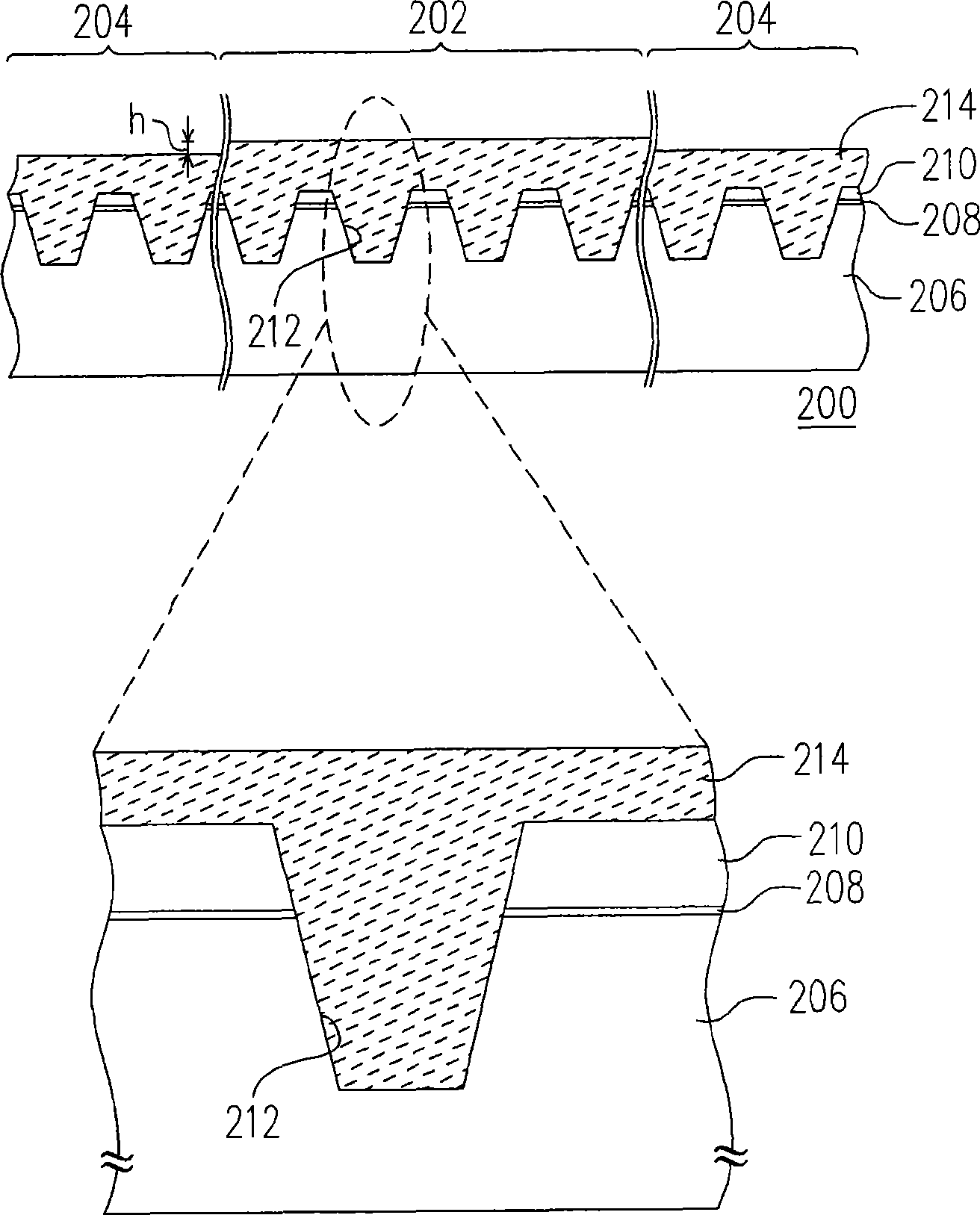

[0027] Figure 1A to Figure 1E It is a schematic cross-sectional view illustrating a formation process of a shallow trench isolation structure according to an embodiment of the present invention.

[0028] First, please refer to Figure 1A . A wafer 200 is provided that includes a semiconductor substrate 206 and can be divided into a central region 202 and an edge region 204 . Next, a pad layer 208 and a mask layer 210 are sequentially formed on the substrate 206 . The method for forming the pad layer 208 and the mask layer 210 is, for example, firstly forming a pad material layer, a mask material layer, and a patterned photoresist layer (not shown) on the substrate 206 in sequence. The material of the pad material layer is, for example, silicon oxide, and its formation method is, for example, thermal oxidation. The material of the mask material layer is, for example, silicon nitride, and its forming method is, for example, chemical vapor deposition. Then, using the pattern...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More