Method for improving thickness consistency of oxide layer on side wall of grid electrode and method for manufacturing grid electrode

A technology of oxide layer thickness and gate sidewall, which is applied in the manufacture of gates and semiconductor devices, can solve problems such as process complexity, etching process slowdown, and gate line width changes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

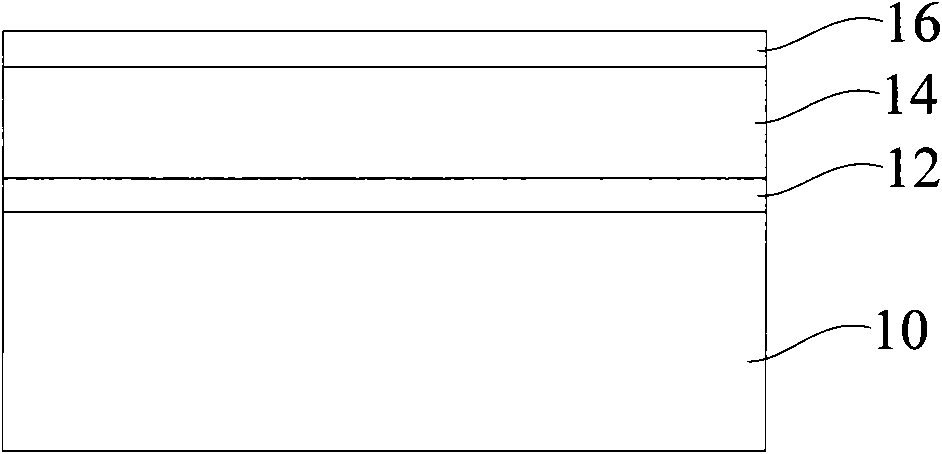

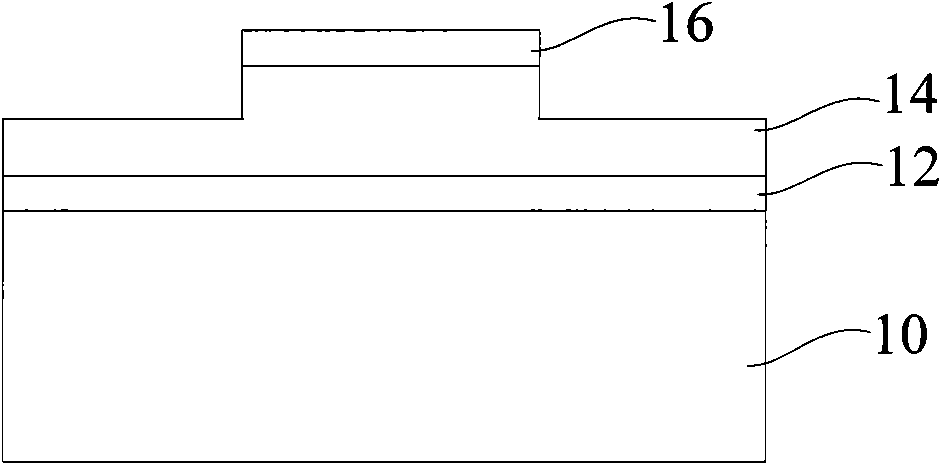

[0052] Please refer to Figure 5 Firstly, a semiconductor substrate 100 is raised, on which there is a gate dielectric layer 102 and a polysilicon layer 104 as a gate, and the polysilicon layer 104 is located on the gate dielectric layer 102 .

[0053] Wherein, the gate can also be a stacked structure of a polysilicon layer and other structures, such as Figure 7 The gate shown is a stacked structure of a polysilicon layer 104 and a metal silicide layer 105, and the metal silicide layer 105 is located on the polysilicon layer 104 to reduce the resistivity of the formed gate and improve the performance of the device;

[0054] another example Figure 8The gate shown is a stacked structure of a first polysilicon layer 104, a dielectric layer 105 and a second polysilicon layer 107, and the dielectric layer 105 is located between the first polysilicon layer 104 and the second polysilicon layer 107 Between; the dielectric layer 105 may be a stacked structure of silicon oxide-silic...

Embodiment 2

[0071] Embodiment 2 is still based on Figure 5 and Figure 6 Reference for explanation.

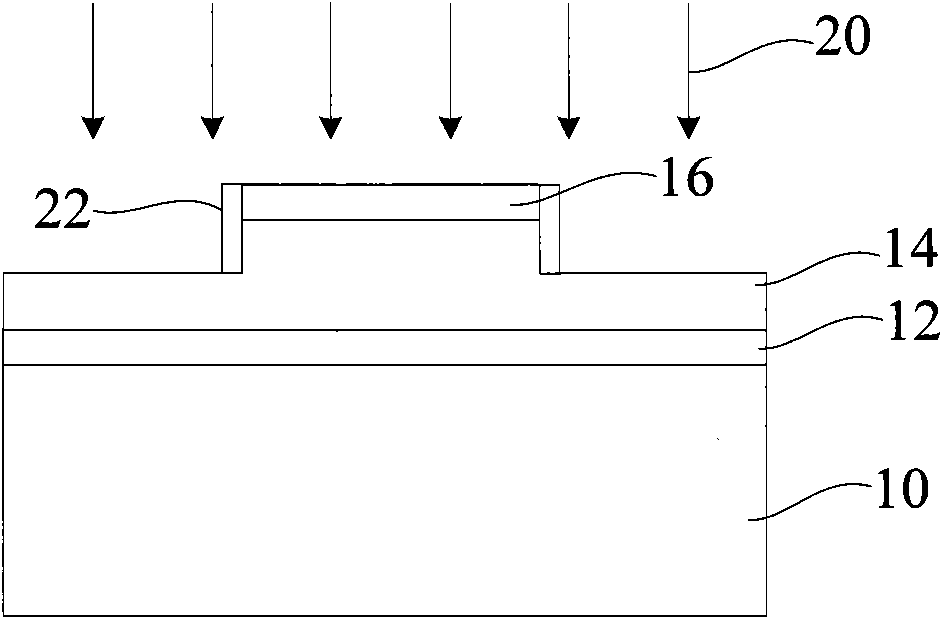

[0072] In this embodiment, before the in-situ water vapor generation oxidation is performed, an annealing process may be performed on the gate electrode containing the doped polysilicon layer, so that the impurity ions in the polysilicon layer are redistributed, thereby improving the performance of the polysilicon layer. The uniformity of the distribution of impurity ions reduces the influence of the uneven distribution of the ions on the thickness of the formed gate sidewall oxide layer, and then performs the in-situ water vapor oxidation process to further increase the thickness of the gate sidewall oxide layer Uniformity.

[0073] Detailed description will be given below.

[0074] Please refer to Figure 5 , firstly, a semiconductor substrate 100 is raised, on which there is a gate dielectric layer 102 and a polysilicon layer 104 as a gate, and the polysilicon layer 104 is located...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More