Data buffer of high-speed data exchange interface and data buffer control method thereof

A technology of data buffer and buffer, which is applied in the field of data communication, can solve problems such as limiting the flexibility of parallel processing systems, complex logic circuits, and unfavorable support for block transmission, so as to improve data transmission efficiency, improve circuit reliability, and increase flexibility. sexual effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

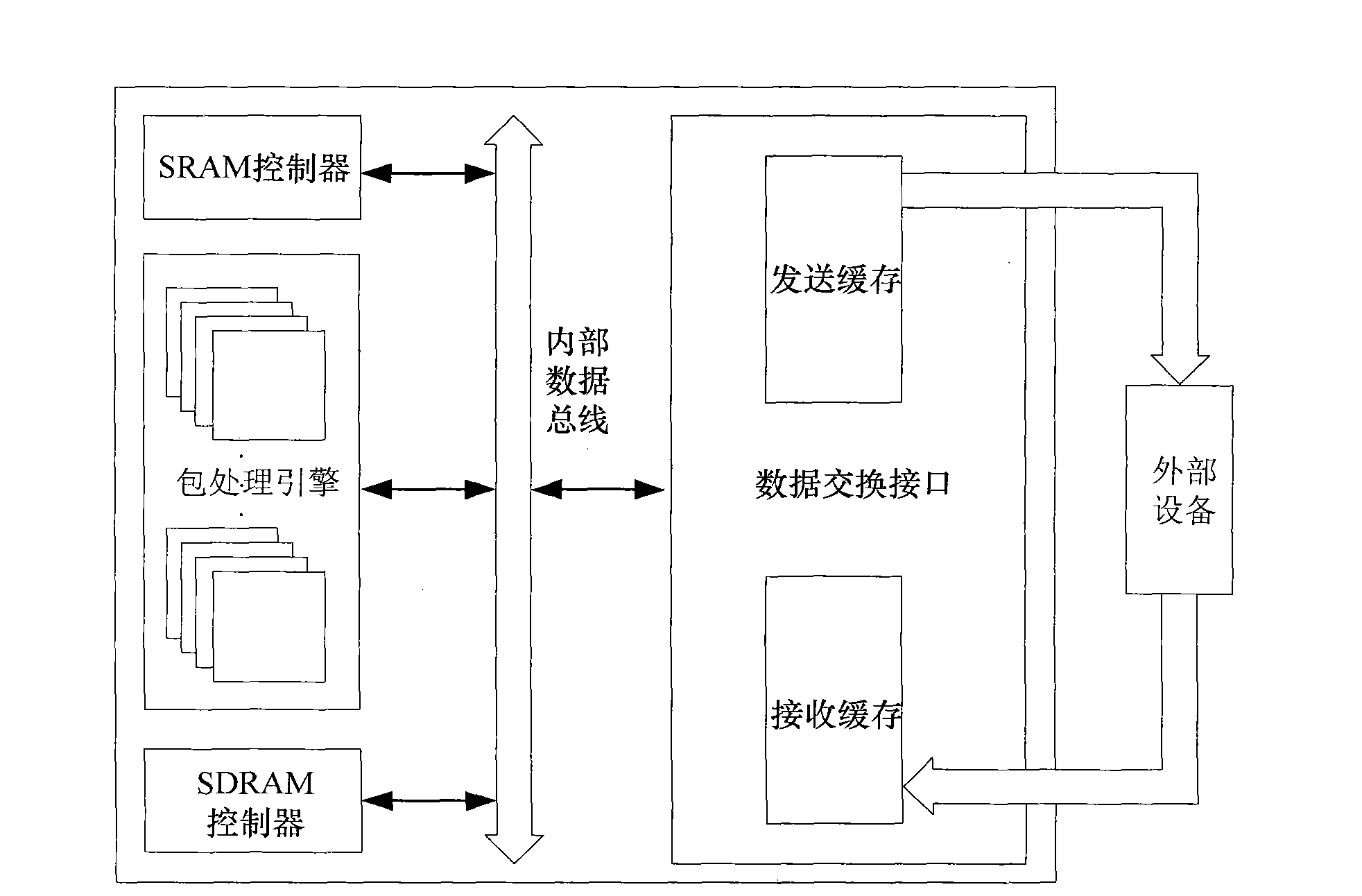

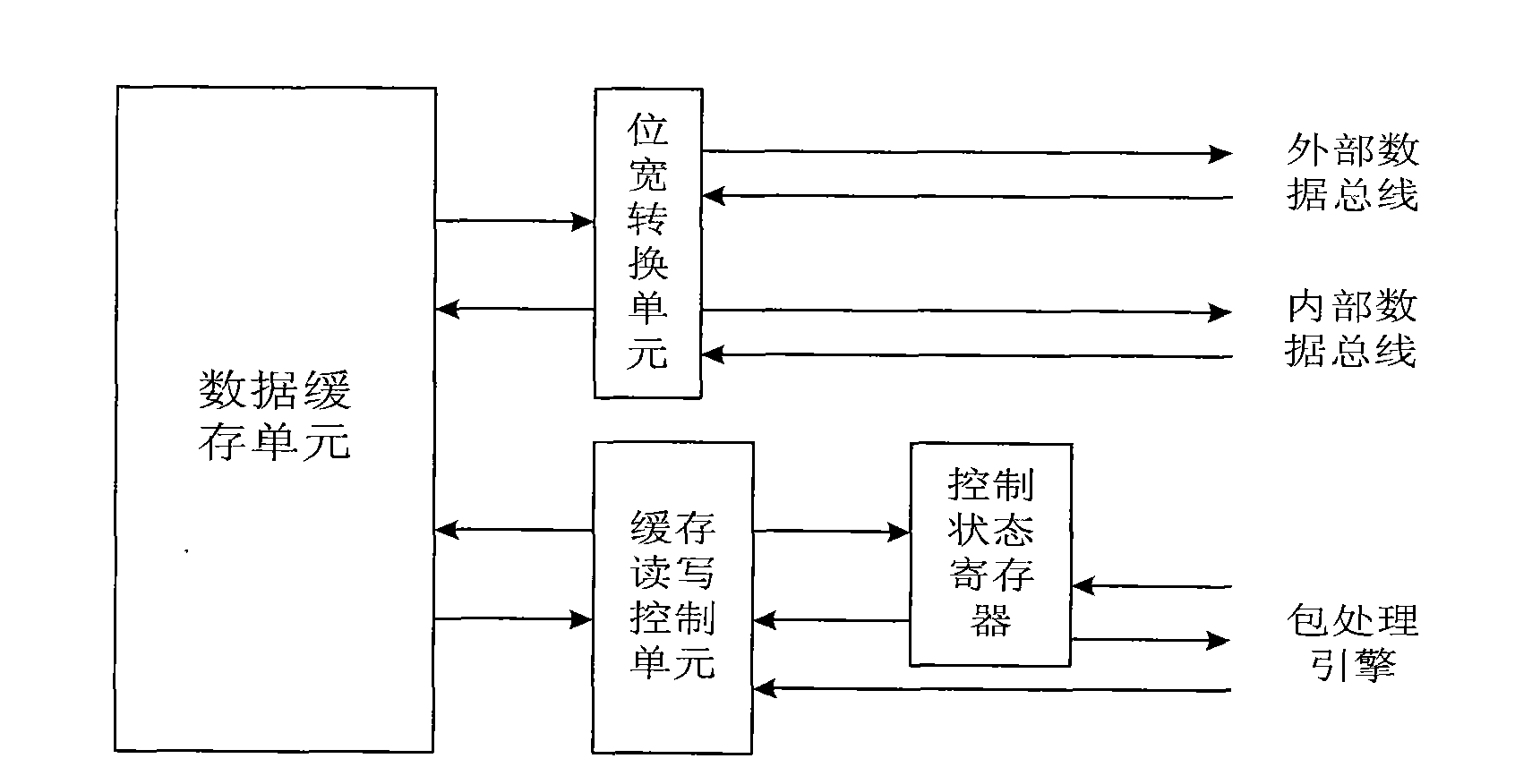

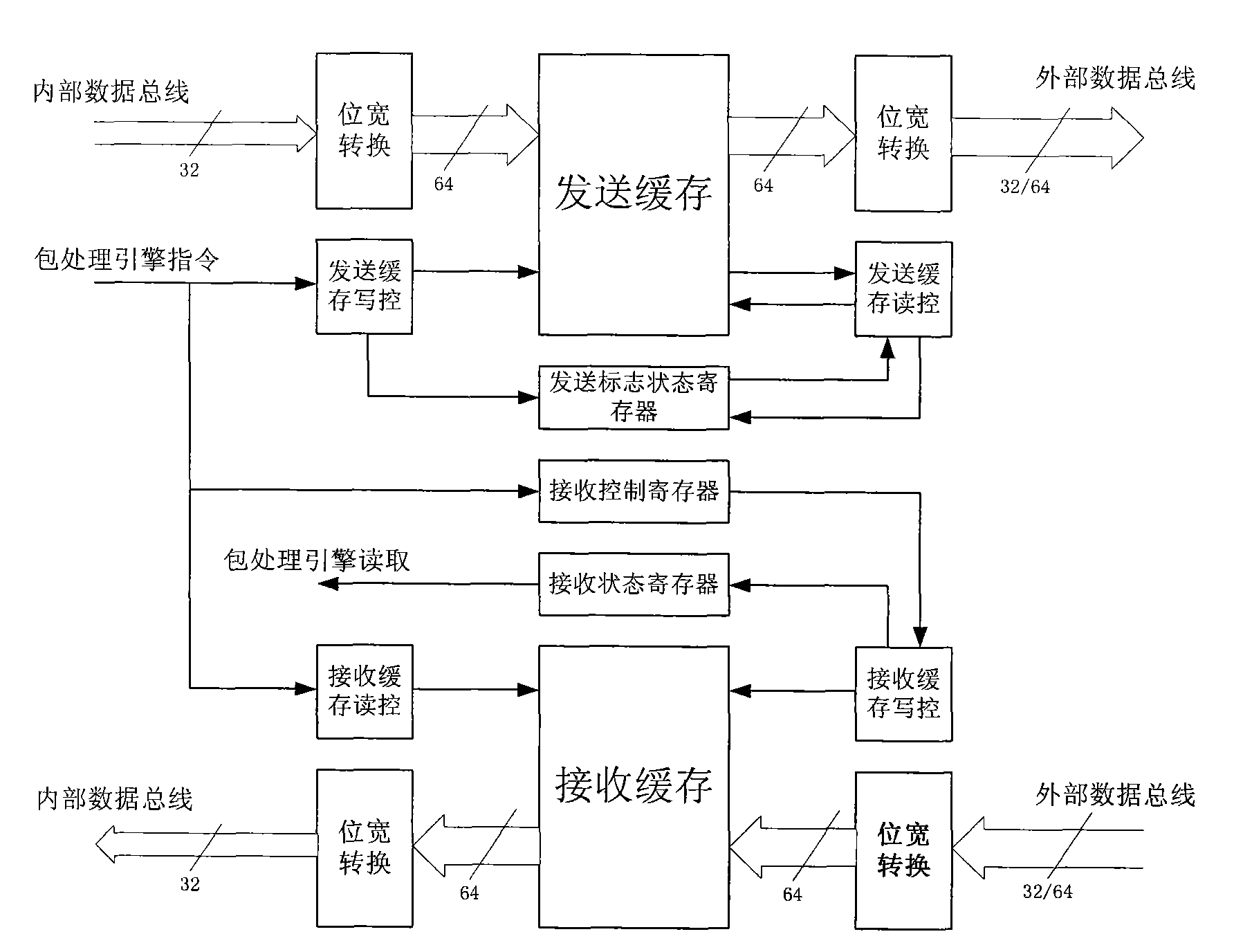

[0030] refer to figure 2 and image 3 , The data buffer of the present invention is mainly composed of a data storage unit, a buffer read and write control unit, a bit width conversion unit, and a control status register unit. in:

[0031] The data storage unit is composed of SRAM memory, the SRAM read and write bit width is 64 bits, the number of effective addresses is 320, the addressing space is 0x000 to 0x13F, and a 9-bit address bus is required to achieve an effective storage capacity of 20Kb. The SRAM memory is divided into units, and 320 effective addresses are abstractly divided into 32 units. Each unit can store 10 quadwords, that is, 80 bytes of data. For the sending buffer and receiving buffer, the unit content is slightly different. Figure 4The division structure of the units in the transmit and receive buffers is given. For the sending buffer, the first four words of each unit is the sending control information field, the content of this field indicates how t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More