Caching collaboration system of on-chip multi-core processor and cooperative processing method thereof

A multi-core processor and high-speed cache technology, applied in memory systems, electrical digital data processing, instruments, etc., can solve problems such as performance impact, uncoordinated policy control and management, and complexity, and achieve low average memory access latency and low average Memory access delay and failure rate, the effect of reducing hardware overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

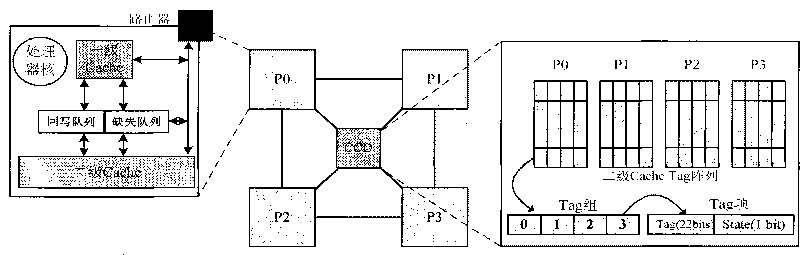

[0036] In this embodiment, the cooperative Cache on the multi-core processor is realized by using the simulation method technology. The multi-core simulator based on Simplescalar is used, and the relevant configuration parameters of the components are shown in Table 1. The hardware structure of the on-chip multi-core processor implemented by this configuration is as follows figure 1 shown.

[0037] Table 1 Simulator related configuration parameters

[0038]

[0039]

[0040] Each processor core of the on-chip multi-core processor has a private first-level instruction and data cache, and also has a private second-level cache body. The first-level cache and the second-level cache are strictly contained. Each processor core has a missing queue (MissQ), which accepts and processes data access requests or consistency requests of each processor core and accesses the secondary Cache or router, which handles local or remote requests; each processing The core has a write-back q...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More