Test circuit for predicting static discharge failure of integrated circuit and prediction method thereof

A failure testing and integrated circuit technology, applied in electronic circuit testing and other directions, can solve problems such as failure alarm, failure to meet circuit real-time test life prediction, inability to ESD real-time test, etc., to achieve the effect of consistent life curve

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

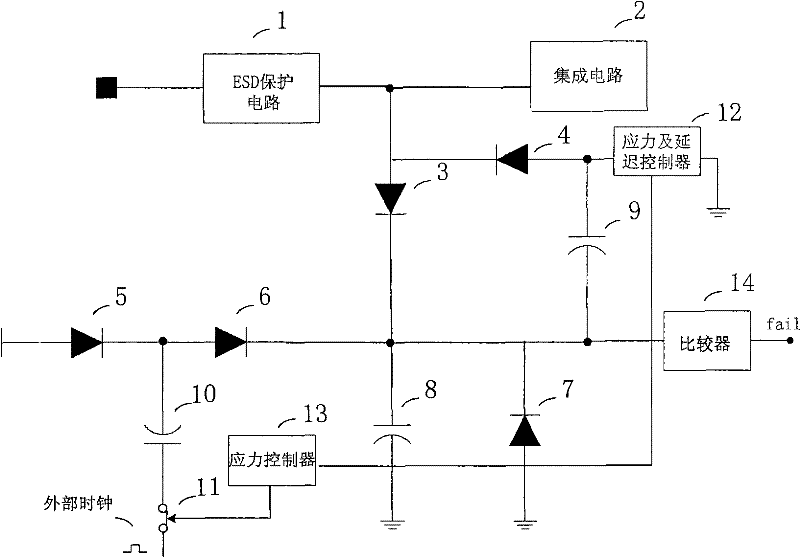

[0030] refer to figure 1 , the test circuit of the present invention includes: four diodes 3,4,5,6, clamping diode 7, two failure test capacitors 8,9, boost capacitor 10, switch circuit 11, stress and delay controller circuit 12, Stress controller circuit 13 and comparator 14. The diodes 3 and 4 are connected end to end to form an electrostatic discharge coupling circuit, and are connected in parallel with the integrated circuit 2 behind the ESD protection circuit 1 of the port. Capacitors 8 and 9 form an electrostatic discharge failure test structure. The gate of the capacitor 8 is respectively connected with the cathodes of the diodes 3 and 6, the gate of the capacitor 9, the anode of the diode 7 and the input terminal of the comparator. When positive ESD stress occurs at the port, diode 3 couples the positive ESD stress that has not been fully discharged to the gates of capacitors 8 and 9, and when negative ESD stress occurs at the port, diode 4 couples the negative ESD s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More