Nano-tubes semiconductor device and preparation method thereof

A semiconductor and device technology, which is applied in the field of nanotube vertical channel metal oxide silicon field effect transistor semiconductor devices, can solve the complex and expensive processing technology of shielded gate structure transistors, reduce the switching speed of shielded gate structure transistors, increase the Drain-source "on" impedance variation range and other issues, to achieve the effect of improving conversion performance, reducing parasitic capacitance, and high conversion speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

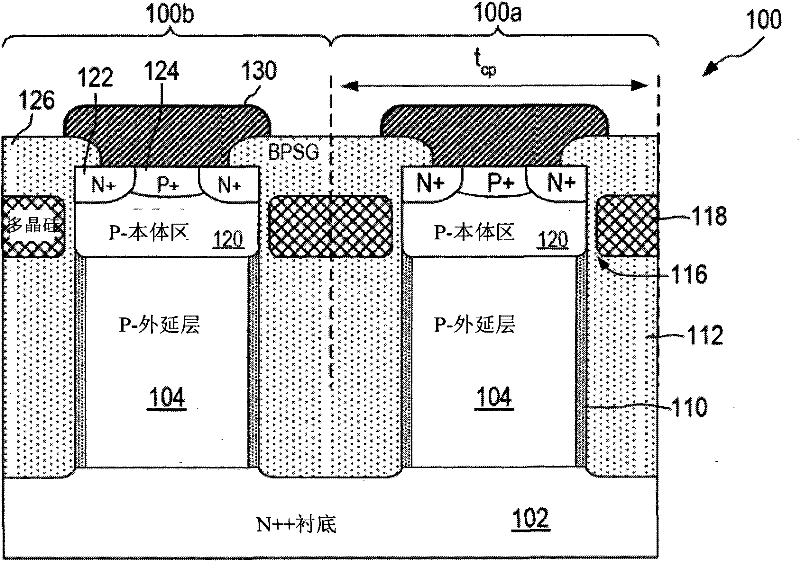

[0081] figure 1 It shows a cross-sectional view of a vertical channel metal oxide silicon field effect transistor device according to a first embodiment of the present invention. see figure 1 , an N-type vertical channel MOSFET device ("NMOS transistor") 100, formed in an array of parallel transistor cells 101a and 101b. A certain number of transistor cells are used to form an array to obtain an NMOS transistor 100 with certain breakdown voltage and Rdson (drain-source "on" resistance) characteristics. Transistor arrays can be one-dimensional or two-dimensional arrays, depending primarily on the number of transistor cells included. For example, a striped unit cell structure can use a one-dimensional array, and a hexagonal unit cell structure can use a two-dimensional array, as described in further detail below.

[0082] The NMOS transistor 100 is formed on an N++ substrate 102 with a relatively high doping concentration. The N++ substrate 102 serves as the drain electrode ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More