Method and structure for reducing grid resistance of power MOSFET (metal oxide semiconductor field-effect transistor)

A power field effect and gate resistance technology, applied in circuits, electrical components, semiconductor devices, etc., can solve problems such as the inability to greatly reduce gate resistance, achieve performance improvement, fast response speed, and reduce gate resistance Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

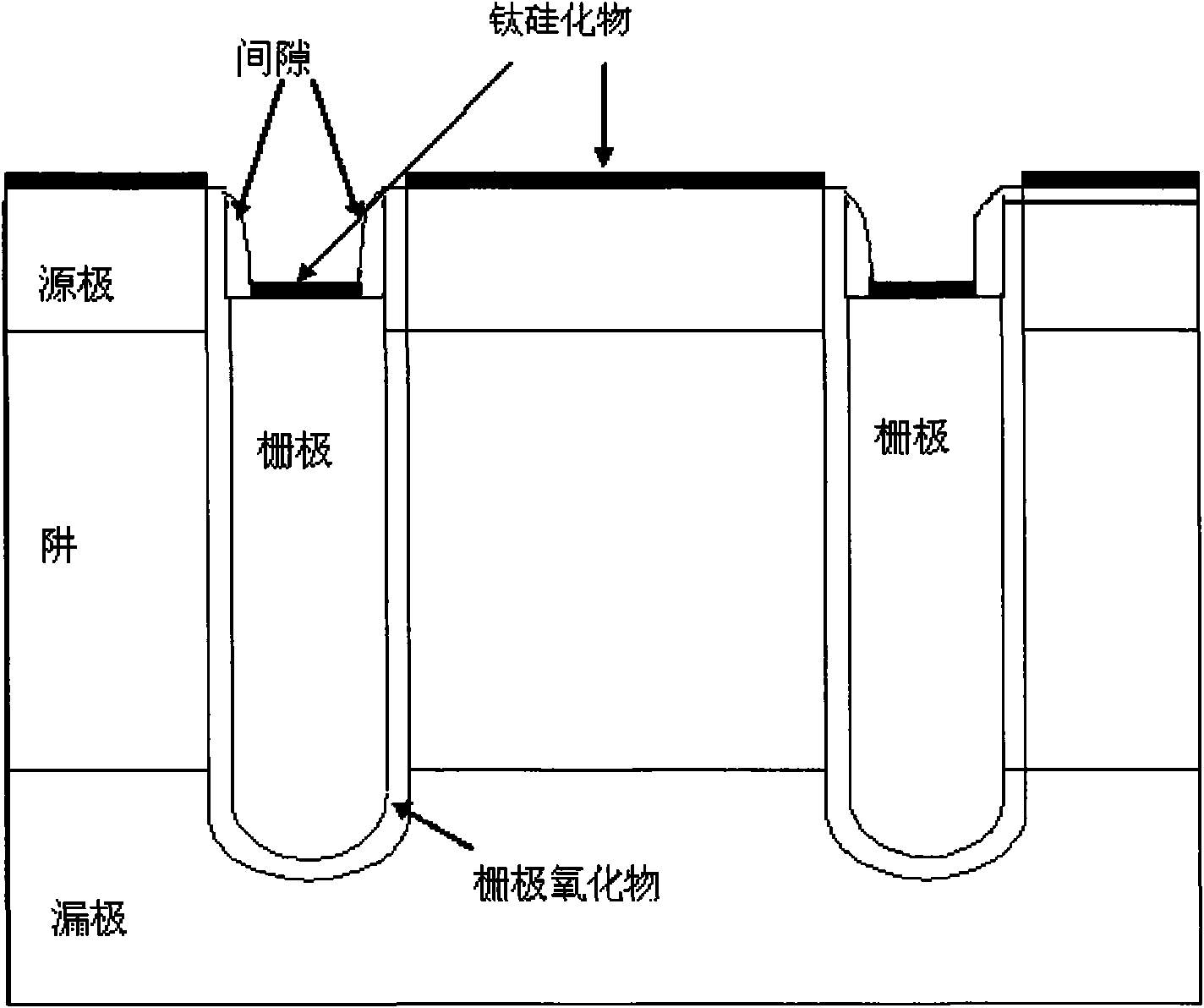

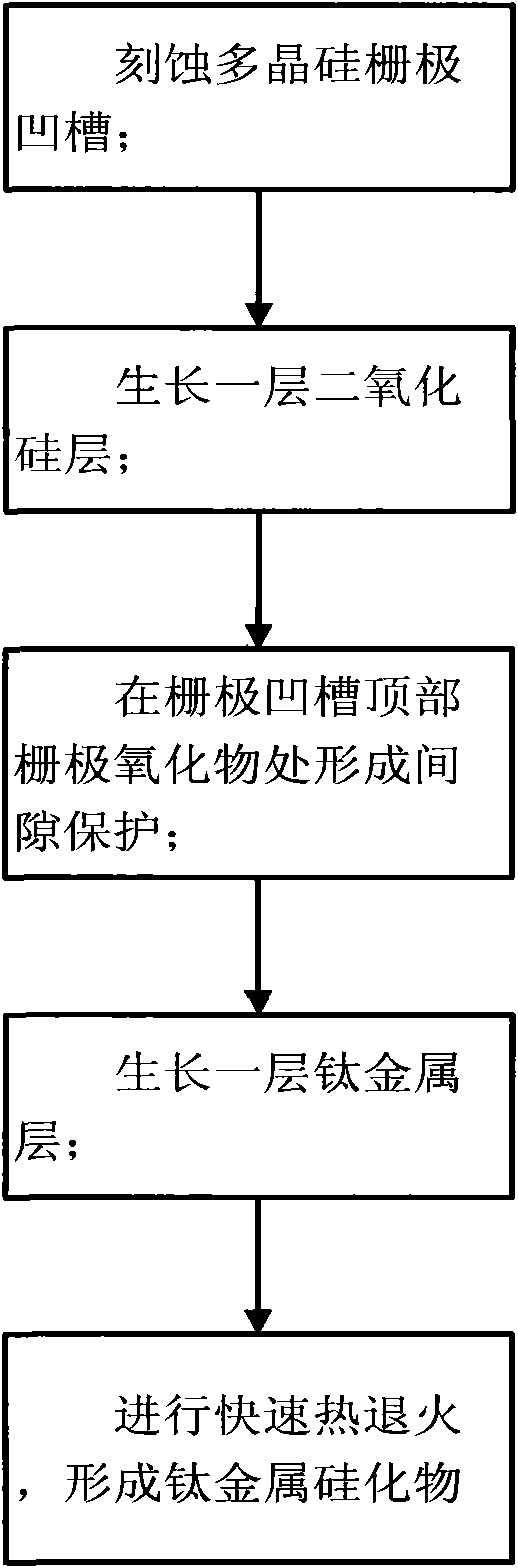

[0016] The method for reducing the gate resistance of a power field effect transistor according to the present invention; comprises the following steps:

[0017] Step 1. When etching the gate polysilicon, carve out grooves deeper than ordinary power field effect transistors. The depth of the grooves is about 1500-3000 angstroms; Source) ion implantation is performed before; then well (Well) ion implantation and source (Source) ion implantation are performed according to the normal process.

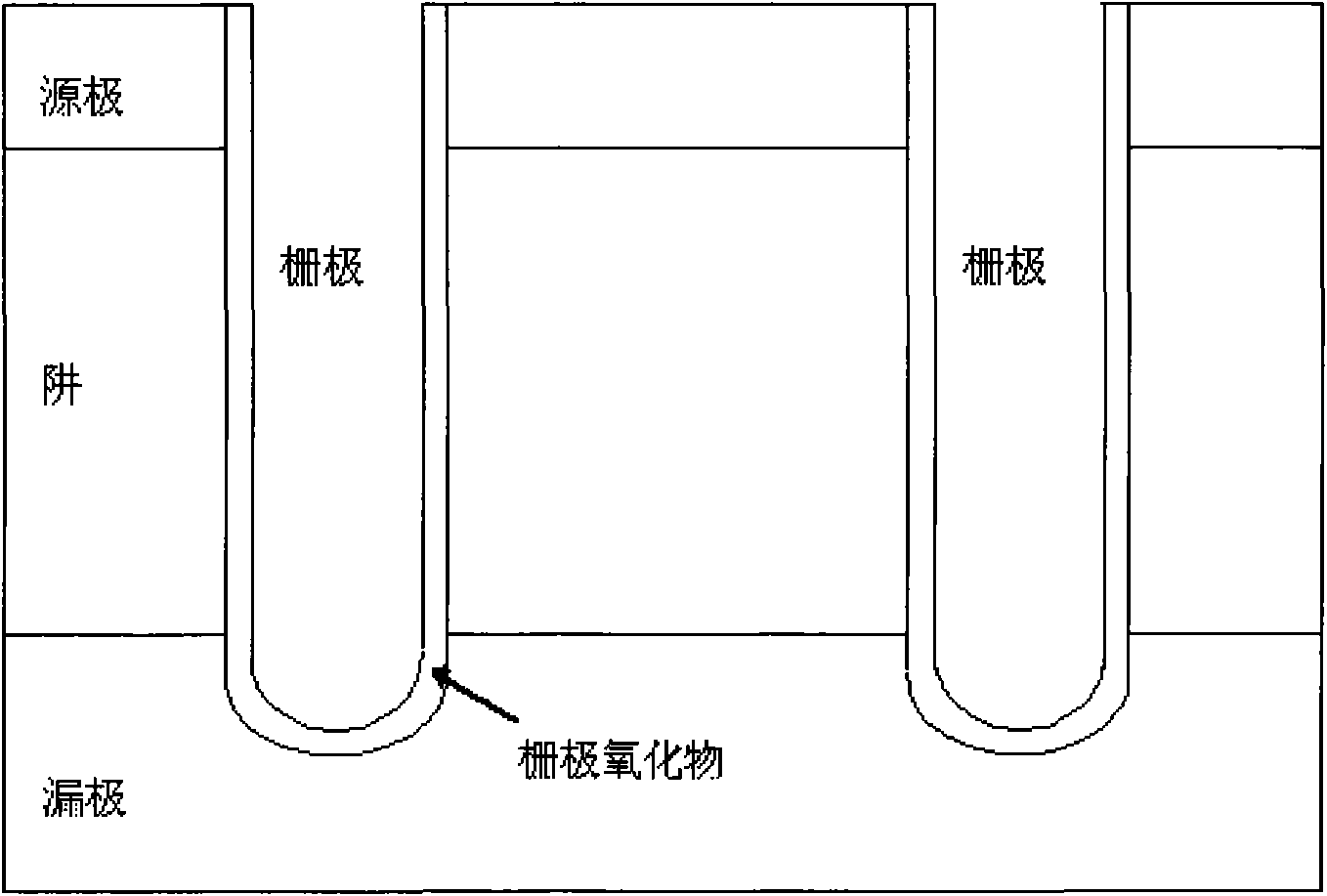

[0018] Compared with the currently known polysilicon gate groove, the structure is basically the same, but the polysilicon gate groove of the present invention is deeper than the polysilicon gate groove of the currently known power MOS device, and this is done to reserve some space Give the titanium metal silicide to be formed below.

[0019] Step 2: After the Well ion implantation and the Source ion implantation are completed as described in Step 1, a layer of silicon dioxide with a cert...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More