First-coating last-etching single package method for positively packaging double-sided graphic chip

A graphics chip and packaging method technology, which is applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve the problems of large volume and area, slow signal output speed of the chip, and high cost of metal wires, and achieve volume and Effects of reduced area, shorter length, and lower cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0110] Example 1: Single Base Island Single Turn Pin

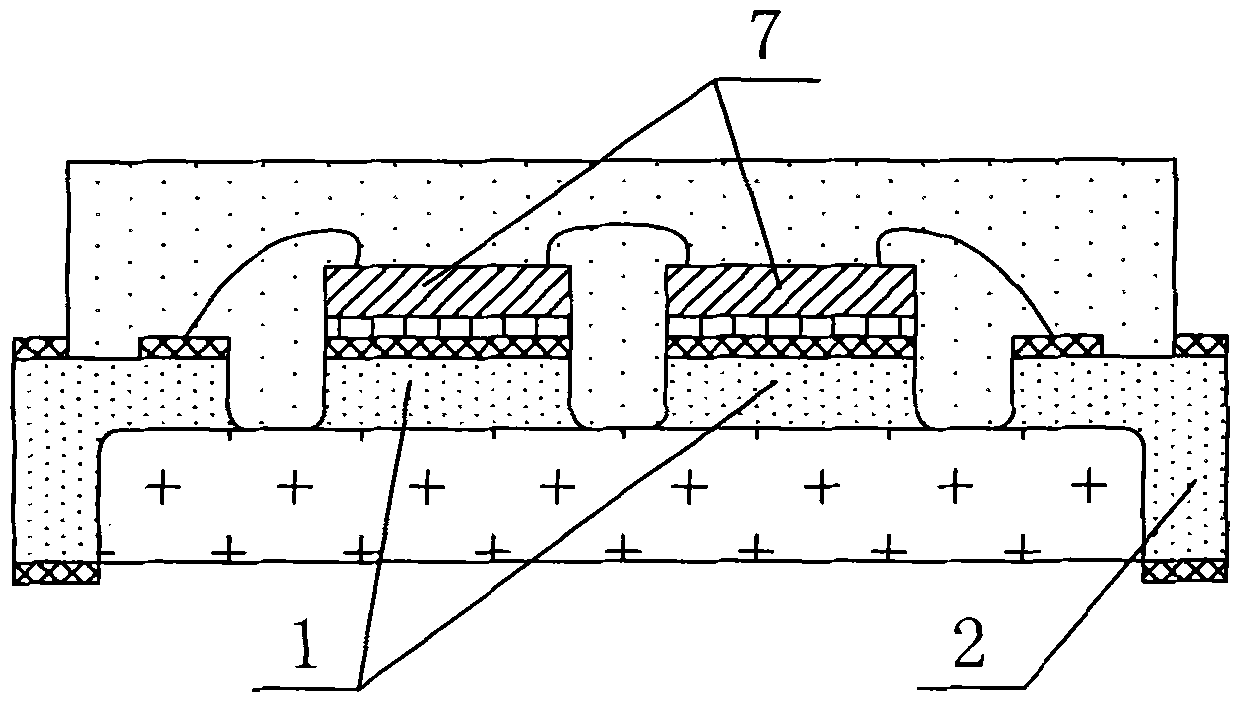

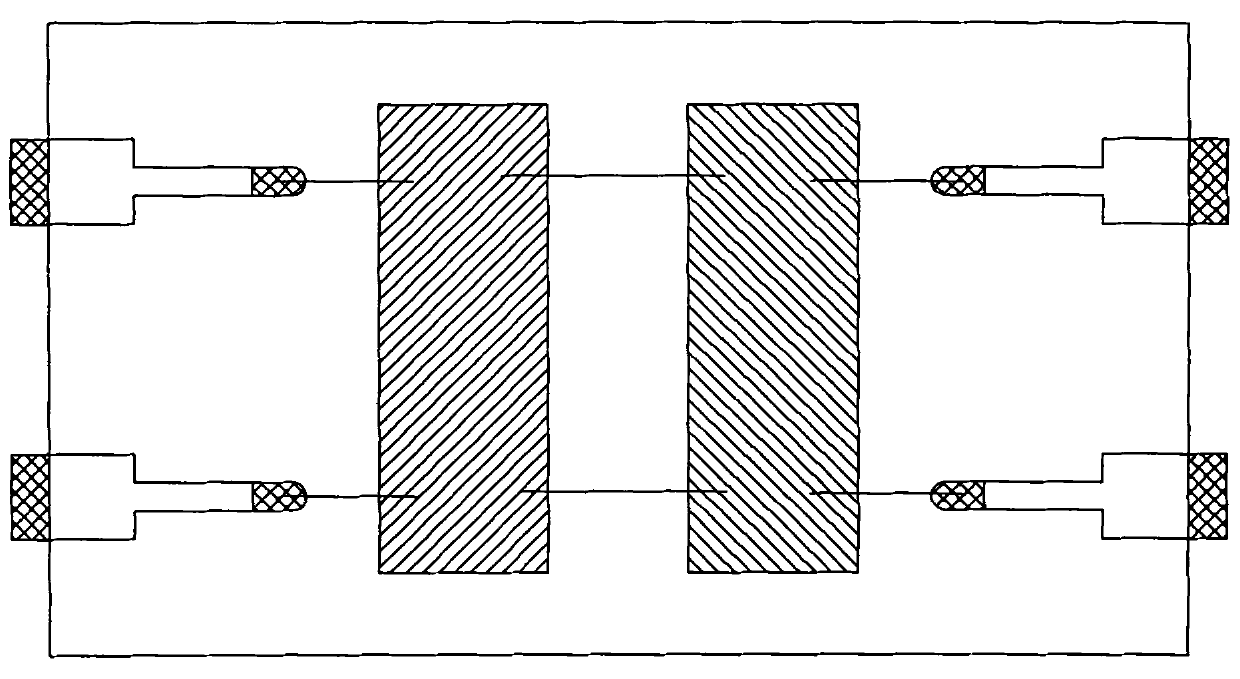

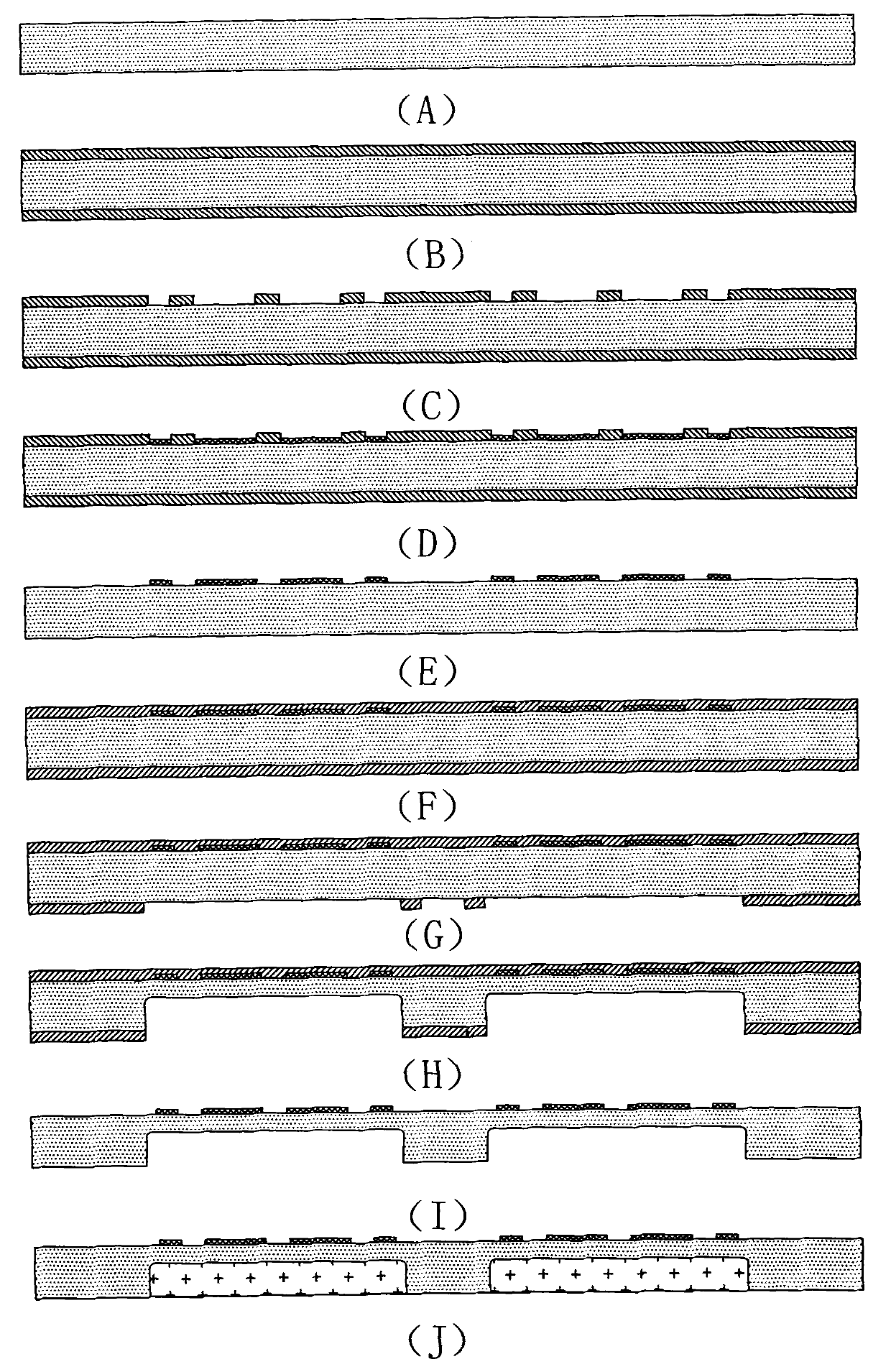

[0111] see figure 2 and image 3 , figure 2 It is a structural schematic diagram of Embodiment 1 of the double-sided graphics chip front-mounted single-chip package structure of the present invention. image 3 for figure 2 top view. Depend on figure 2 and image 3 It can be seen that the double-sided graphic chip of the present invention is mounted on a single package structure, including base island 1, pin 2, plastic encapsulant (epoxy resin) 3 without filler, conductive or non-conductive bonding material 6, chip 7, metal line 8 and filler molding compound (epoxy resin) 9, the front of the pin 2 extends as far as possible to the side of the base island 1, and a first metal layer 4 is arranged on the front of the base island 1 and the pin 2, A second metal layer 5 is arranged on the back side of the base island 1 and pins 2, and a chip 7 is arranged on the first metal layer 4 on the front side of the base island...

Embodiment 2

[0151] Embodiment 2: sunken base island exposed type single-turn pin

[0152] see Figure 4~6 , Figure 4 (A)~ Figure 4 (R) is a schematic diagram of each process in Embodiment 2 of the double-sided graphics chip packaging method of the present invention, which is first plated and then engraved. Figure 5 It is a structural schematic diagram of Embodiment 2 of the double-sided graphics chip front-mounted single-chip package structure of the present invention. Figure 6 for Figure 5 top view. Depend on Figure 4 , Figure 5 and Figure 6 It can be seen that the only difference between Embodiment 2 and Embodiment 1 is that the base island 1 is a sunken base island, that is, the central area of the front of the base island 1 is sunken.

Embodiment 3

[0153] Embodiment 3: Embedded base island single-turn pin

[0154] see Figure 7-9 , Figure 7 (A)~ Figure 7 (R) is a schematic diagram of each process in Embodiment 3 of the double-sided graphics chip packaging method of the present invention, which is first plated and then engraved. Figure 8 It is a structural schematic diagram of Embodiment 3 of the double-sided graphics chip front-mounted single-chip package structure of the present invention. Figure 9 for Figure 8 top view. Depend on Figure 7 , Figure 8 and Figure 9 It can be seen that the difference between Example 3 and Example 1 is that the base island 1 is an embedded base island, that is, the back of the base island 1 is embedded with the filler-free molding compound (epoxy resin) 3 Inside.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More