Method for constructing floating gate

A floating gate and wafer technology, applied in the direction of semiconductor devices, etc., can solve problems such as FG short circuit and device failure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

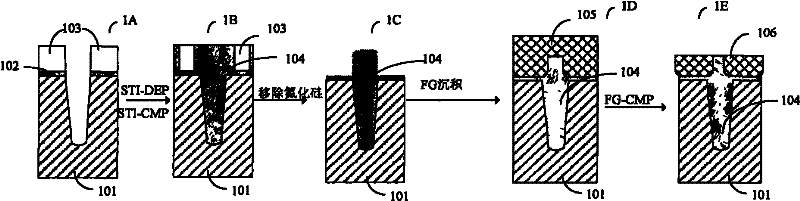

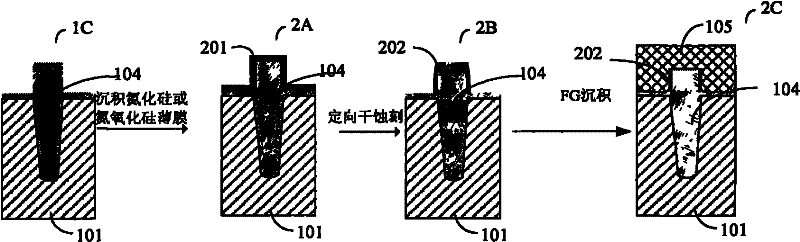

[0029] The inventors analyzed the existing FG construction process and found that the following factors may cause the distance between adjacent FGs to be too small:

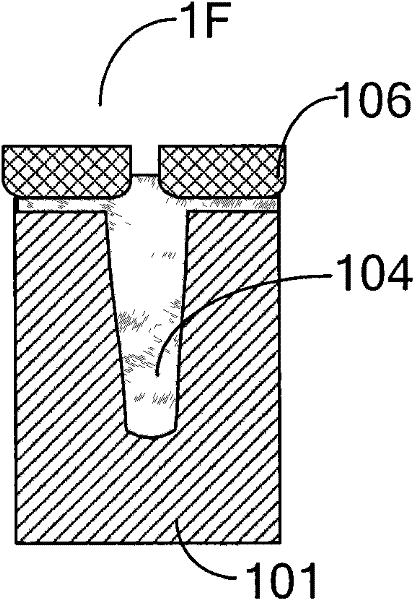

[0030] The process of removing silicon nitride is a wet etching process. In addition to removing silicon nitride 103, this process also has a corrosion effect on the silicon oxide filled in the STI, so that the volume of vacancies formed by the removed silicon nitride increases. . The subsequent two-step hydrofluoric acid pre-cleaning process further depleted the filled silicon oxide, and the width of the filled silicon oxide between the vacancies was reduced. From figure 1 This trend can be clearly seen from Section 1B to Section 1C in the figure. In this way, in the subsequent step of depositing polysilicon, the volume of polysilicon deposited in the vacancies is significantly larger than the volume of the original silicon nitride, and the width of the FG formed on this basis will also be too large, resultin...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More