Manufacturing method of coreless layer capsulation substrate

A technology for encapsulating substrates and non-nuclear layers, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., and can solve the problem of smaller bonding area between solder and surface treatment layer 19 and poor reliability of the overall packaging substrate , Packaging substrates are not easy to separate, etc., to shorten the signal transmission path, avoid poor developing effects, and reduce warping

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

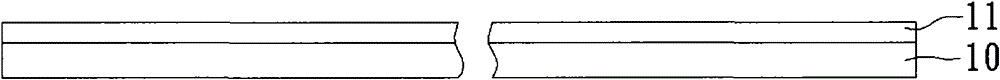

[0063] Please refer to Figure 2A and 2A’ ,in Figure 2A It is a cross-sectional view of the carrier plate used for the non-nuclear layer packaging substrate of the present invention, in addition Figure 2A' for Figure 2A The upper perspective view of the release film 22 and the first dielectric layer 21 in the carrier board.

[0064] like Figure 2A As shown, a core layer 20 is provided, and the core layer 20 can be, for example, a copper foil substrate, but the present invention is not limited thereto. Then, a first dielectric layer 21 , a release film 22 , and a metal layer 23 are sequentially formed on the surface of the core layer 20 . Depend on Figure 2A' As shown, it can be found that the area of the release film 22 is smaller than that of the first dielectric layer 21, and the first dielectric layer 21 has a frame-shaped region 21a not covered by the release film 22, so the first dielectric layer 21 and the metal layer The overlapping portion of 23 is the fr...

Embodiment 2

[0068] Please refer to Figure 2A to Figure 2G , which is a cross-sectional view of the manufacturing process of the non-nuclear layer packaging substrate of the present invention, which is used to manufacture bump pads embedded and exposed on the non-nuclear layer packaging substrate.

[0069] First, if Figure 2A As shown, a carrier board 2 is provided, and the carrier board 2 is the carrier board used to manufacture the core-free layer packaging substrate in the first embodiment.

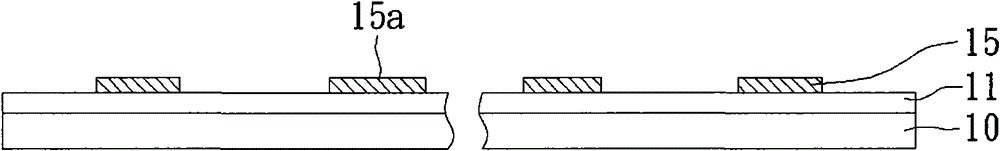

[0070] Next, if Figure 2B As shown, on the metal layer 23 and the core layer 20 of the carrier board 2, a resistance layer 24 is pressed. This resistance layer 24 is mainly pressed on the surface of the metal layer 23, and exceeds the periphery of the metal layer 23. The opening area 244 exposes part of the surface of the metal layer 23 through the exposure and development patterning process. Next, in the opening area 244, for example, use electroplating to form a first circuit layer 25, and ...

Embodiment 3

[0077] The preparation method of this embodiment is substantially the same as that of Embodiment 2, and the differences are described in detail as follows.

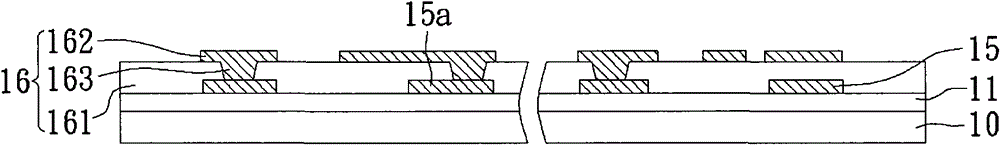

[0078] like Figure 2E' As shown, on the surface of the second dielectric layer 261 on the outermost layer of the build-up structure 26, the second circuit layer 262 not only has a plurality of second electrical contact pads 262a, but also has a circuit 262b, and is formed on the surface of the build-up structure 26 An insulating protective layer 27, the insulating protective layer 27 can be, for example, a solder resist layer using green paint, or using dielectric materials commonly used in this field. Wherein, according to the material of the insulating protection layer 27, a plurality of openings 274 can be formed on the insulating protection layer 27 by means of exposure and development or laser ablation (laser ablation), so as to expose the second circuit layer 262 of the outermost layer. Two electrical contact pads...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More