Hybrid latch applied to multi-power supply system on chip

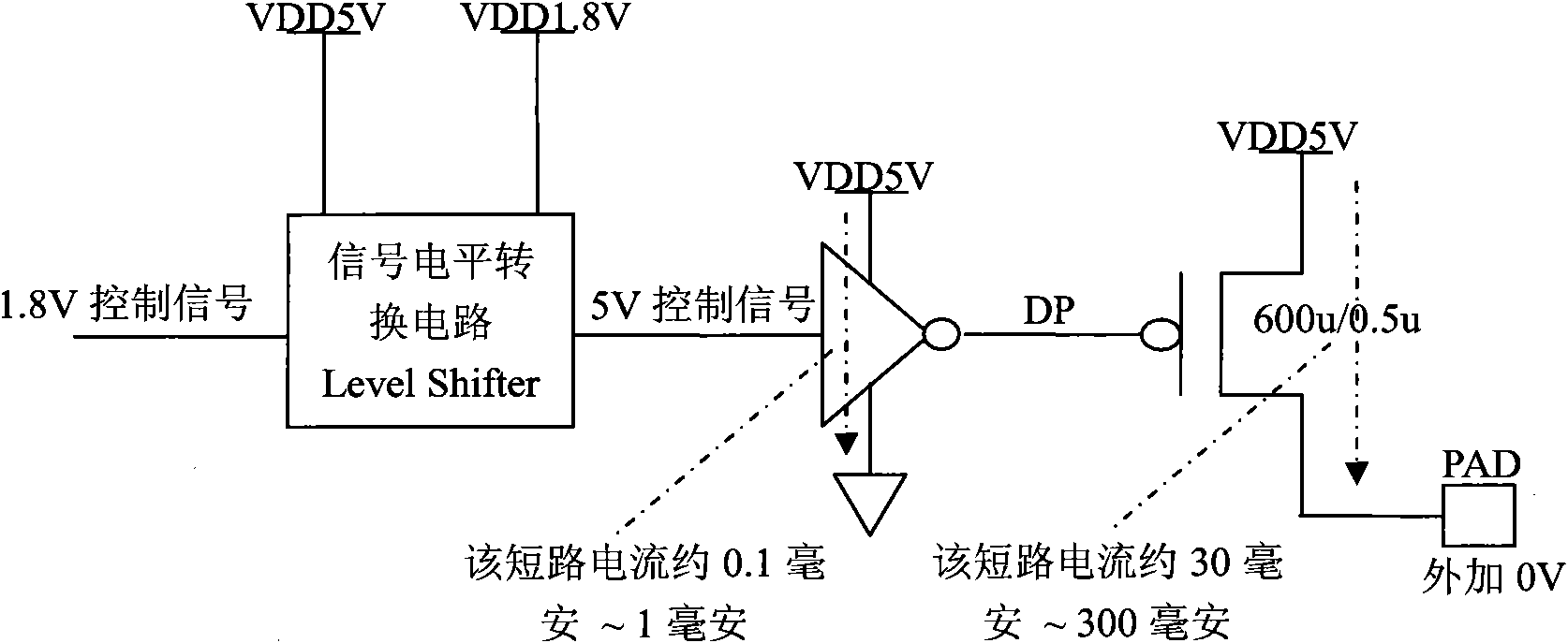

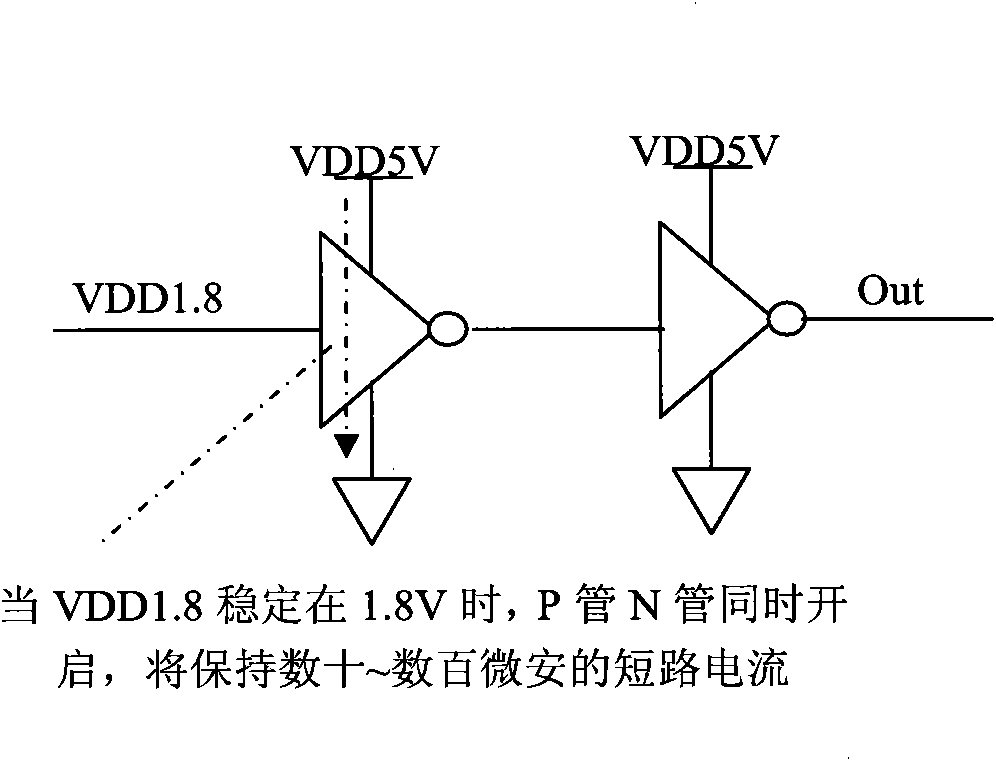

A system-on-chip, hybrid technology, applied in electrical components, output power conversion devices, etc., can solve problems such as limiting the standby time of handheld devices, inverter short-circuit current, etc., to reduce battery consumption and suppress short-circuit current.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

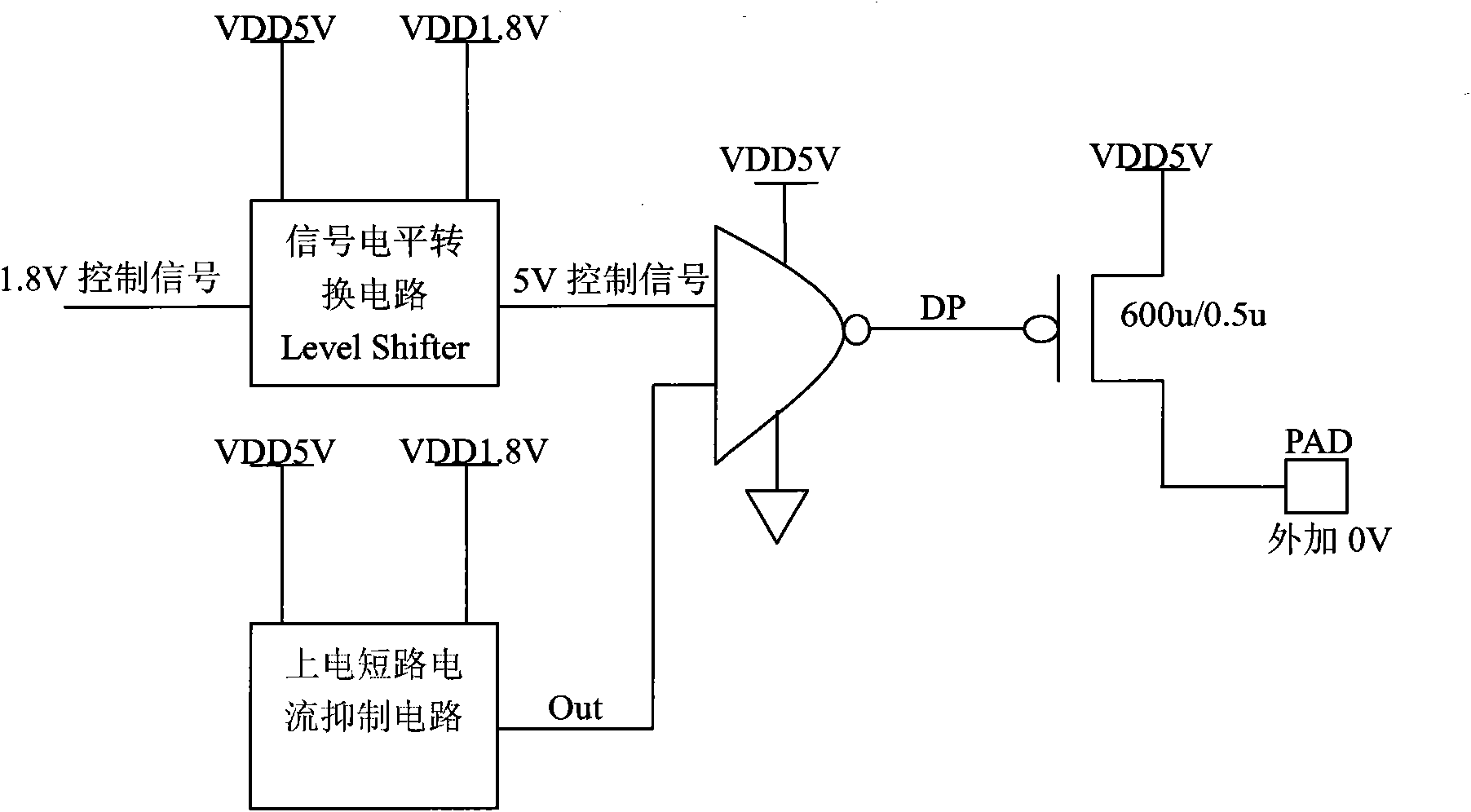

[0023] Such as Figure 4 As shown, it is a hybrid latch applied to a system-on-chip with multiple power supplies according to the present invention. The multi-power supply system-on-a-chip refers to a system in which the main power supply and multiple sub-power supplies are integrated on one working chip for collaborative power supply. The working chip includes multiple working circuits, and some working circuits will generate short-circuit current when the sub-power supplies are not stable. In this embodiment, the total power supply is a 5V power supply, and the sub-power supply is a 1.8V power supply, and the sub-power supplies are generated by a power generation circuit using the total power supply as a source. The input terminal of the hybrid latch is connected to the main power supply and the sub-power supply, and the output terminal is connected to the part of the working circuit of the working chip that will generate a short-circuit current when the sub-power supply is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More