Method for realizing sub-10nm gate length line

A technology of grid length and line, applied in the field of defining fine grid line graphics, can solve the problem of large process window, etc., and achieve the effect of large process window, good controllability and repeatability, and simple process flow

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

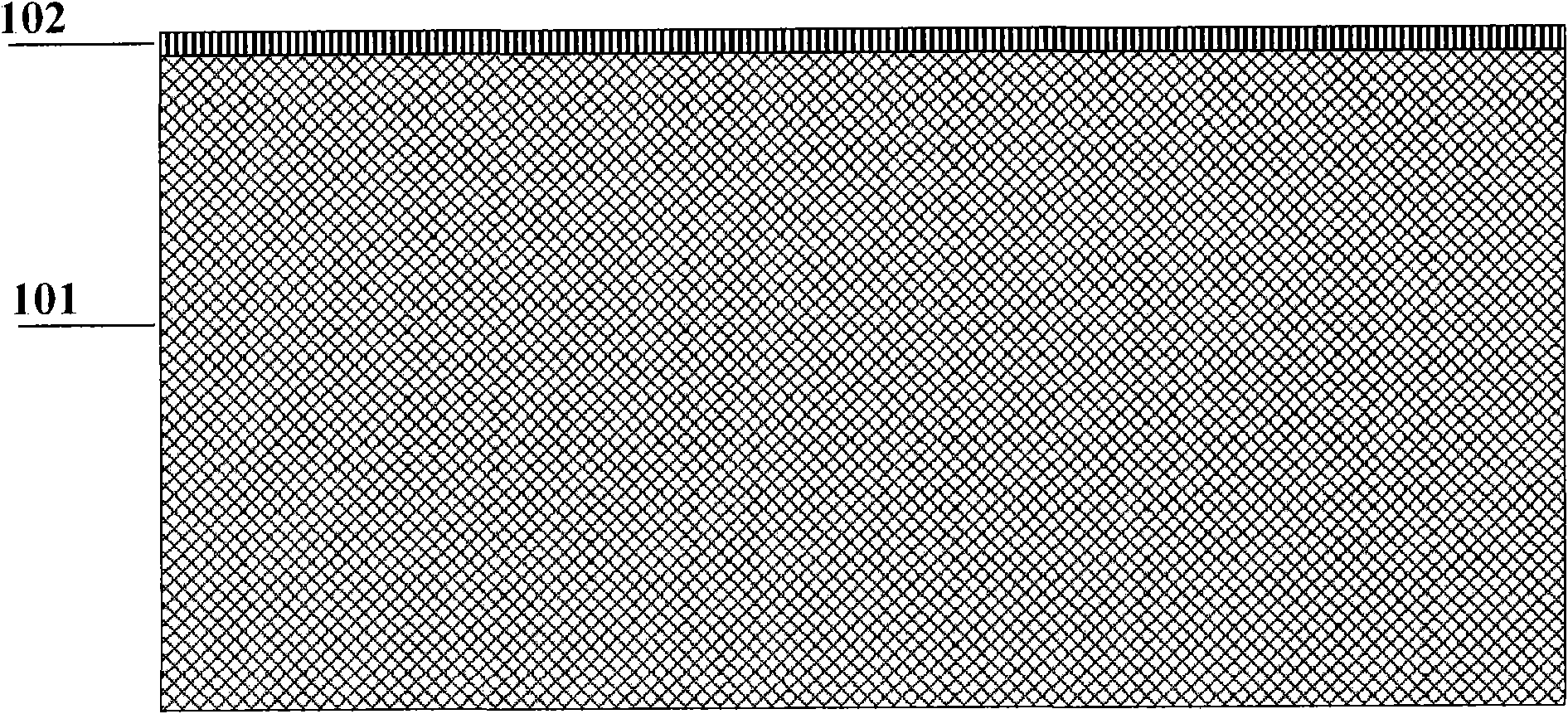

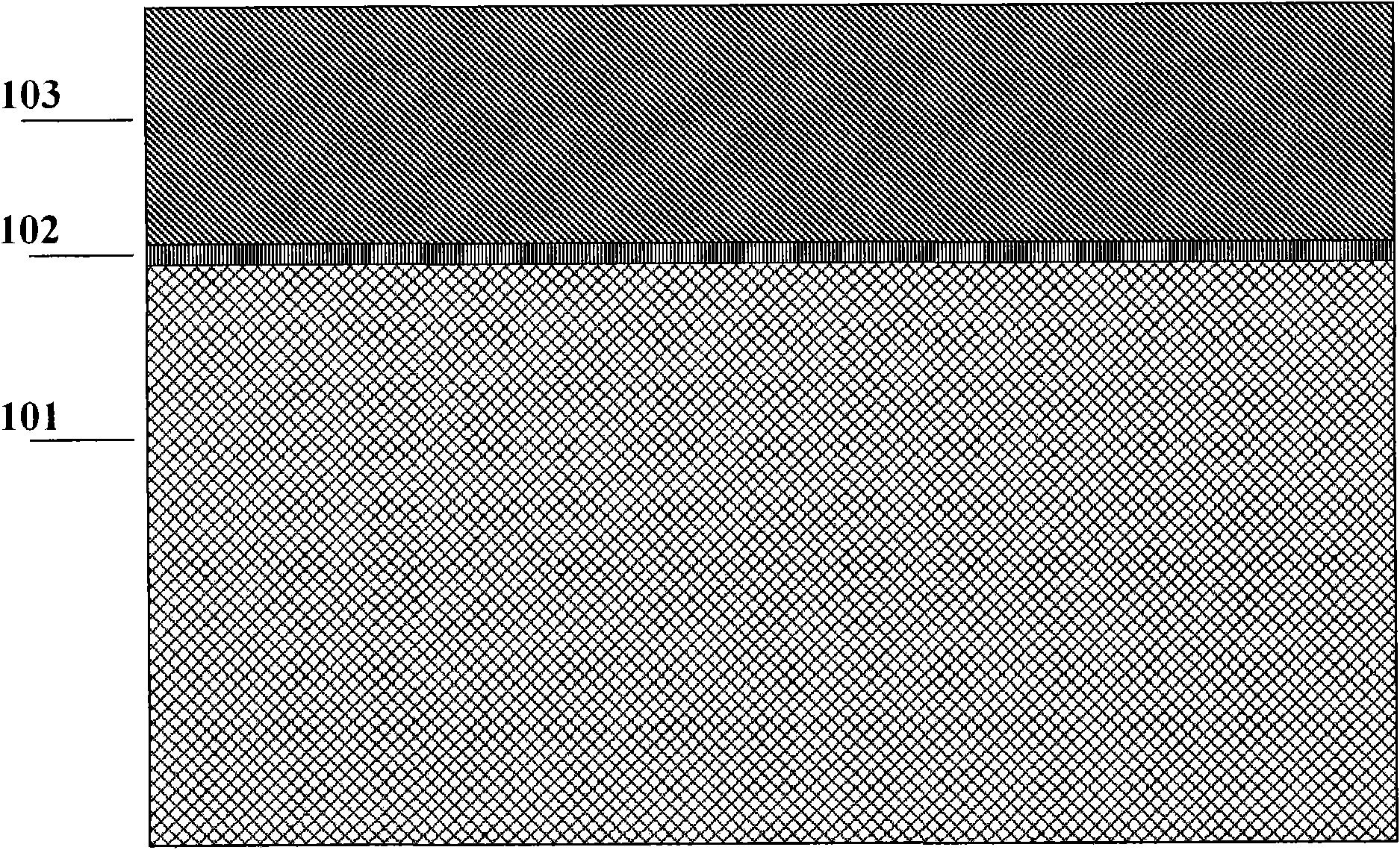

[0033] 1) if Figure 1a As shown, at 950 °C, thermal oxidation growth of SiO 2 thickness of (102);

[0034] 2) if Figure 1b As shown, the low pressure chemical vapor deposition polysilicon (103);

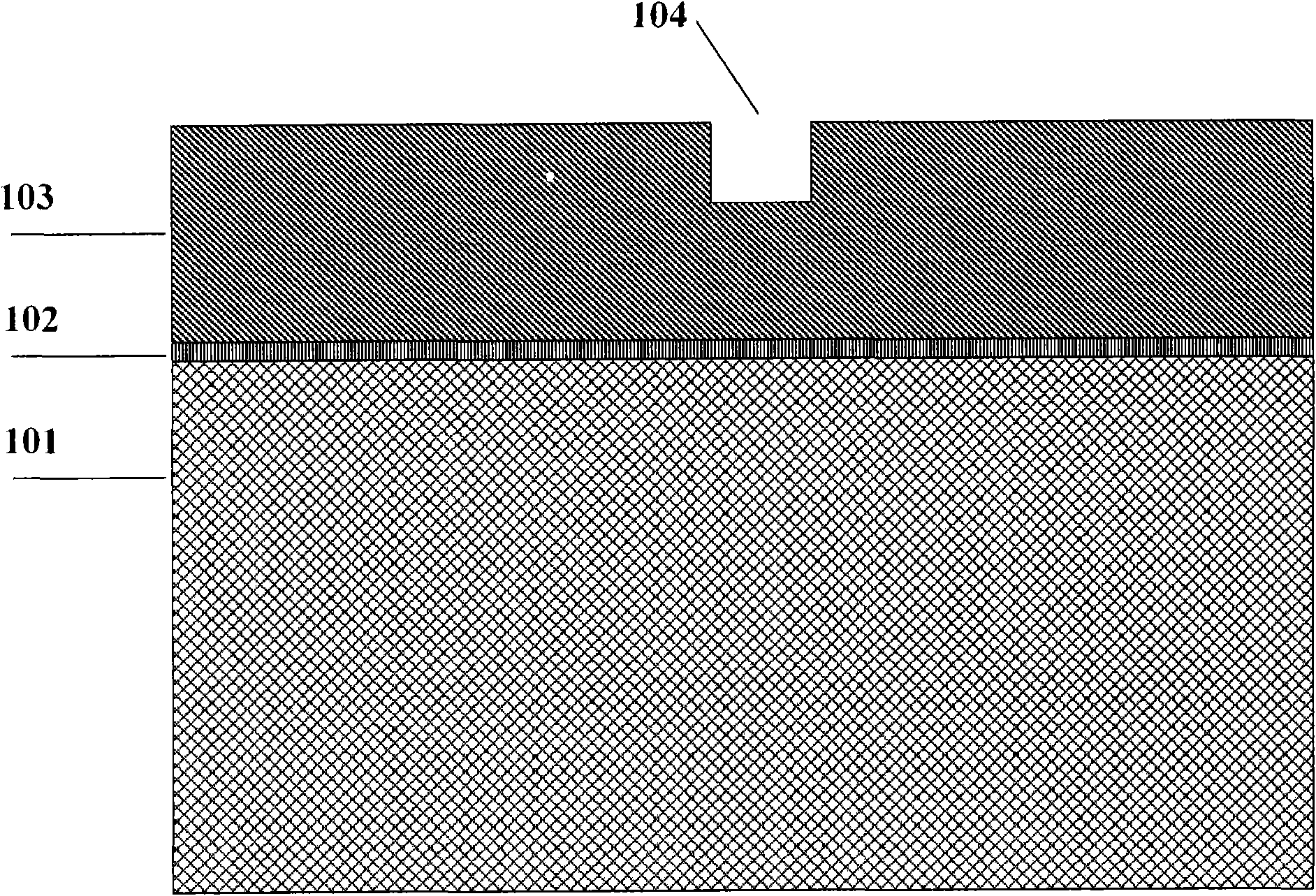

[0035] 3) if Figure 1c Shown, using positive electron beam photoresist ZEP520 exposure. The steep grooves (104) are etched using chlorine-based reactive ions. The etched groove has a width of 100nm and a depth of 10nm;

[0036] 4) Chemical vapor deposition oxide dielectric layer LTO (105), with a thickness of 30nm;

[0037] 5) if Figure 1d As shown, the surface of the oxide dielectric layer is planarized (105) by chemical mechanical sectioning.

[0038] 6) If Figure 1e As shown, a positive electron beam photoresist ZEP520 is used to expose two grooves ( 107 ) with a defined pitch of 80 nm. The steep grooves are etched using fluorine-based reactive ions. The etched groove has a width of 100 nm and a depth of 10 nm.

[0039] 7) if Figure 1f As shown, the oxide la...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width | aaaaa | aaaaa |

| Depth | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com