Embedded system on programmable chip (SOPC) having image coprocessor

An embedded system and coprocessor technology, applied in the field of embedded programmable system-on-chip, can solve problems such as insufficient CPU computing power

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

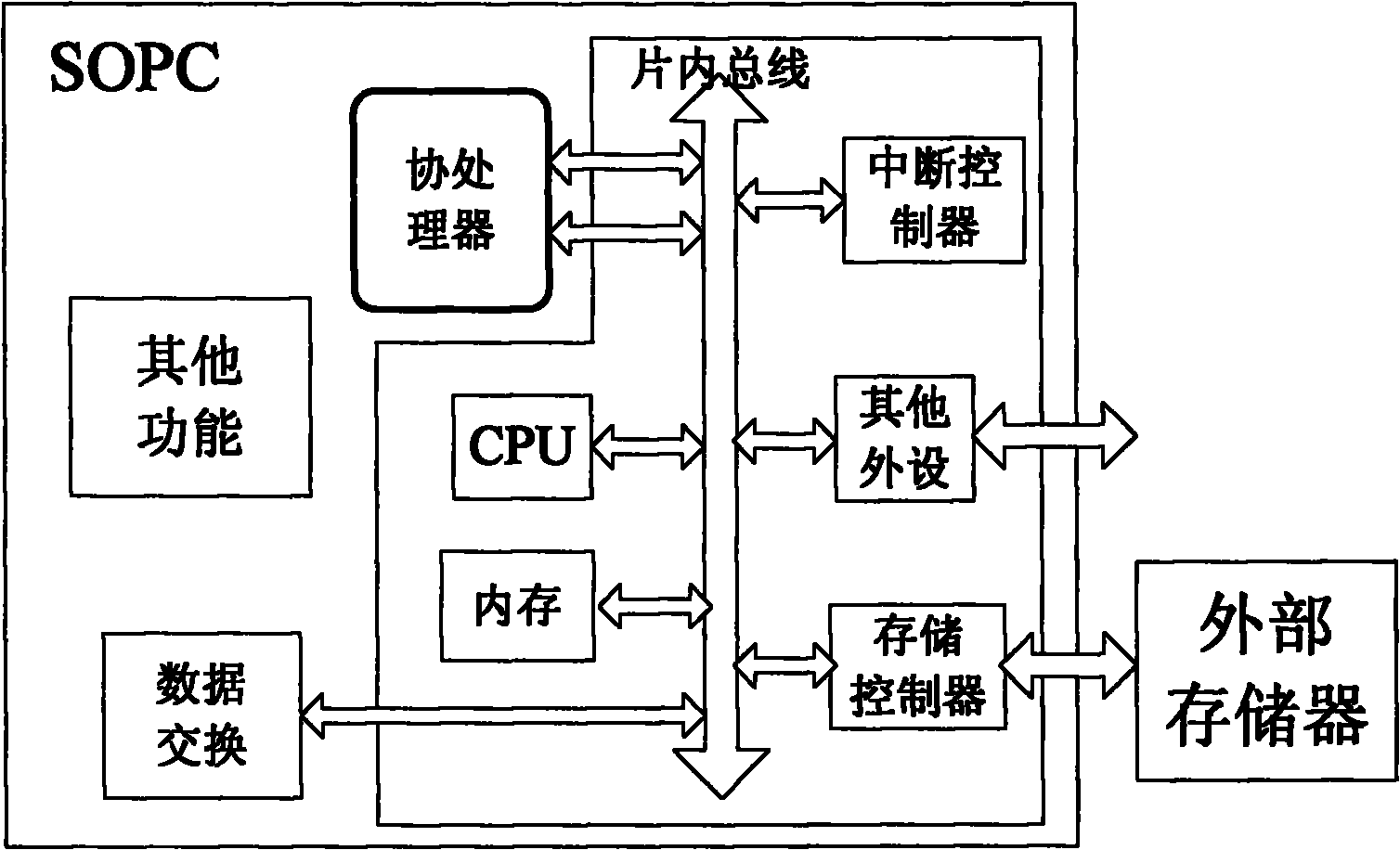

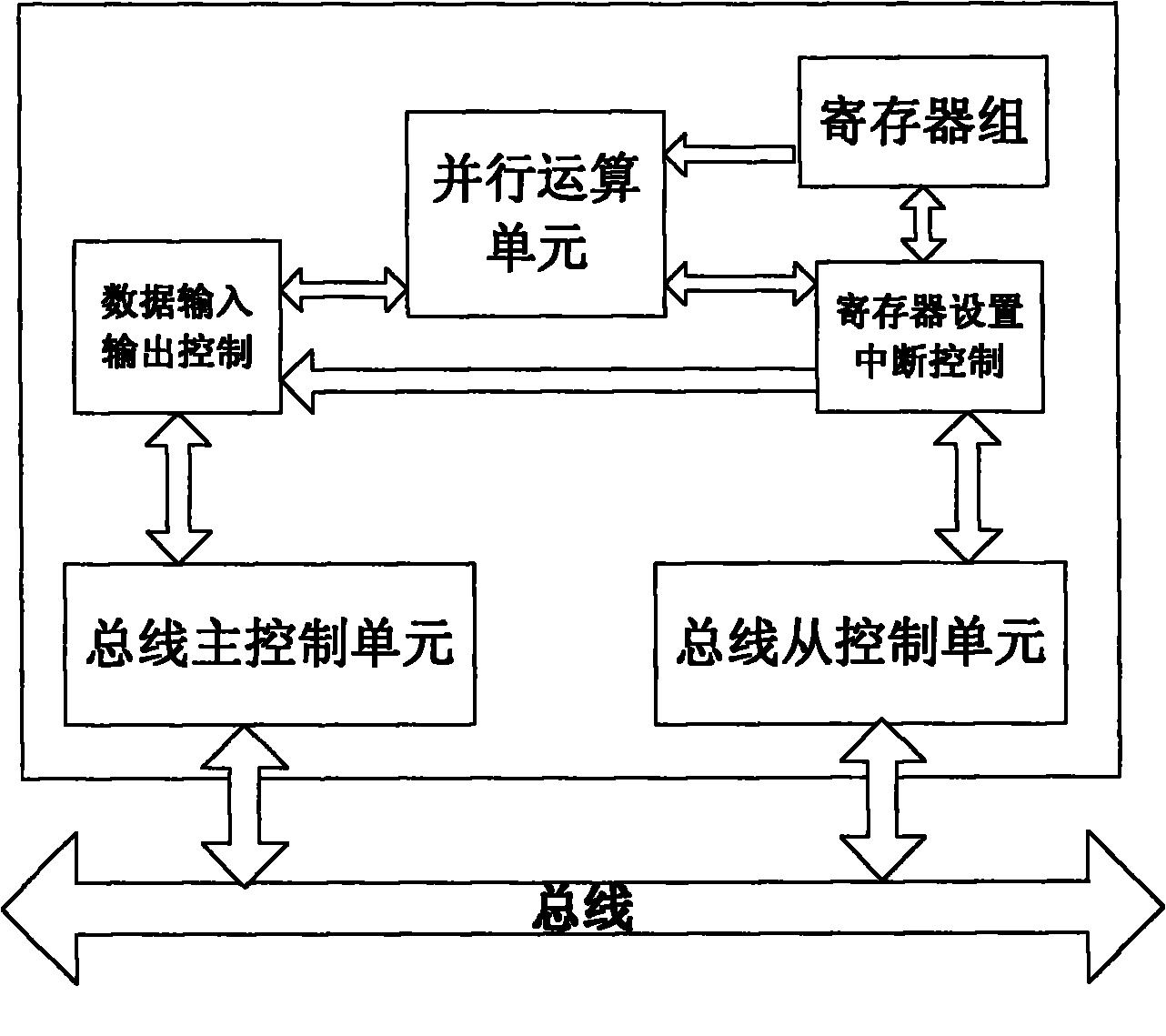

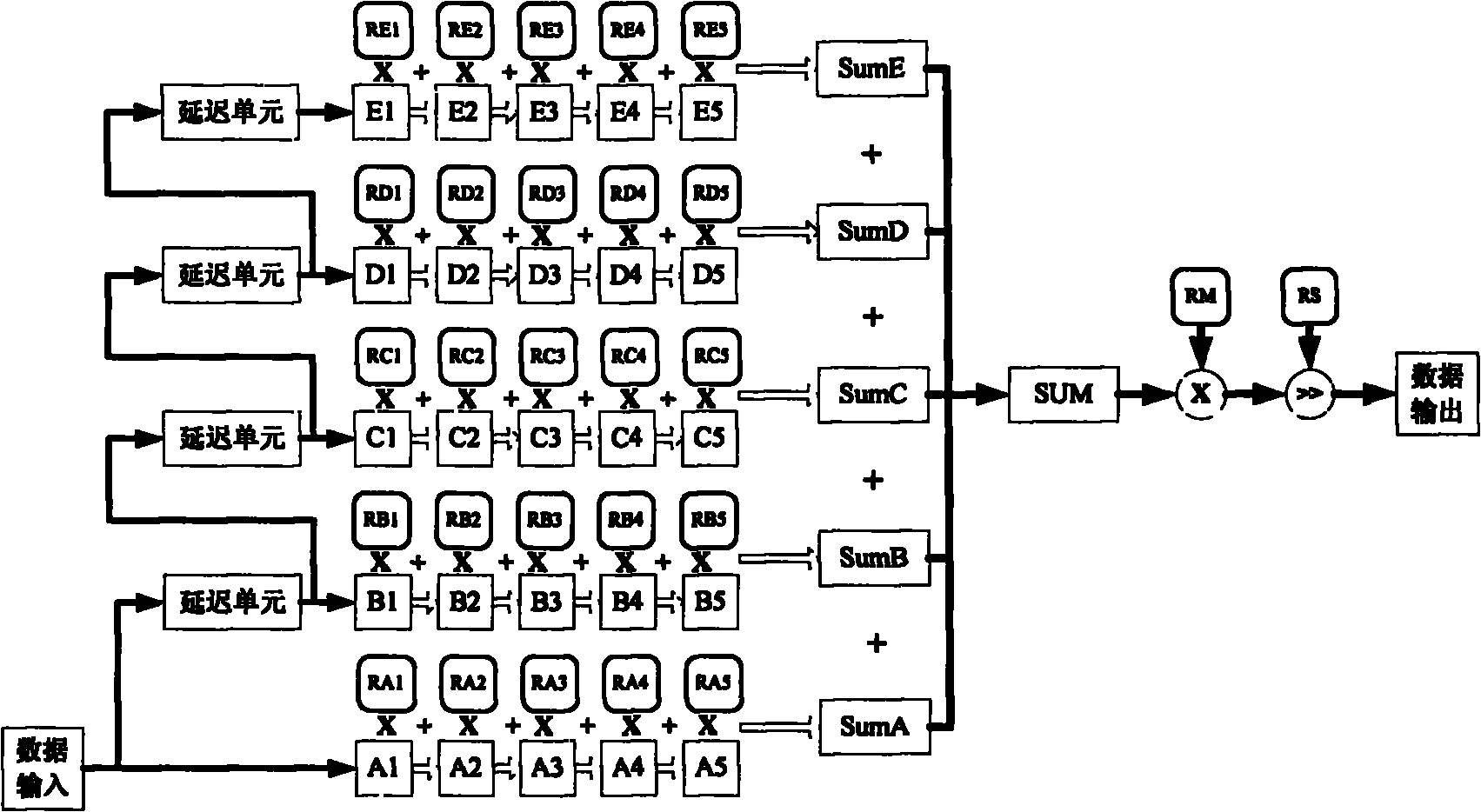

[0022] An example of the present invention is as follows:

[0023] On the self-developed SOPC signal processing platform, Gaussian smoothing and filtering operations are performed on multi-frame images. The platform chooses the FPGA of XC5VFX20T-FF323 model of Xilinx Company, and uses the development software provided by the company to design an embedded platform inside the FPGA. In this design, Microblaze is selected as the CPU of the embedded system, and the clock frequency is 125MHz; the PLB4.6 bus is selected as the system bus, the clock frequency is 125MHz, and the width is 64 bits. The sum of the throughput rates, so that the two are not affected by the transmission rate. Select DDR2_SDRAM_256MB as the off-chip memory of the system, and map to the memory space whose address range is 0x80000000-0x90000000. After the above-mentioned design is completed, the coprocessor is connected to the PLB bus, and the clock selects the bus clock 125MHz. The image data selects 1080P ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More