III-V family semiconductor MOS (Metal Oxide Semiconductor) interface structure

A III-V, interface structure technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of high interface state density and channel carrier mobility, and achieve reduced scattering, high mobility and high Electron concentration, effect of reducing interface state density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

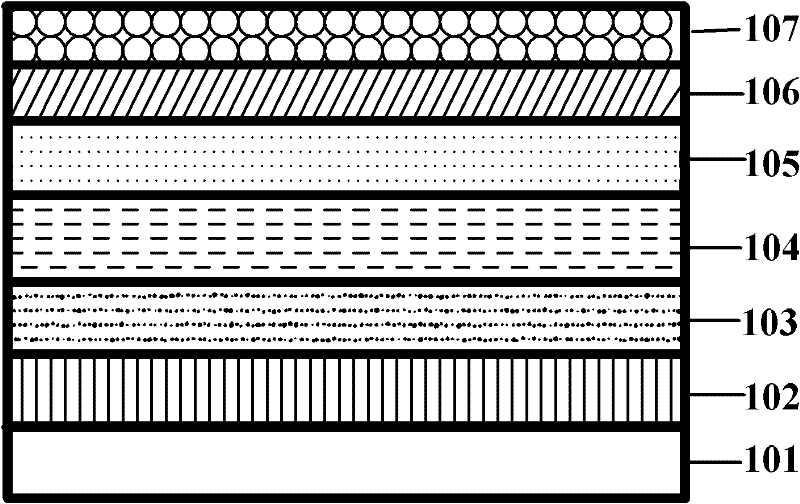

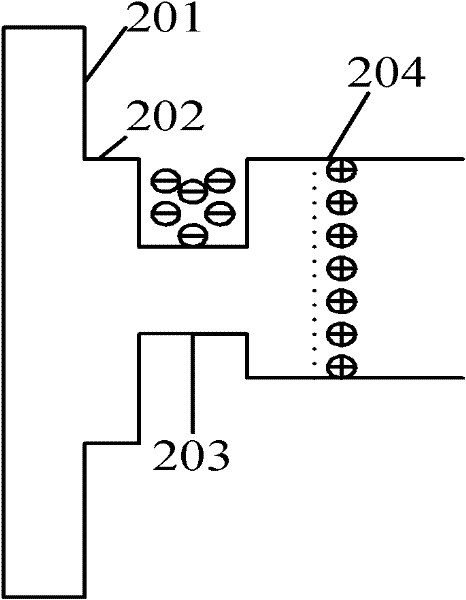

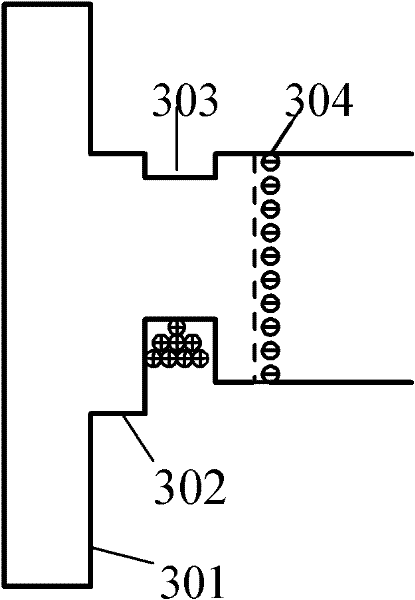

[0032] Such as figure 1 as shown, figure 1 It is a schematic diagram of the III-V semiconductor MOS interface structure provided by the present invention. The III-V semiconductor MOS interface structure uses gallium phosphide as the interface control layer, and specifically includes: a single crystal substrate 101 on the single crystal substrate 101 The buffer layer 102 formed on the surface, the quantum well bottom barrier layer 103 formed on the buffer layer 102, the high mobility quantum well channel 104 formed on the quantum well bottom barrier layer 103, the high mobility quantum well channel GaP interface control layer 105 formed on GaP interface control layer 104 , high-K gate dielectric 106 formed on GaP interfac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More