Patents

Literature

84 results about "Gallium phosphide" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Gallium phosphide (GaP), a phosphide of gallium, is a compound semiconductor material with an indirect band gap of 2.24 eV at room temperature. Impure polycrystalline material has the appearance of pale orange or grayish pieces. Undoped single crystals are orange, but strongly doped wafers appear darker due to free-carrier absorption. It is odorless and insoluble in water.

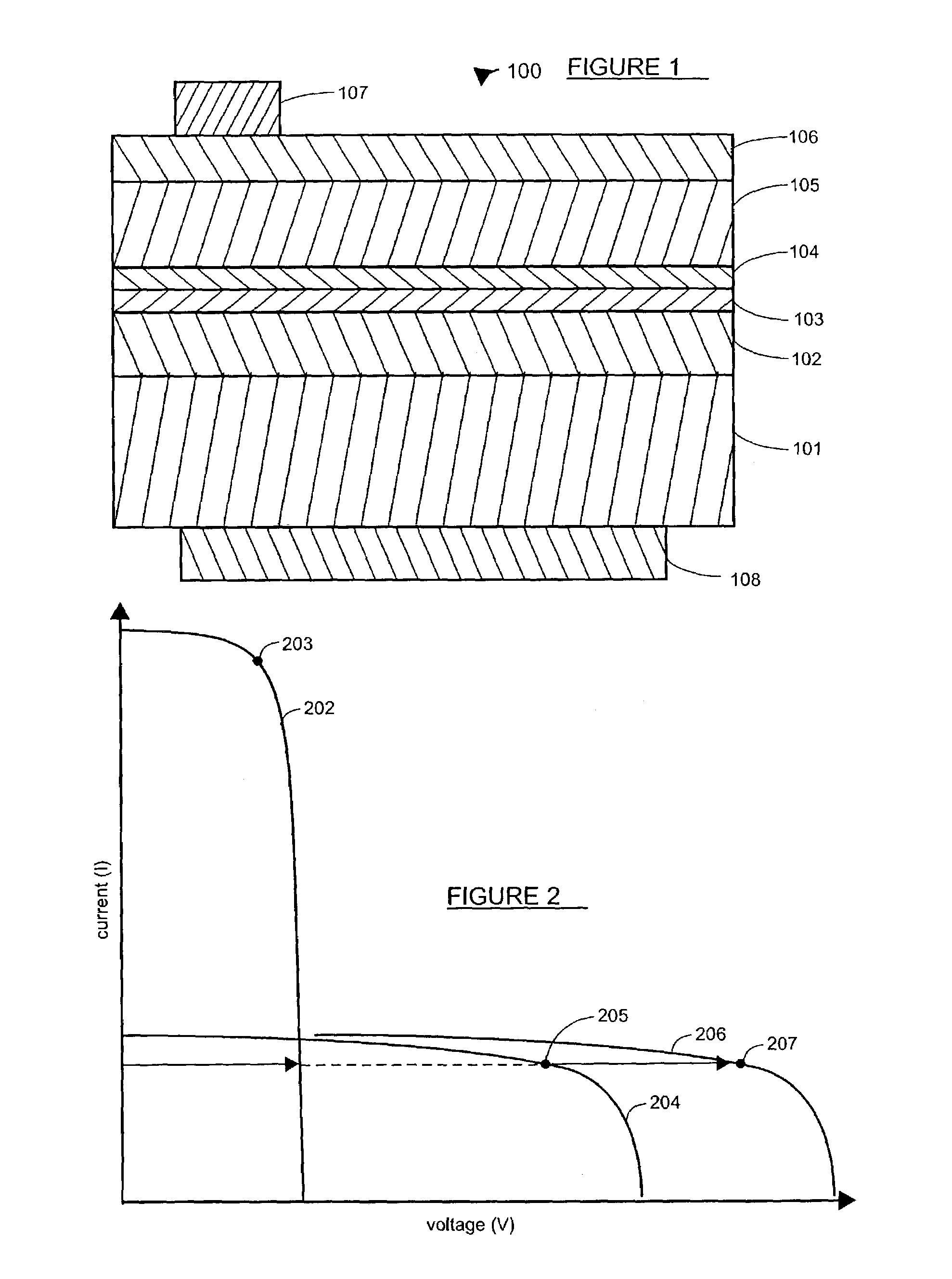

GaP/silicon tandem solar cell with extended temperature range

InactiveUS7148417B1Improve performanceHigh operating temperaturePhotovoltaic energy generationSemiconductor devicesTandem solar cellCrystalline silicon

A two-junction solar cell has a bottom solar cell junction of crystalline silicon, and a top solar cell junction of gallium phosphide. A three (or more) junction solar cell has bottom solar cell junctions of silicon, and a top solar cell junction of gallium phosphide. The resulting solar cells exhibit improved extended temperature operation.

Owner:NASA

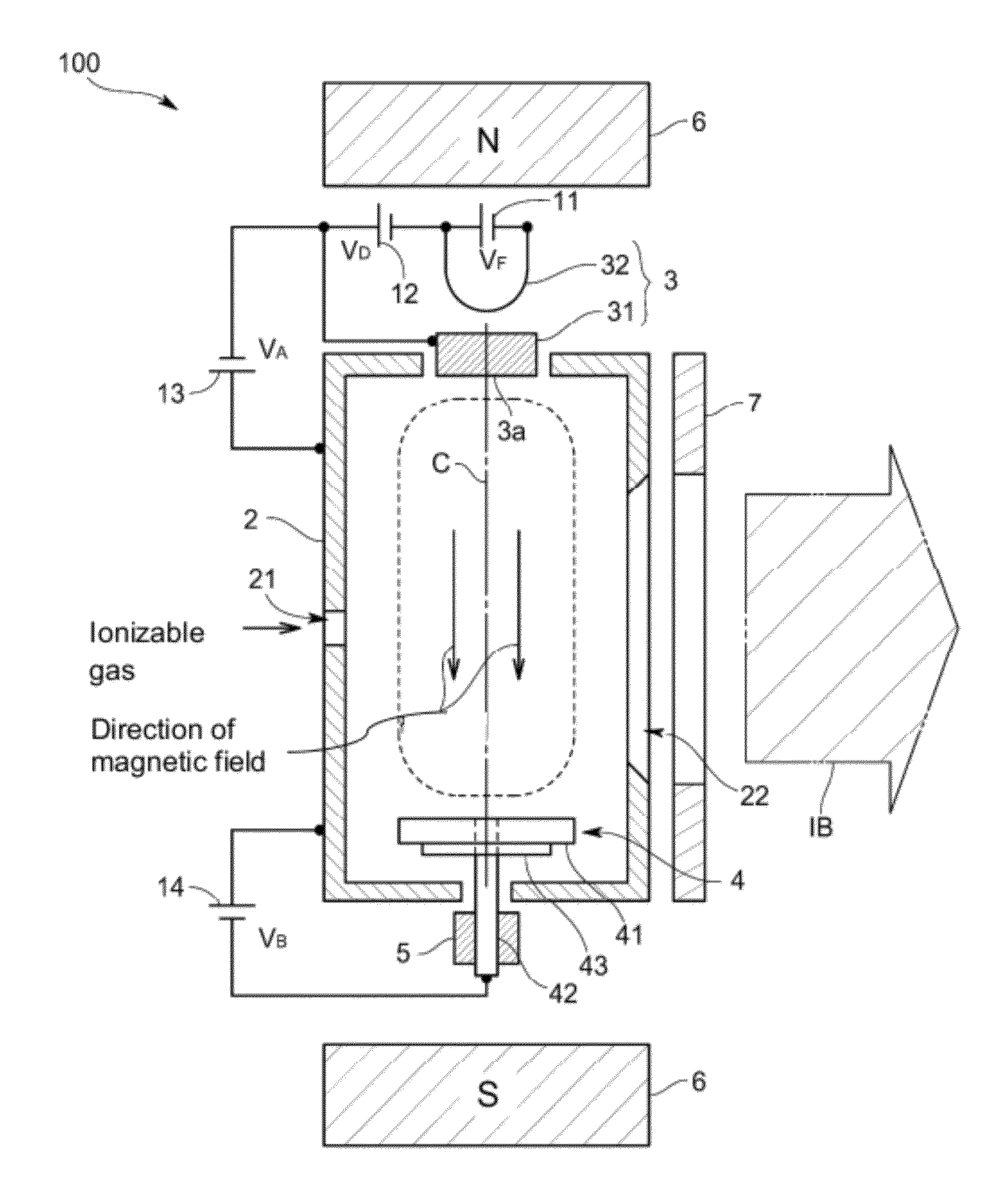

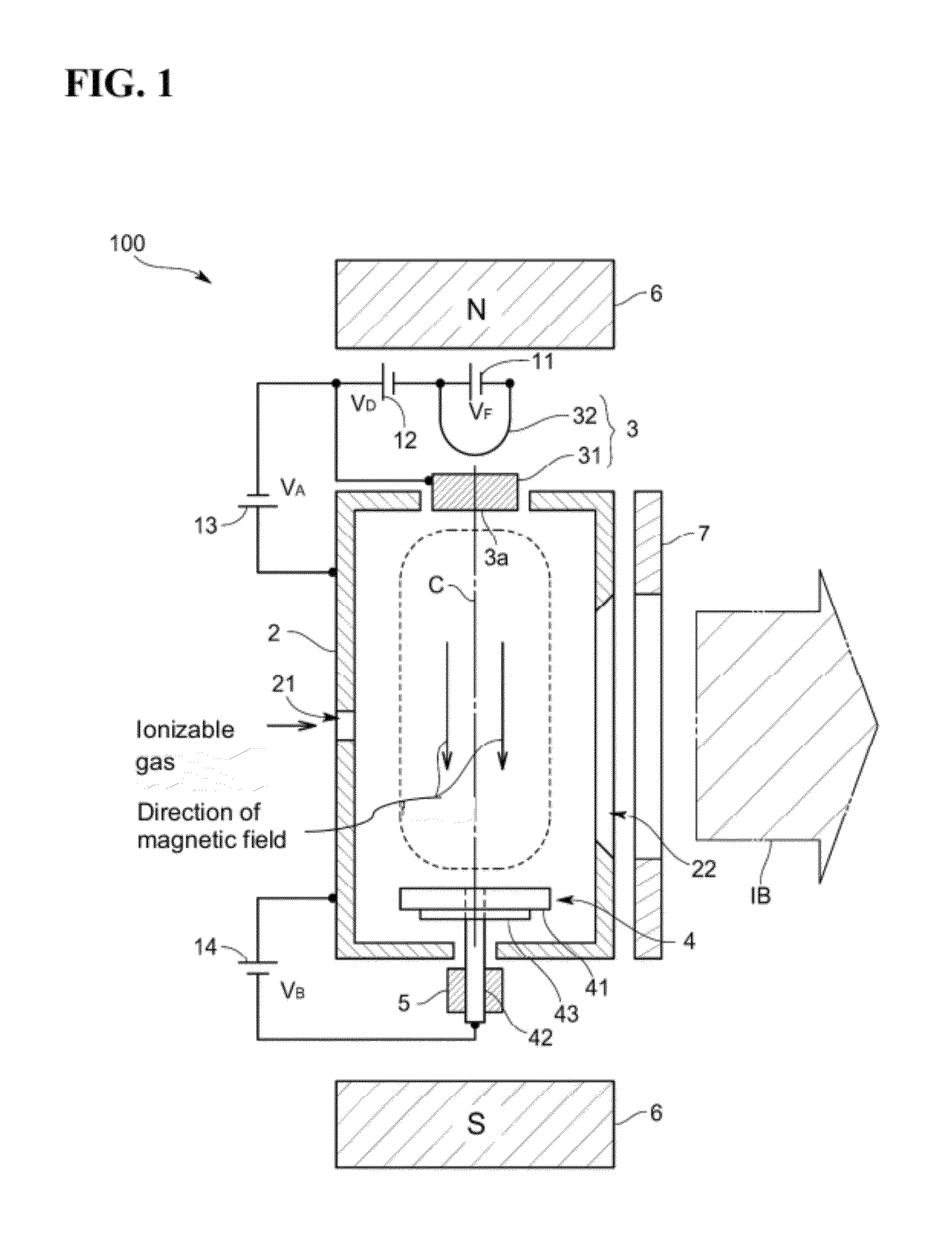

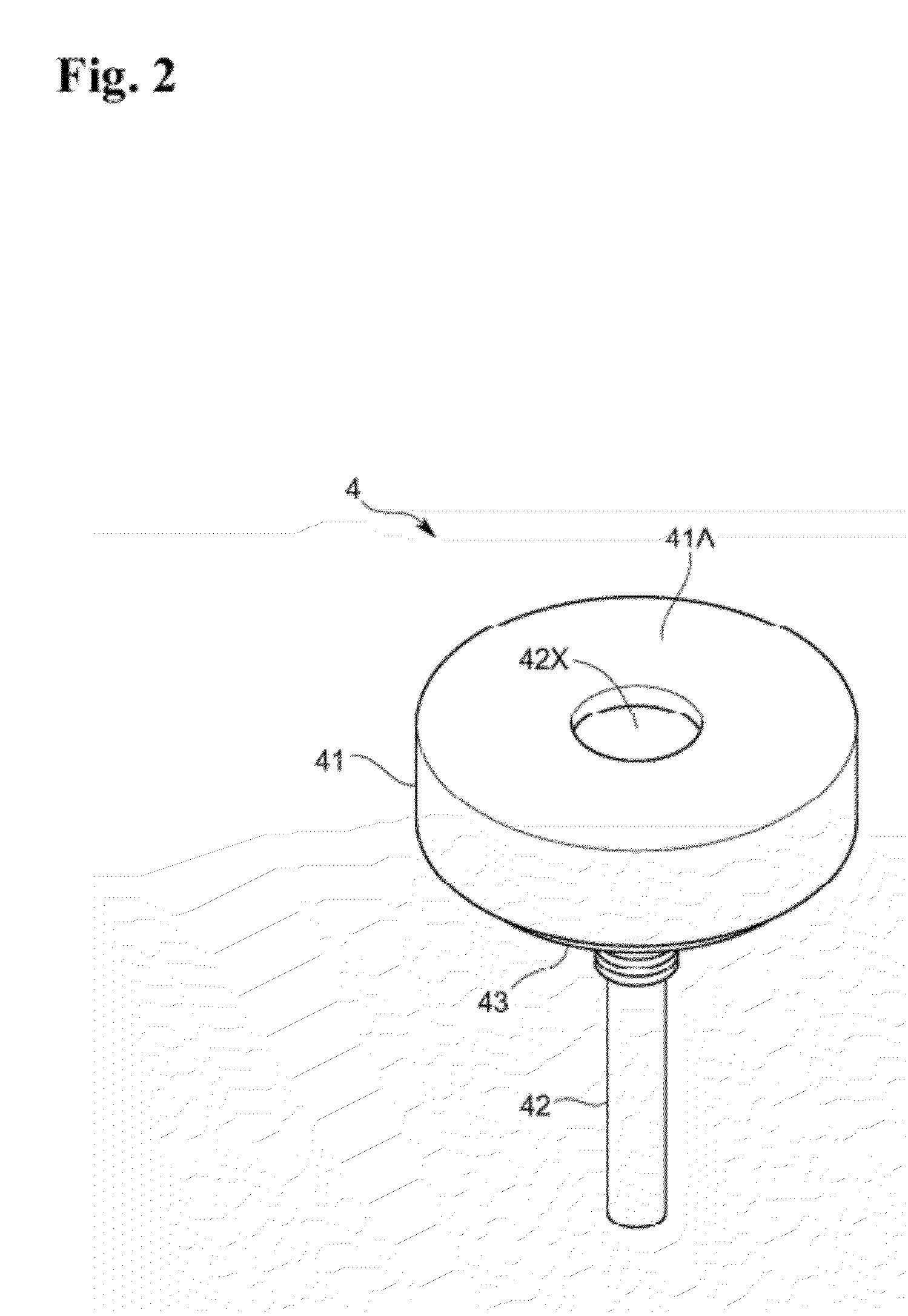

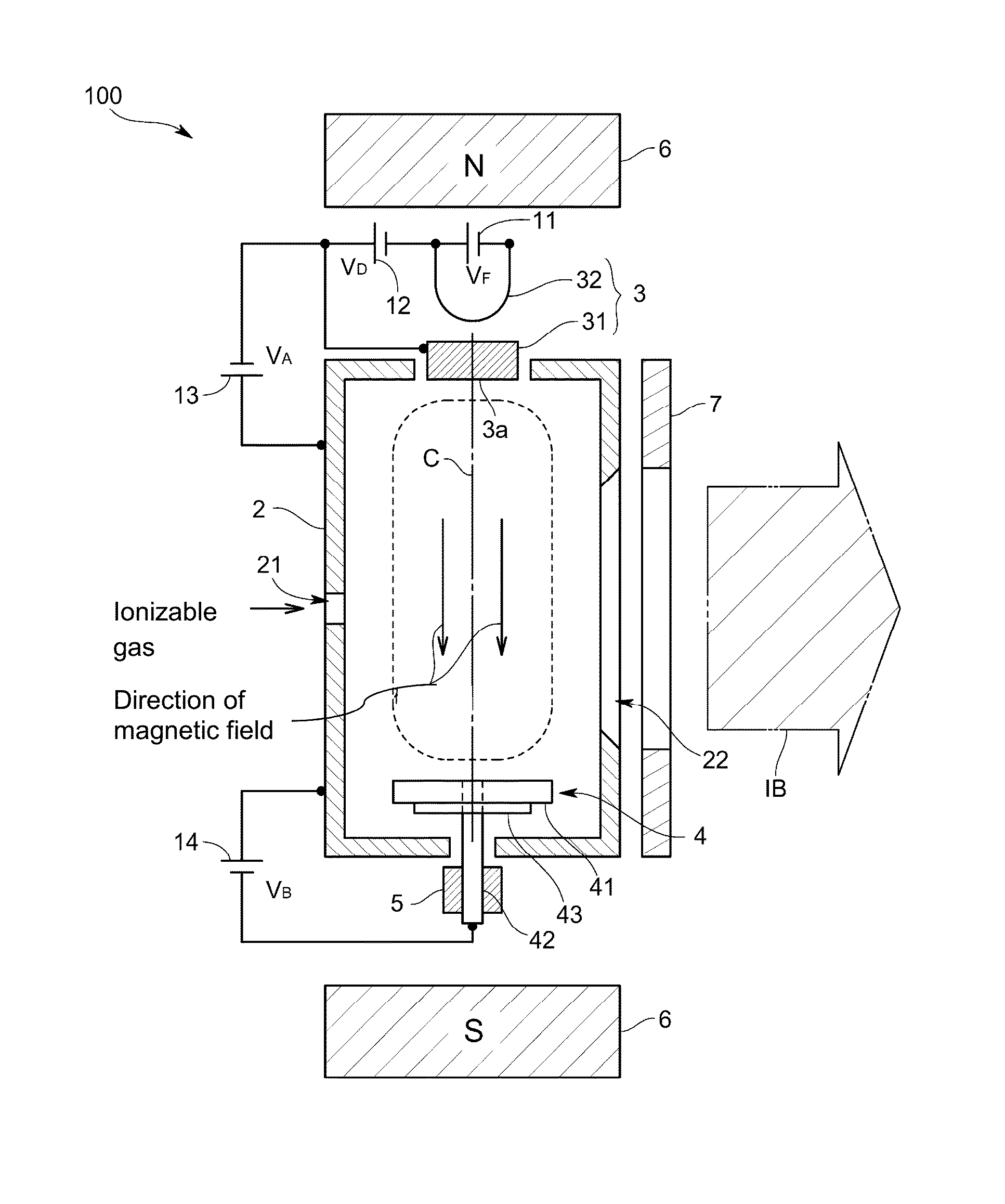

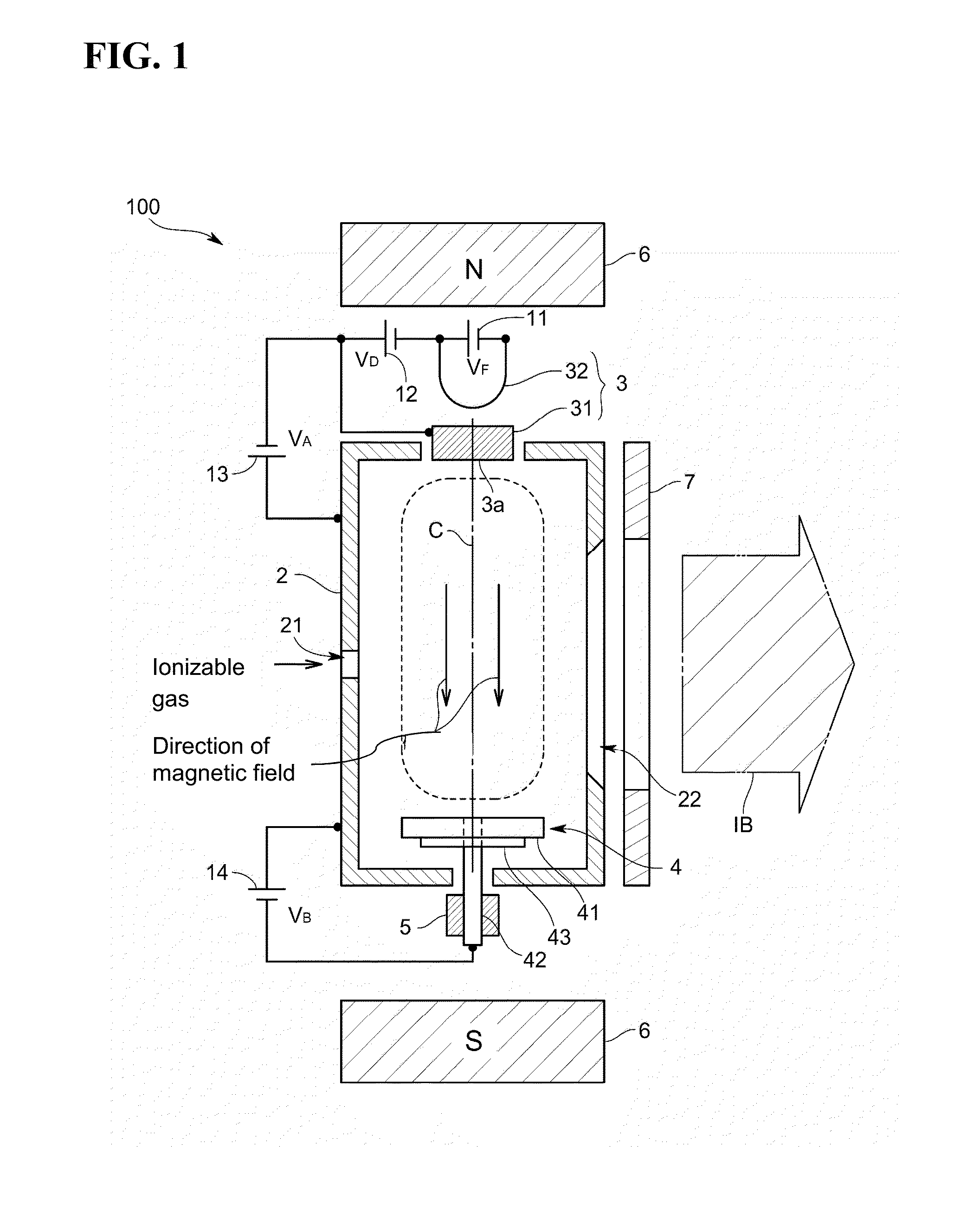

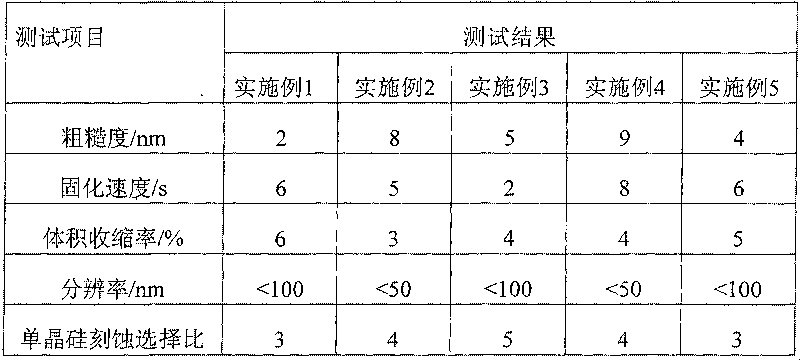

Ion source and repeller structure

InactiveUS20120255490A1Improve efficiencyIncrease surface areaIon beam tubesSpray discharge apparatusChemical physicsGallium nitride

A repeller structure comprises a target member configured to be sputtered by a plasma to emit given ions, and provided with a through-hole penetrating between a sputterable surface and a reverse surface thereof, and a repeller body which supports the target member while being inserted in the through-hole of the target member, and has a repeller surface exposed on the side of the sputterable surface through the through-hole. The target member is made of a material selected from the group consisting of gallium oxide, gallium nitride, gallium phosphide, gallium arsenide and gallium fluoride.

Owner:NISSIN ION EQUIP CO LTD

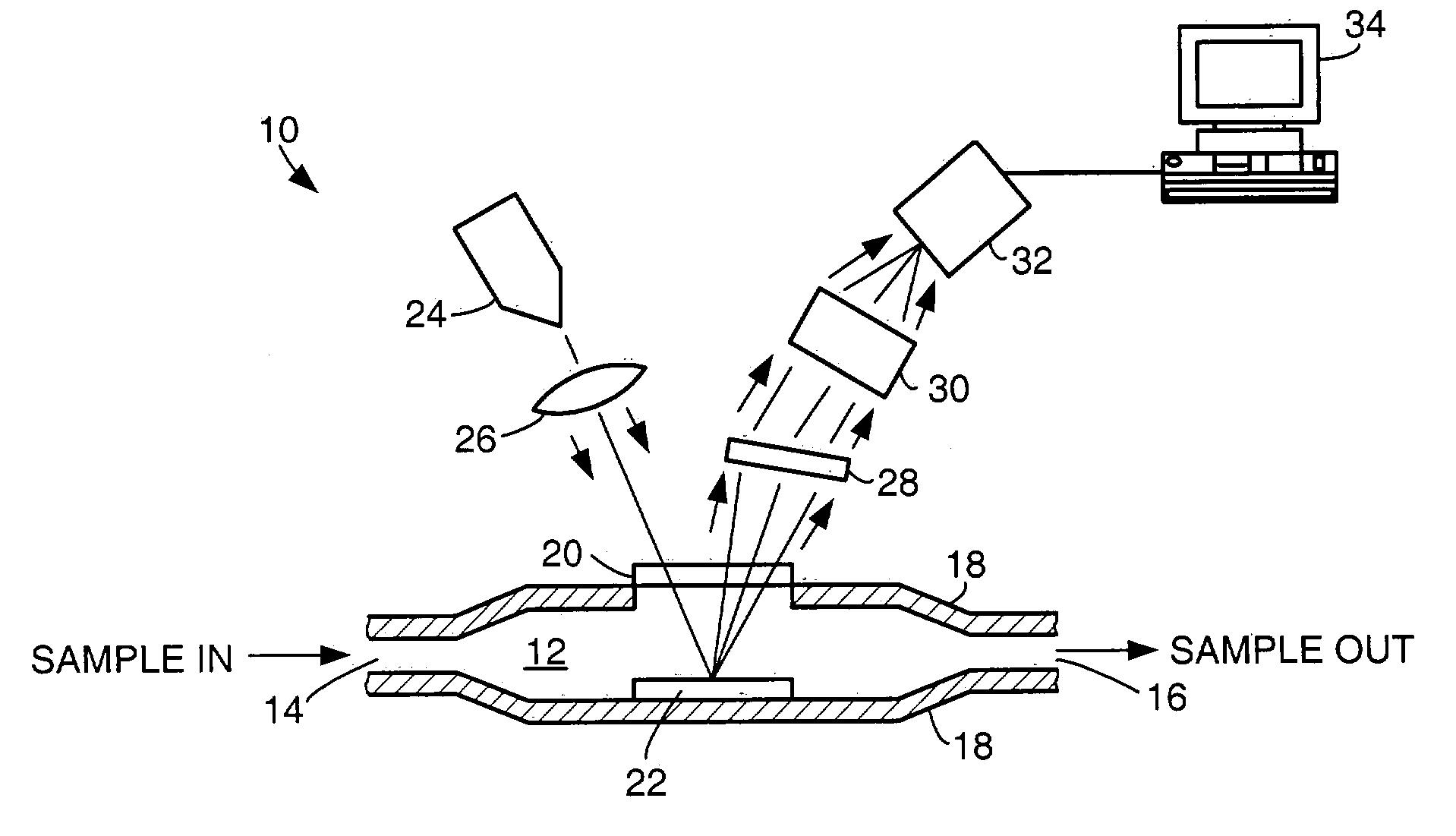

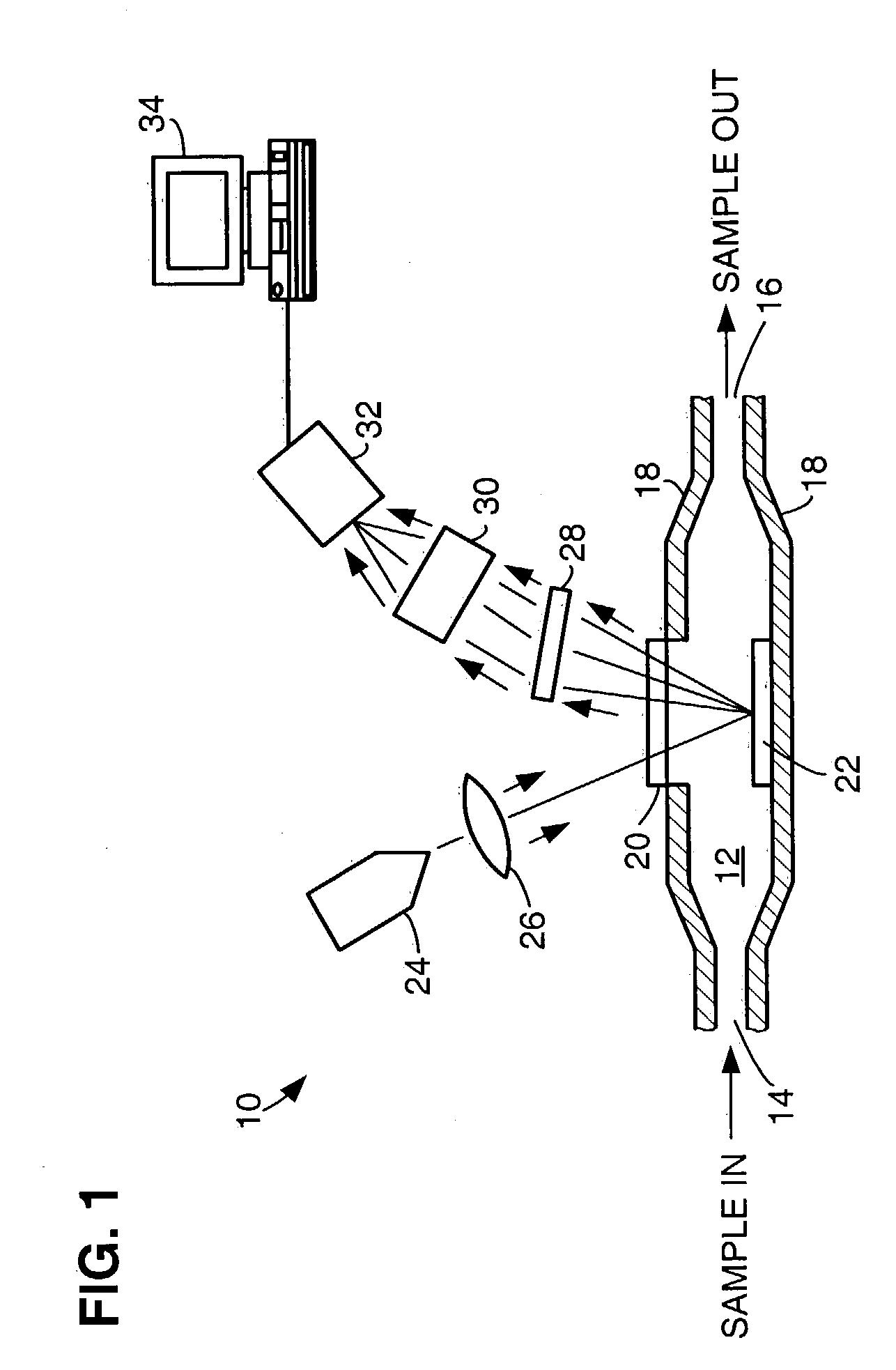

Method, structure, and apparatus for Raman spectroscopy

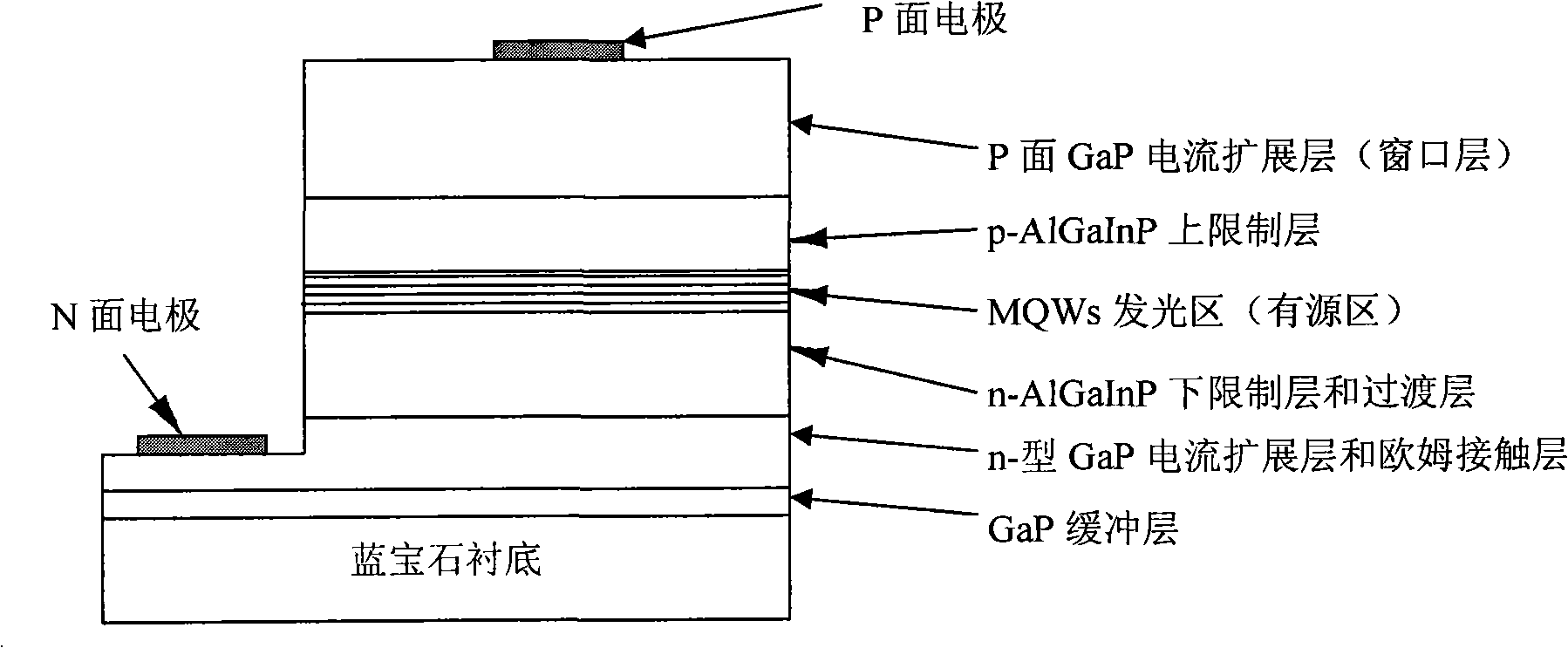

Disclosed herein are a Raman spectroscopy structure comprising a porous material substrate, and a method of performing Raman spectroscopy of a sample disposed adjacent to the structure comprising the porous material substrate. Generally, the substrate includes one or more layers of a porous material such as porous silicon, porous polysilicon, porous ceramics, porous silica, porous alumina, porous silicon-germanium, porous germanium, porous gallium arsenide, porous gallium phosphide, porous zinc oxide, and porous silicon carbide. It has been discovered that such a substrate material, when excited with near-infrared light, does not exhibit undesired background fluorescence characteristic of other known Raman spectroscopy substrates.

Owner:INTEL CORP

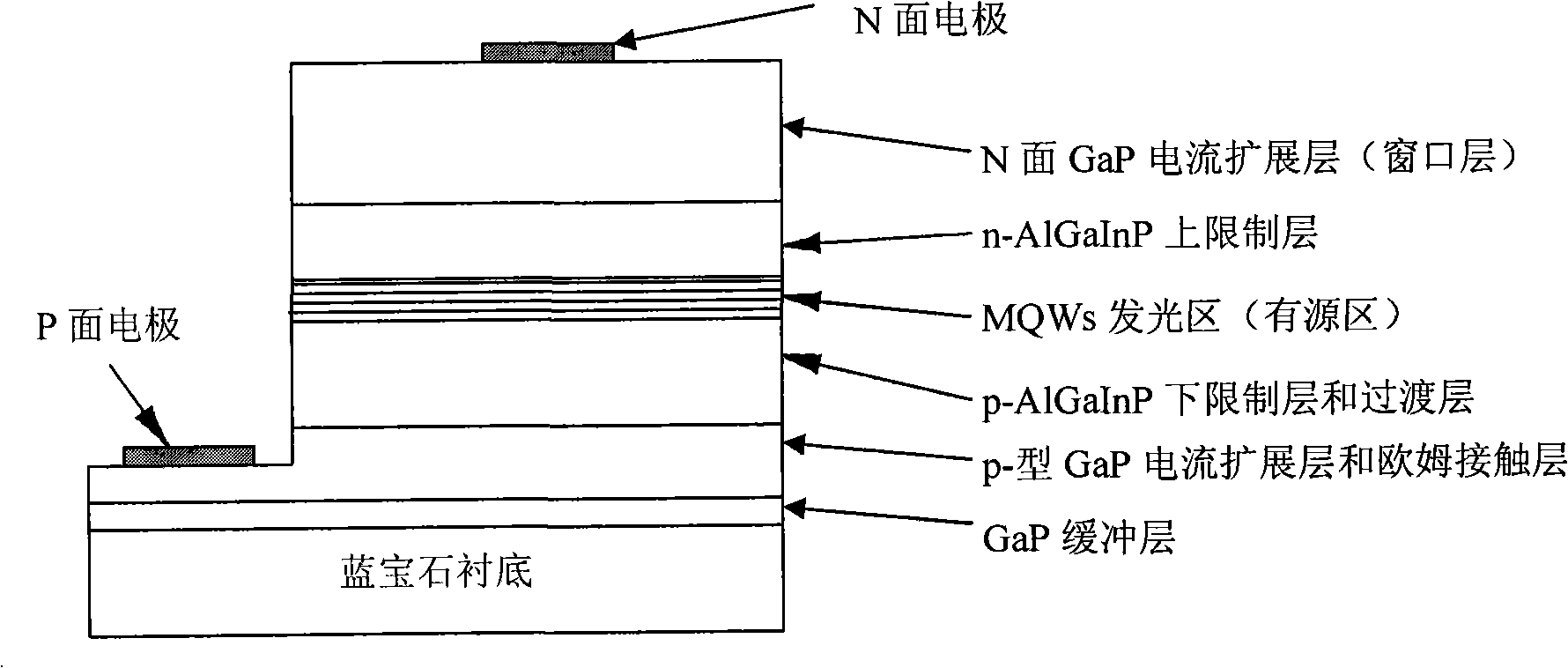

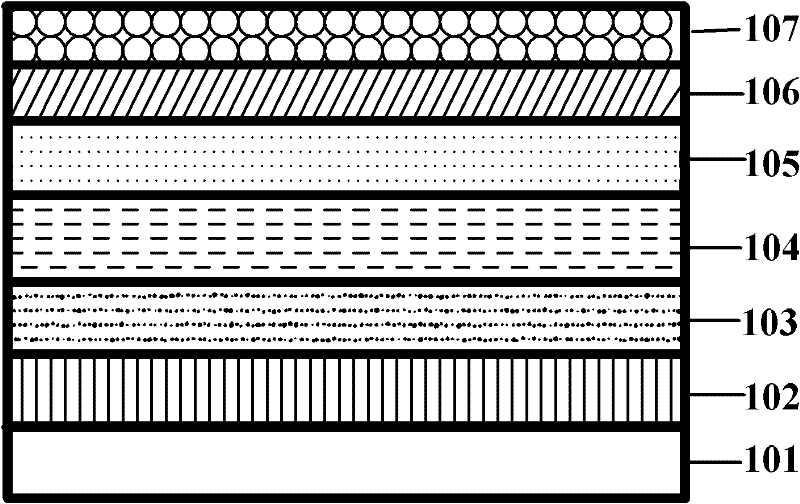

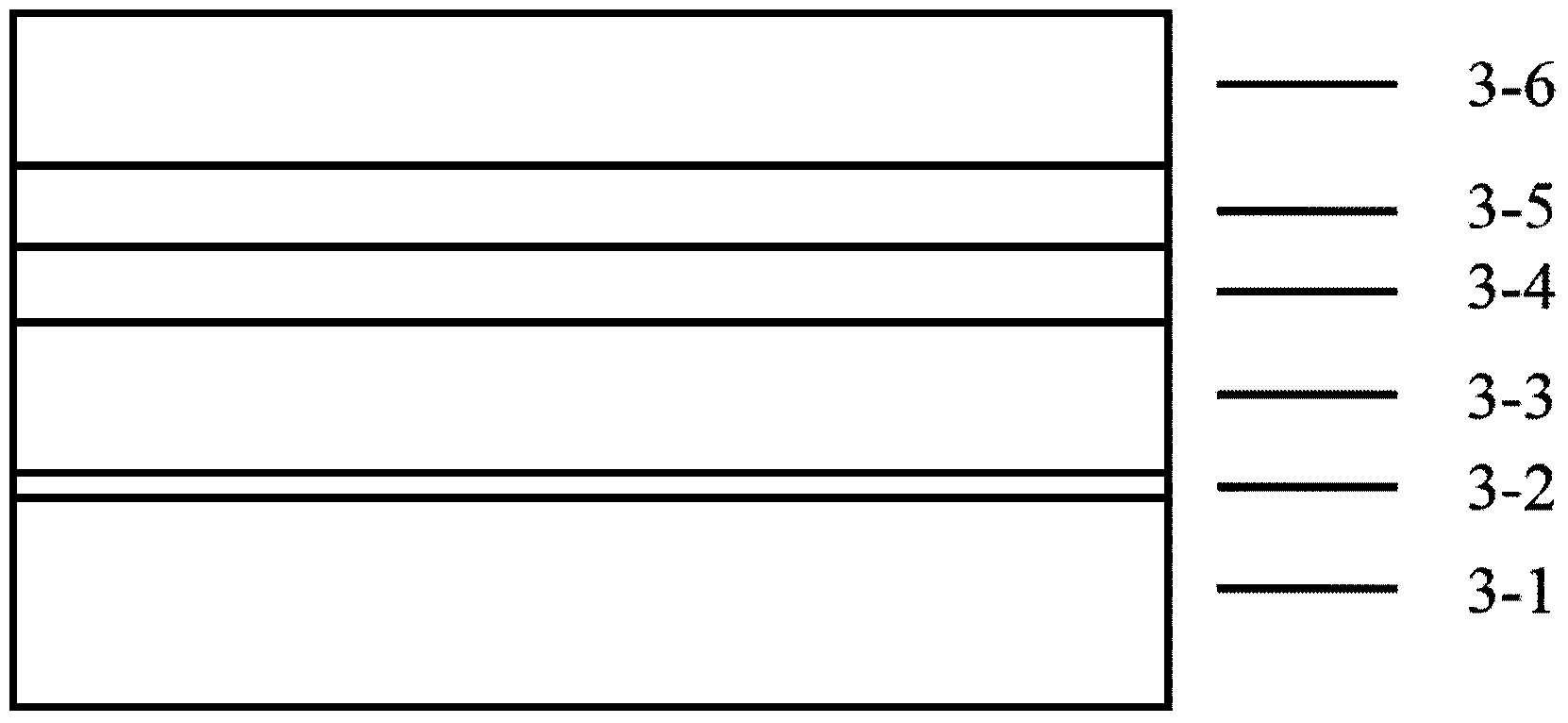

Epitaxial wafer of AlGaInP light emitting diode with sapphire underlay and preparation method thereof

InactiveCN101540359ANo light absorption problemInhibition of growth defectsSemiconductor devicesLattice mismatchLight-emitting diode

The invention provides an epitaxial wafer of an AlGaInP light emitting diode with a sapphire underlay and a preparation method thereof. An epitaxial structure of the light emitting diode sequentically comprises the sapphire underlay, a low-temperature GaP buffer layer, a high-temperature GaP buffer layer, a GaP current expansion and ohmic contact layer, an AlGaInP transition layer, a lower limiting layer, a multiple quantum well AlGaInP active area, an AlGaInP upper limiting layer and a GaP current expansion layer from bottom to top. The preparation method comprises the steps that each epitaxial layer grows on the sapphire underlay layer by layer sequentially. The epitaxial wafer uses the sapphire as the epitaxial growth underlay and uses gallium phosphide as the buffer layer. Because the sapphire and the gallium phosphide material are transparent to a wave band from yellow to red, the problem of light absorption of the underlay does not exist. The gallium phosphide buffer layer can inhibit the material growth defect caused by lattice mismatch and heat expansion coefficient mismatch between the sapphire underlay and the AlGaInP material so as to greatly improve the light output capability of the light emitting diode.

Owner:Shandong Huaguang Optoelectronics Co. Ltd.

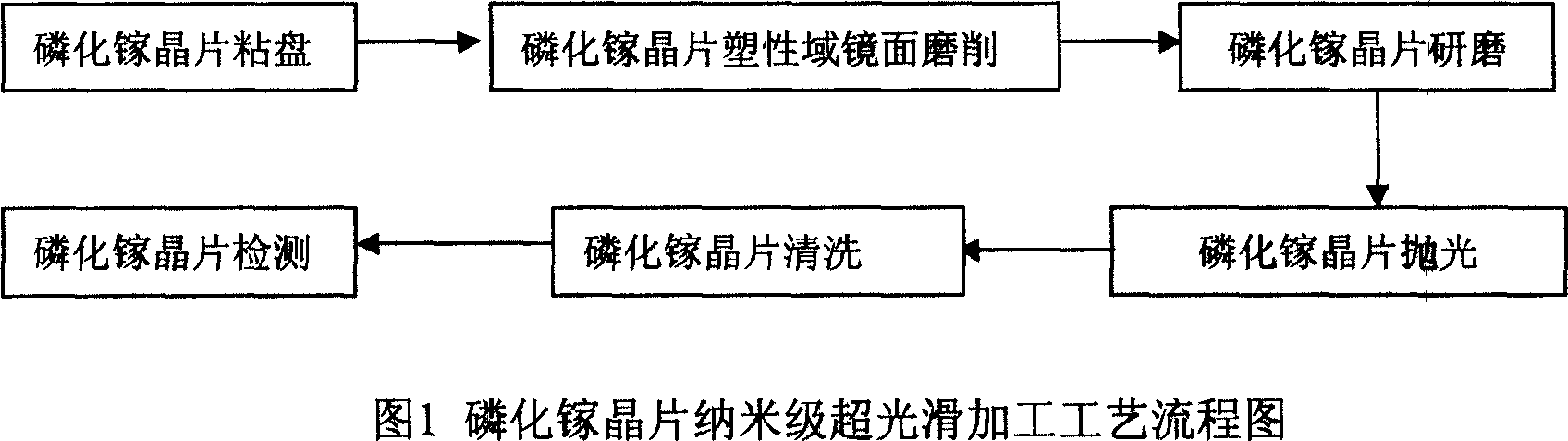

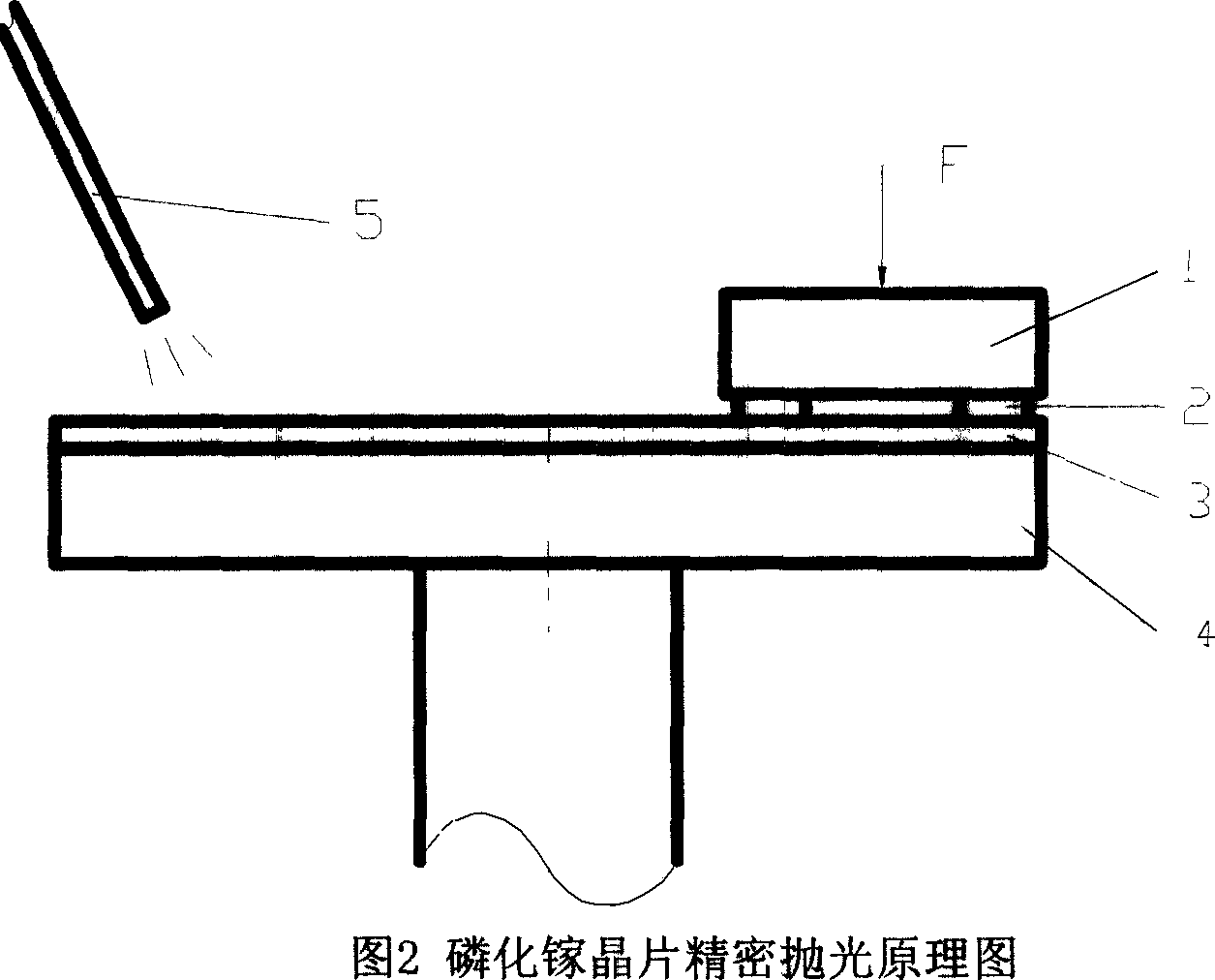

Technique for nanometer grade super smooth processing gallium phosphide wafer

InactiveCN1947944AEasy to processQuality improvementSemiconductor/solid-state device manufacturingLapping machinesProduction rateSurface roughness

A nano-class super-smooth technology for processing the GaP wafer used to prepare blue and red LEDs includes such steps as adsorbing the GaP wafer on the bearing disc by water, plastic abrading, grinding, polishing and cleaning. Its dedicated grinding liquid, polishing liquid, cleaning liquid and their components are also disclosed.

Owner:周海

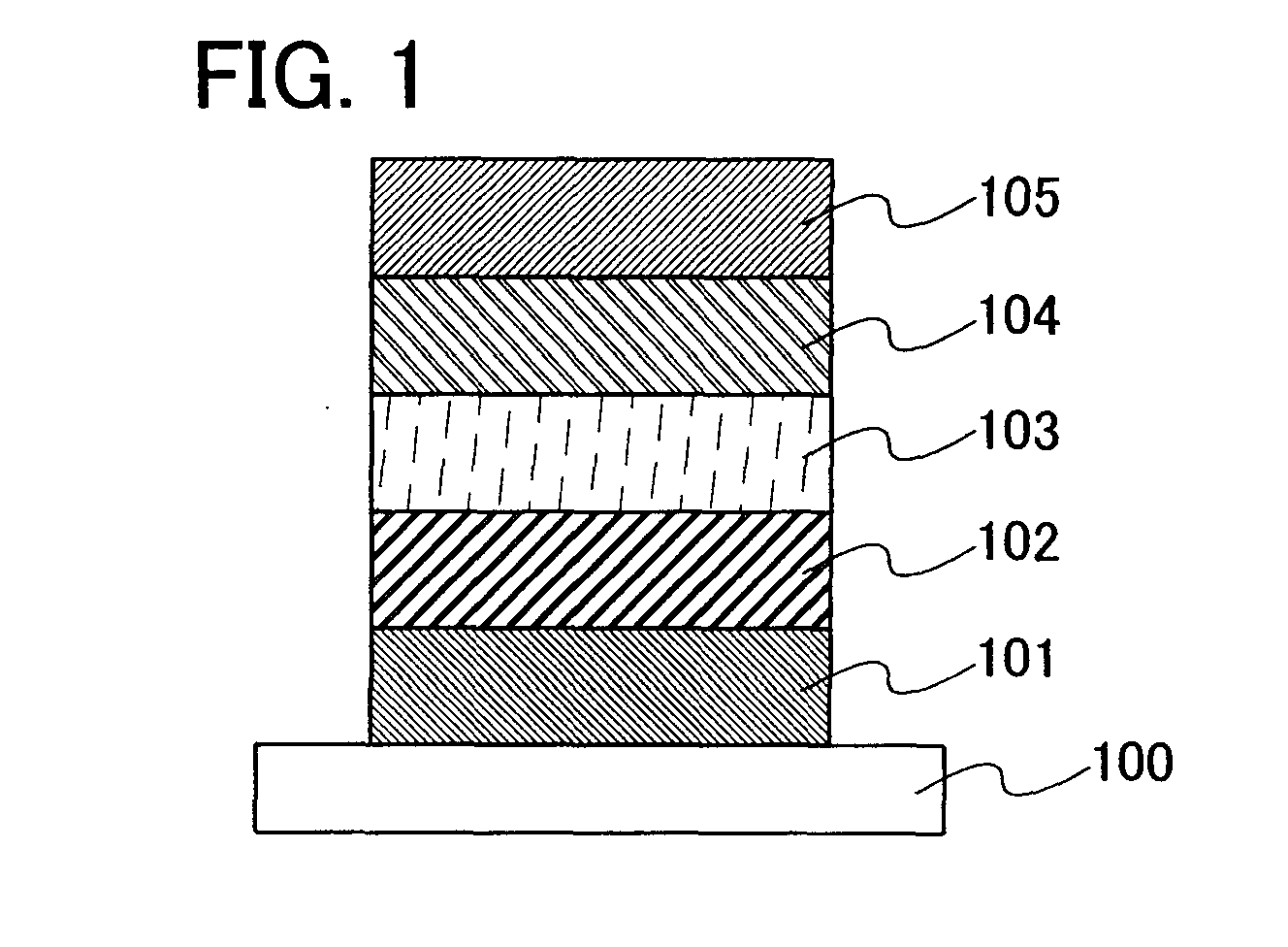

High brightness light emitting diode

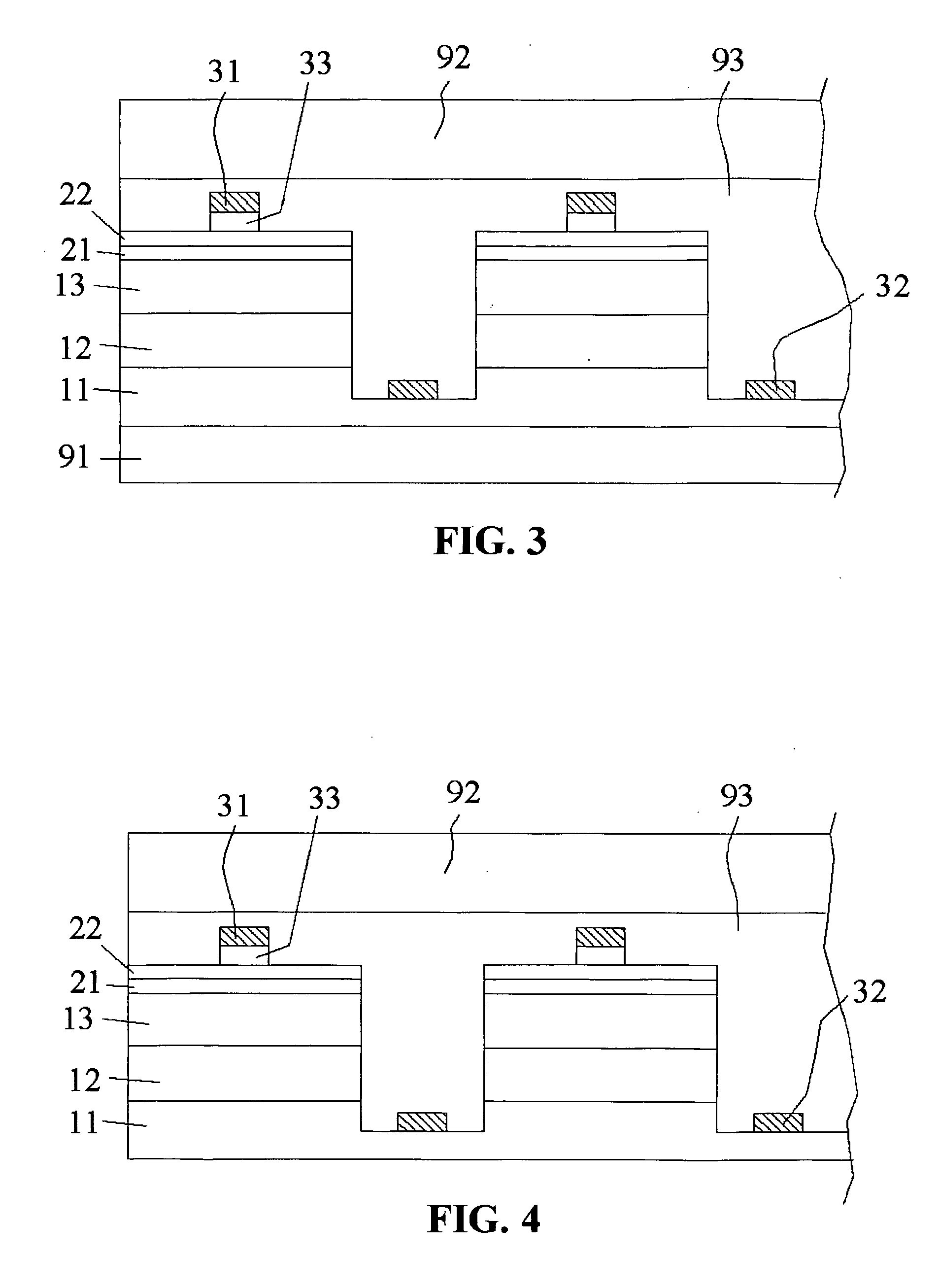

InactiveUS20050062061A1Enhanced glowIncrease brightnessSemiconductor/solid-state device manufacturingSemiconductor devicesQuantum wellOhmic contact

The present invention discloses a high brightness light emitting diode. The light emitting diode primarily includes a permanent substrate, a reflective mirror formed on said permanent substrate, an n-type cladding layer formed on said reflective mirror, and defining a higher port and a lower port on an upper surface thereof, an active layer with quantum well structure formed on said higher port of said n-type cladding layer, a p-type cladding layer formed on said active layer, a p-GaP layer formed on said p-type cladding layer, a metal contact layer formed on said GaP layer, a p-type ohmic contact electrode formed on said metal contact layer, and an n-type ohmic contact electrode formed on said lower port of said n-type cladding layer. By providing a gallium phosphide window and a reflective mirror, brightness of the LED can be promoted.

Owner:NAT SCI COUNCIL

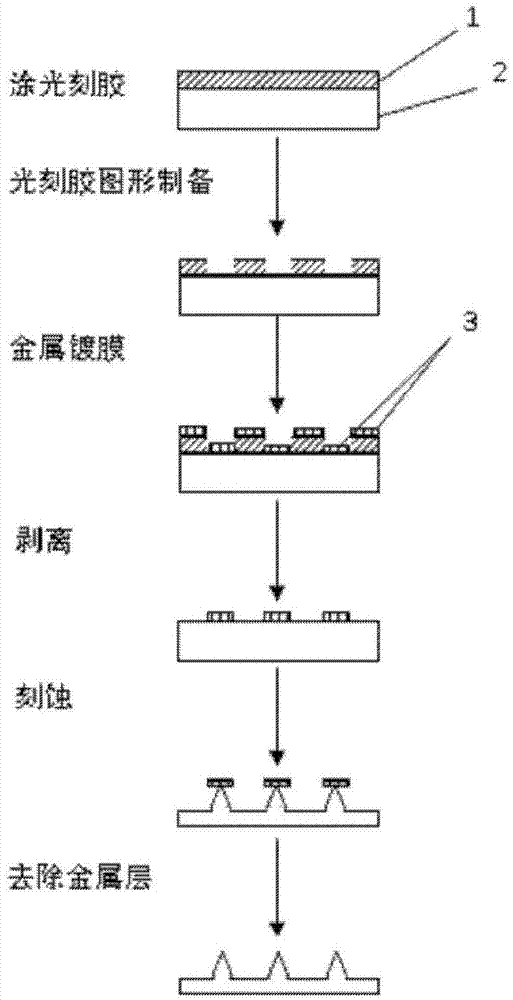

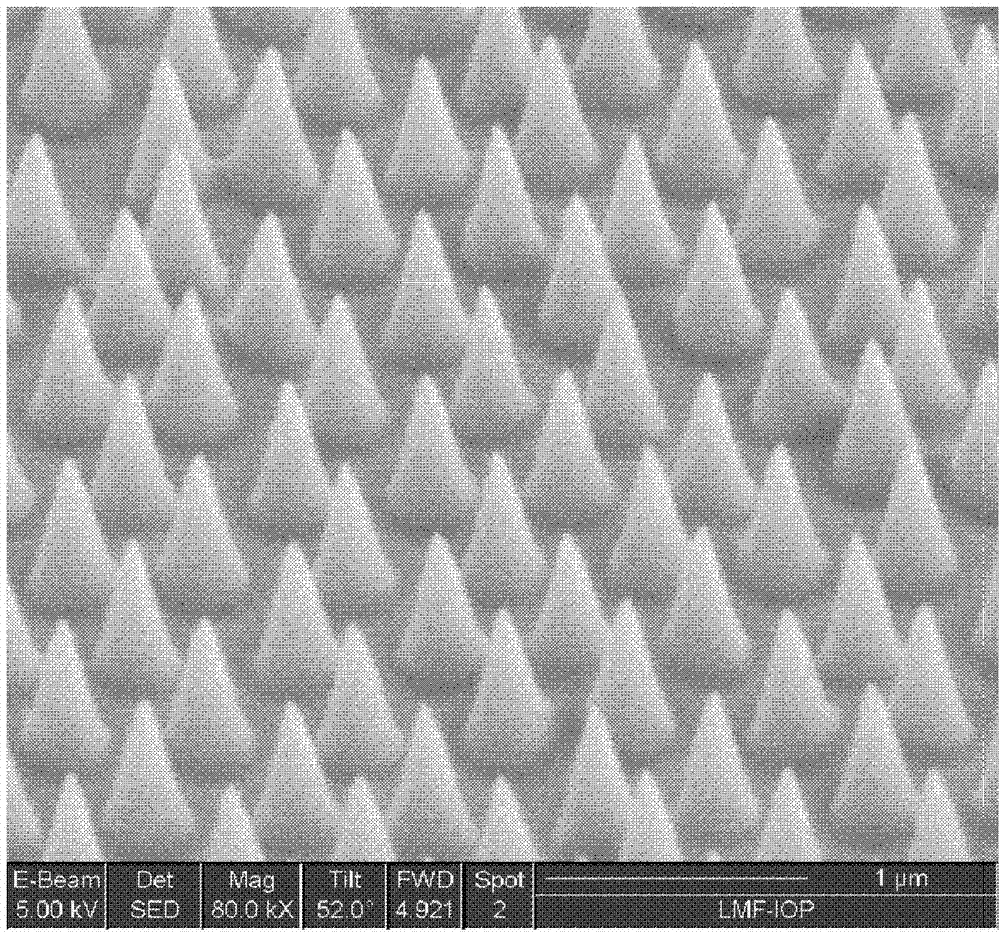

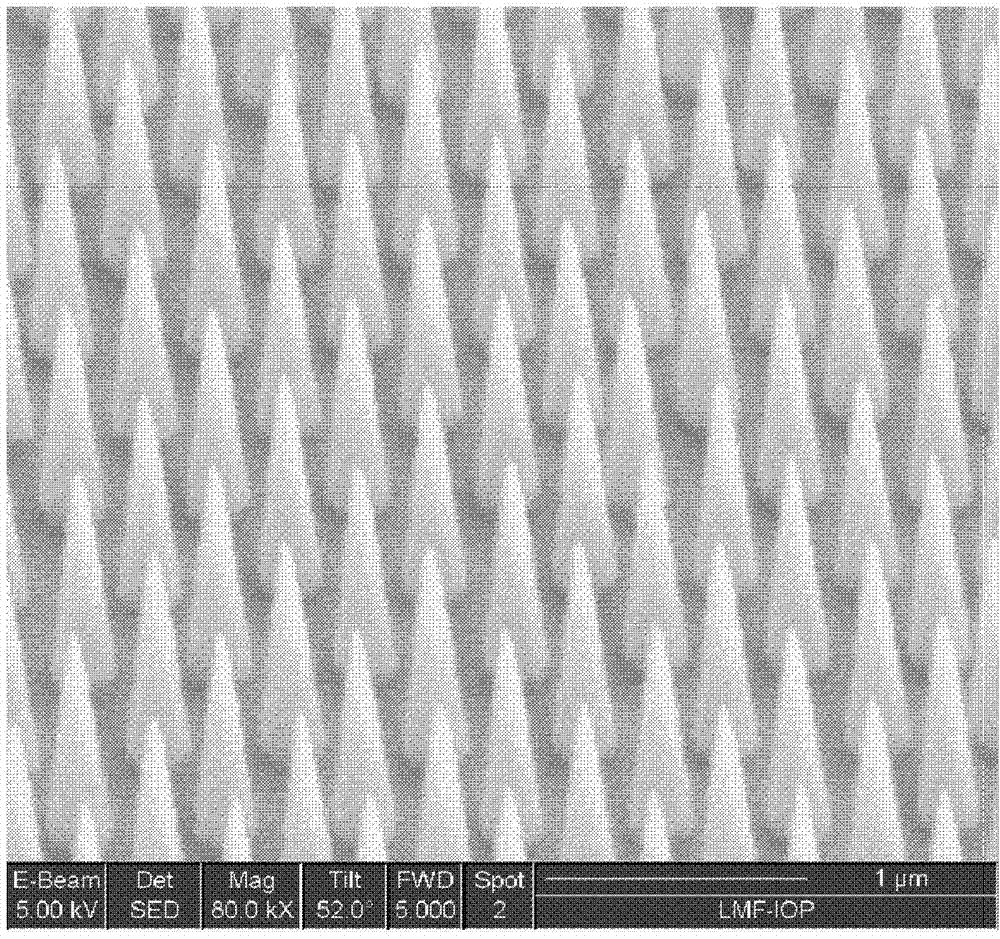

Method for preparing cone-shaped structure on gallium phosphide (GaP) surface

ActiveCN103199161AAdd depthImprove light extraction efficiencySemiconductor devicesMicrometerNanoscopic scale

The invention provides a method for preparing a cone-shaped structure on a gallium phosphide (GaP) surface. Photoresist is coated on the surface of a GaP sample in a spinning mode, and then a micrometer / nanometer scale image preparation technology is used for preparing a hole-shaped photoresist array pattern on the photoresist to obtain a sample with the hole-shaped photoresist array pattern; metal plating equipment is used for growing a metal layer on the sample with the hole-shaped photoresist array pattern, and a desolventizing process is carried out to obtain a sample with a metal-column-shaped pattern array; dry etching equipment is used for carrying out etching on the sample with the metal-column-shaped pattern array to obtain a GaP sample of a cone-shaped array structure; and the GaP sample of the cone-shaped array structure is placed in metal corrosive liquid to be cleaned, residual metal layers on the surface of the GaP sample of the cone-shaped array structure are removed, and then a cone-shaped array structure is obtained on the Gap surface. The cone-shaped array structure can be used for improvement of light extraction efficiency of an AlGaInP-based red light-emitting diode (LED).

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

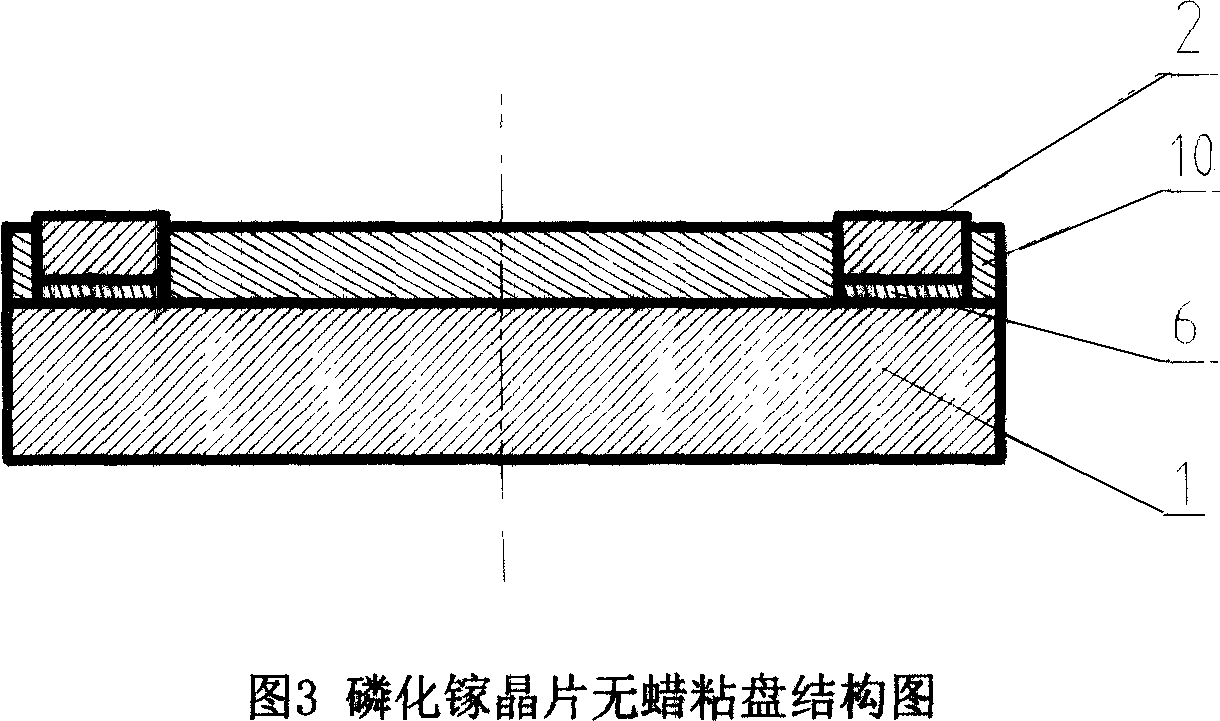

Two-sided polishing method for gallium phosphide crystal plate

ActiveCN101130229ACause harmSimple methodPolishing machinesSemiconductor/solid-state device manufacturingEngineeringTotal thickness

The invention discloses a double-faced polishing method of gallium phosphide wafer, which comprises the following steps: (1) cleaning the wafer in the abluent through ultrasound; controlling the temperature between 50 deg. c and 100 deg. c; (2) pasting; (3) placing the cooled polishing disc on the polishing cloth; using polishing arm to fix the polishing disc under 10-50psi; setting the flow of the polishing liquid at 10-40ml / min under 5-25 deg. c to polish; flushing after the thickness is standard; (4) removing the wafer; pasting; polishing another face; (5) detecting the cleaning. The invention has strong operation and convenience and utility with low cost for chemical agent, which improves the polishing yield over 85% without harming environment and human body. The total thickness of the wafer is not more than 6um with angularity not more than 25um and wafer flatness not more than 5um, which avoids the defect of spot, fog, particle, crack, orange peel and so on.

Owner:GRINM GUOJINGHUI NEW MATERIALS CO LTD

Aluminum diecasting alloy

An aluminum alloy suitable for diecasting of components with high elongation in the cast state contains, as well as aluminum and unavoidable impurities, 8.0 to 11.5 w. % silicon, 0.3 to 0.8 w. % manganese, 0.08 to 0.4 w. % magnesium, max 0.4 w. % iron, max 0.1 w. % copper, max 0.1 w. % zinc, max 0.15 w. % titanium and 0.05 to 0.5 w. % molybdenum. Optionally, the alloy also contains 0.05 to 0.3 w. % zirconium, 30 to 300 ppm strontium or 5 to 30 ppm sodium and / or 1 to 30 ppm calcium for permanent refinement and for grain refinement gallium phosphide and / or indium phosphide in a quantity corresponding to 1 to 250 ppm phosphorus and / or titanium and boron added by way of an aluminum master alloy with 1 to 2 w. % Ti and 1 to 2 w. % B.

Owner:АЛЮМИНИУМ РАЙНФЕЛЬДЕН ГМБХ

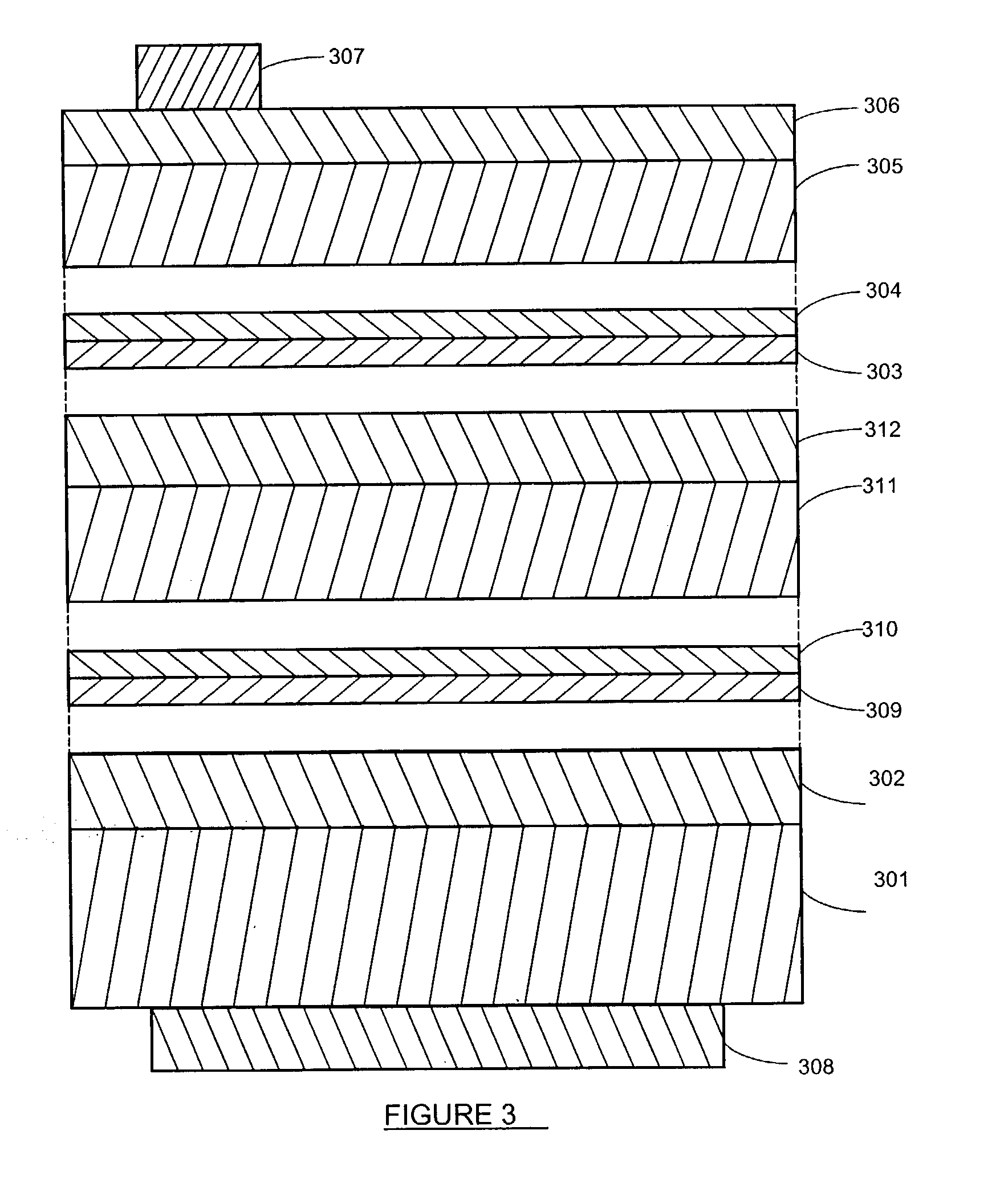

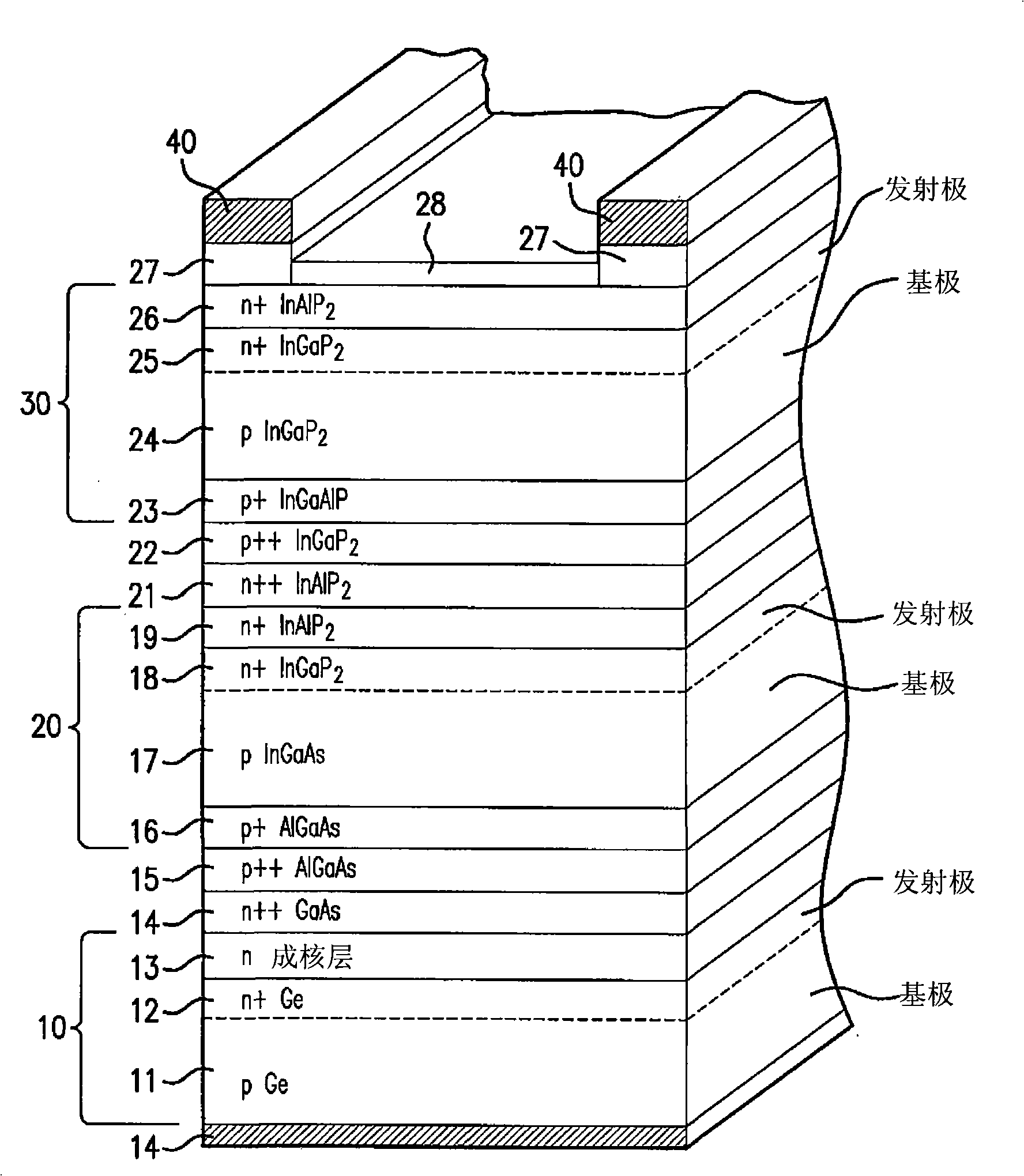

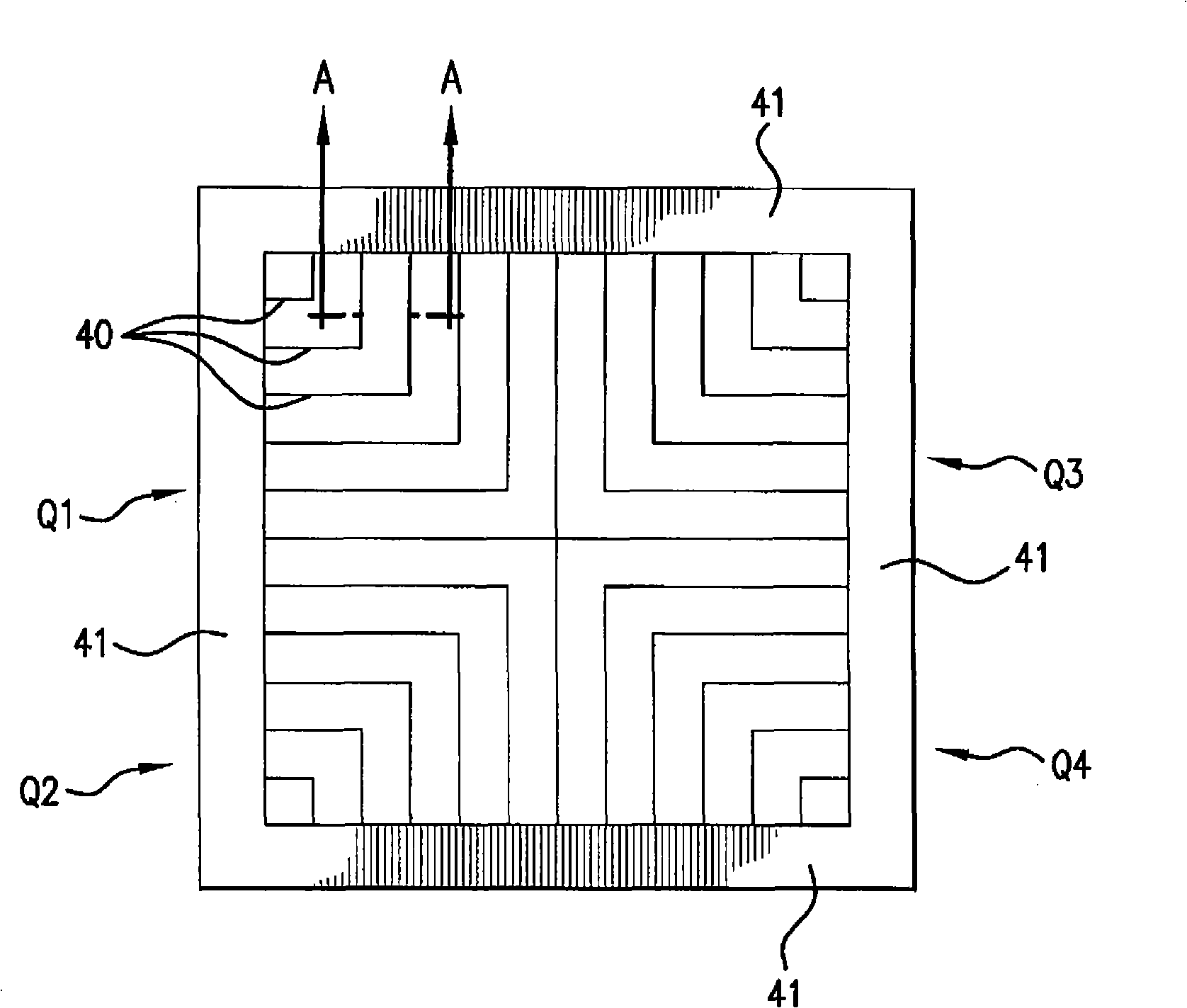

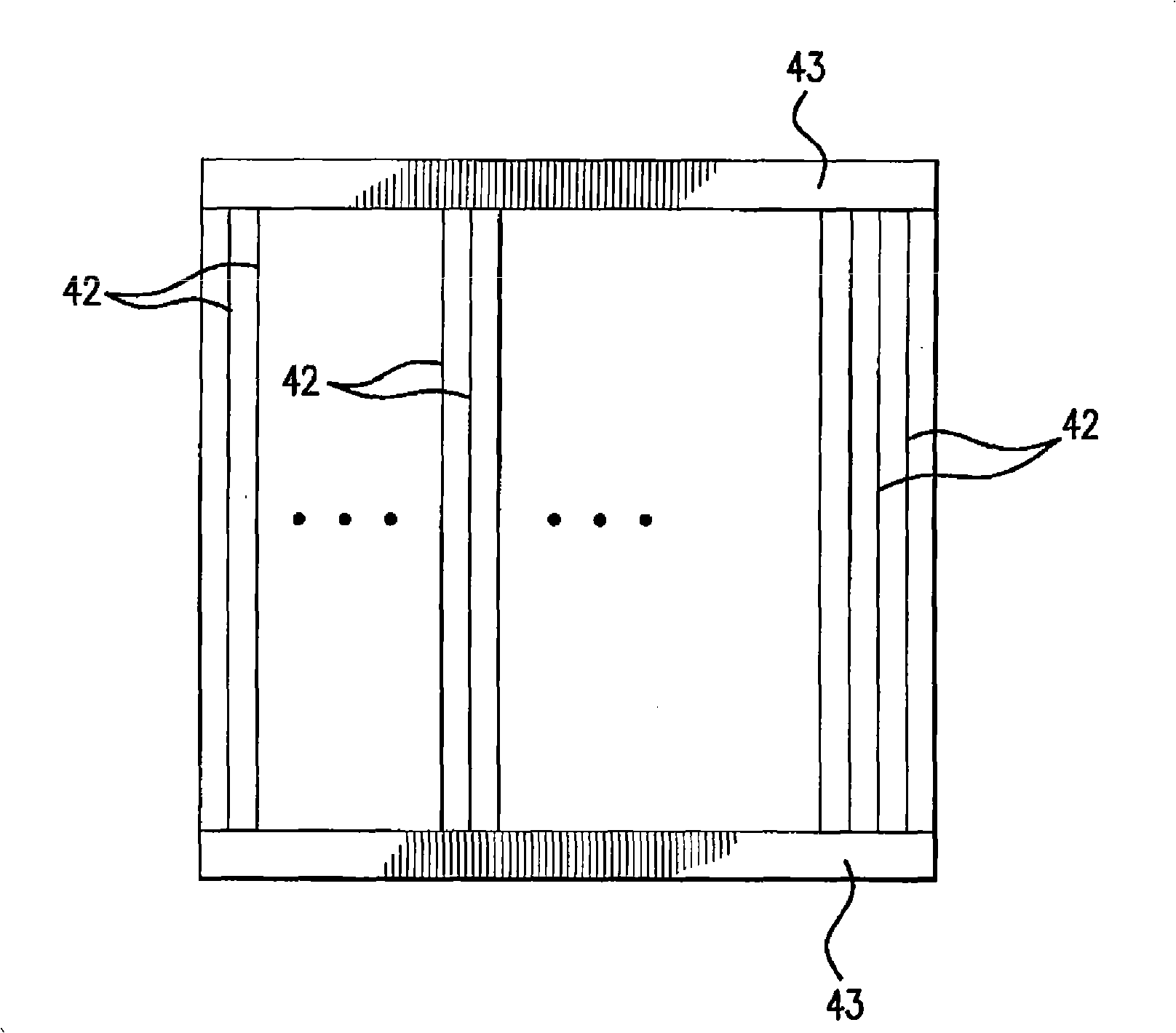

High concentration terrestrial solar cell arrangement with iii-v compound semiconductor cell

InactiveCN101494246APracticalPhotovoltaic energy generationSemiconductor devicesHigh concentrationIndium

The present invention relates to a concentrator photovoltaic solar cell array for terrestrial use for generating electrical power from solar radiation which includes the following components: a collection lens for generating collection degree higher than 500X; solar cell of gathered beam path including a germanium substrate having a first photovoltaic node and forming a bottom solar sub-cell; a gallium arsenide middle sub-cell set on the substrate; and gallium phosphide indium top sub-cell set above the middle sub-cell and provided with band-gap maximizes absorption in AM1.5 spectral regions and thickness larger than 7000 angstrom; and sheet resistance smaller than 330 Ohm / square and suitable for operation in collection degree larger than 20 solar collection degree, wherein current density of the top sub-cell larger than 35 ampere / square centimeter.

Owner:EMCORE INC

Aluminum die-casting alloy and manufacturing process thereof

The invention discloses an aluminum die-casting alloy and a manufacturing process thereof. The aluminum die-casting alloy comprises the following substances in weight ratio: 8.0-11.5% of silicon, 0.3-0.8% of manganese, 0.08-0.4% of magnesium, less than or equal to 0.4% of iron, less than or equal to 0.1% of copper, less than or equal to 0.1% of zinc, less than or equal to 0.15% of titanium, 0.05-0.5% of molybdenum, 0.05-0.3% of zirconium, 30-300 ppm of strontium or 5-30 ppm of sodium and / or 1-30 ppm of calcium, and the balance of aluminum and inevitable impurities, and the aluminum die-castingalloy is used for long-effect refining, wherein gallium phoshpide and / or indium phosphide with phosphor amount being 1-250 ppm is used for particle refining; and titanium and boron which are added inthe form of an aluminum matrix alloy containing 1-2wt% of Ti and 1-2wt% of B are used for particle refining. The aluminum die-casting alloy adopts a rare-earth reinforced aluminum alloy material anda precise die-casting technology, can perform light optimized design on a product structure on the premise of meeting using requirements as tensile strength, yield strength, hardness and the like of the aluminum die-casting alloy are improved, and technically meet higher requirements, on safety performance, of the current safety belt industry.

Owner:江苏恒昌铸造科技有限公司

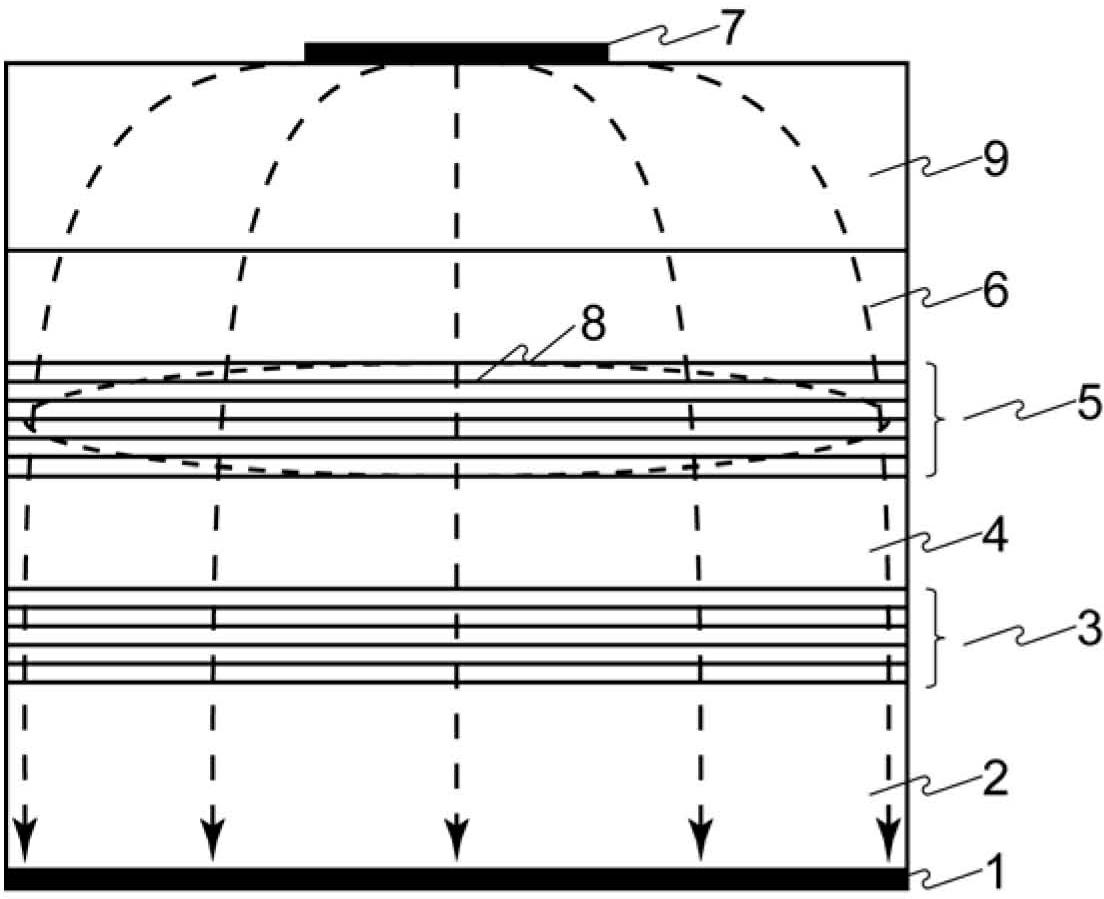

Method by adopting impulse airflow method to grow gallium phosphide (GaP) current extension layer

ActiveCN102593274AImprove efficiencyExtend your lifePolycrystalline material growthFrom chemically reactive gasesGas phaseChemical vapor deposition

The invention discloses a method by adopting an impulse airflow method to grow a gallium phosphide (GaP) current extension layer, which is characterized in that: a molybdenum (MO) source containing gallium atoms, phosphorane and a doping source are alternatively introduced into a reaction chamber of a metal organic chemical gas-phase precipitation system in a pulse way, or the flow-rate of the phosphorane is maintained constant, the MO source containing t he gallium atoms and the doping source are introduced in a pulse way. Due to adoption of the method, transition time of gallium atoms and phosphorus atoms on the surface of an extension layer can be increased, so that the gallium atoms and the phosphorus atoms can adequately cover the surface of the extension layer, and a GaP current extension layer with high quality can be obtained.

Owner:XIAMEN CHANGELIGHT CO LTD

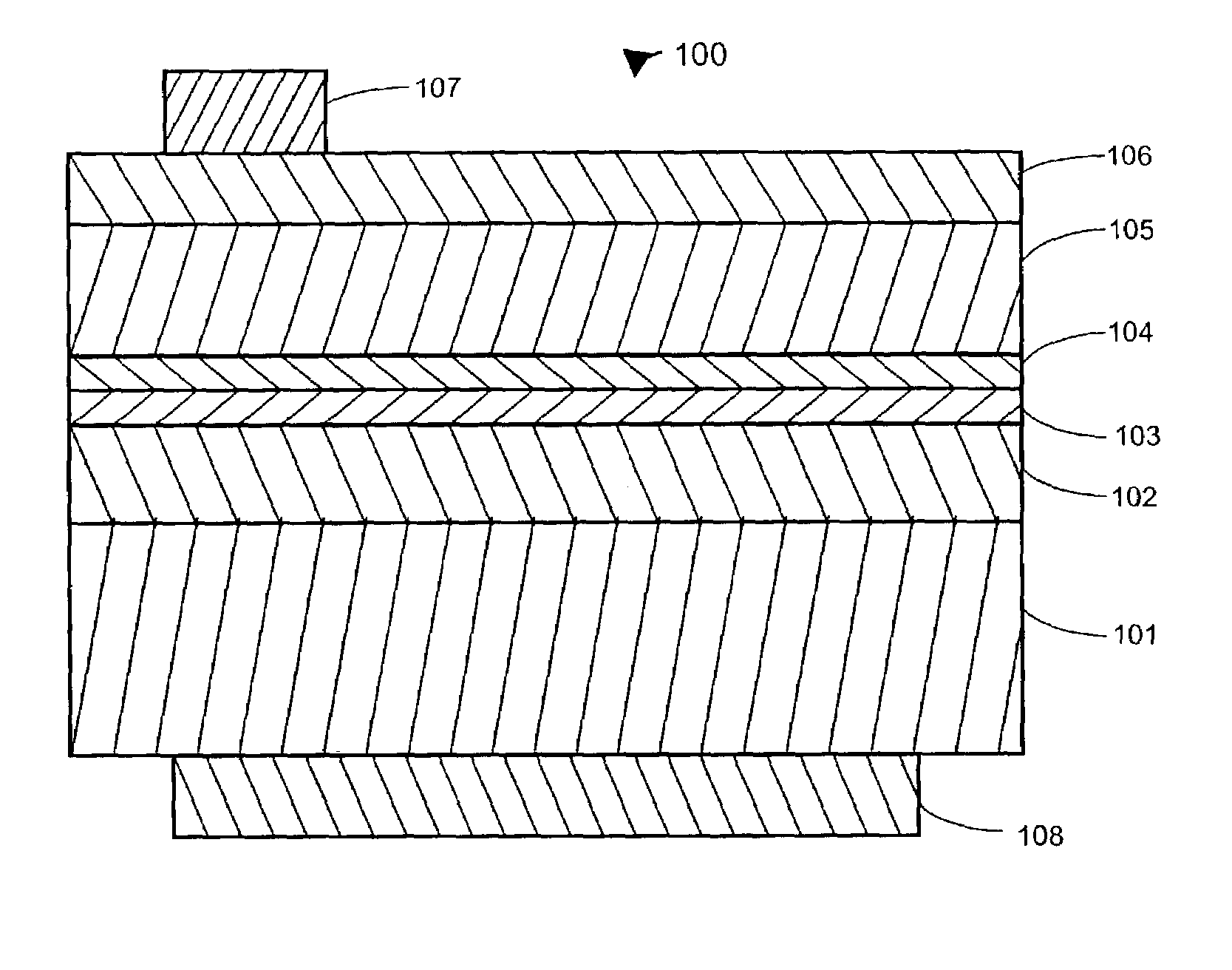

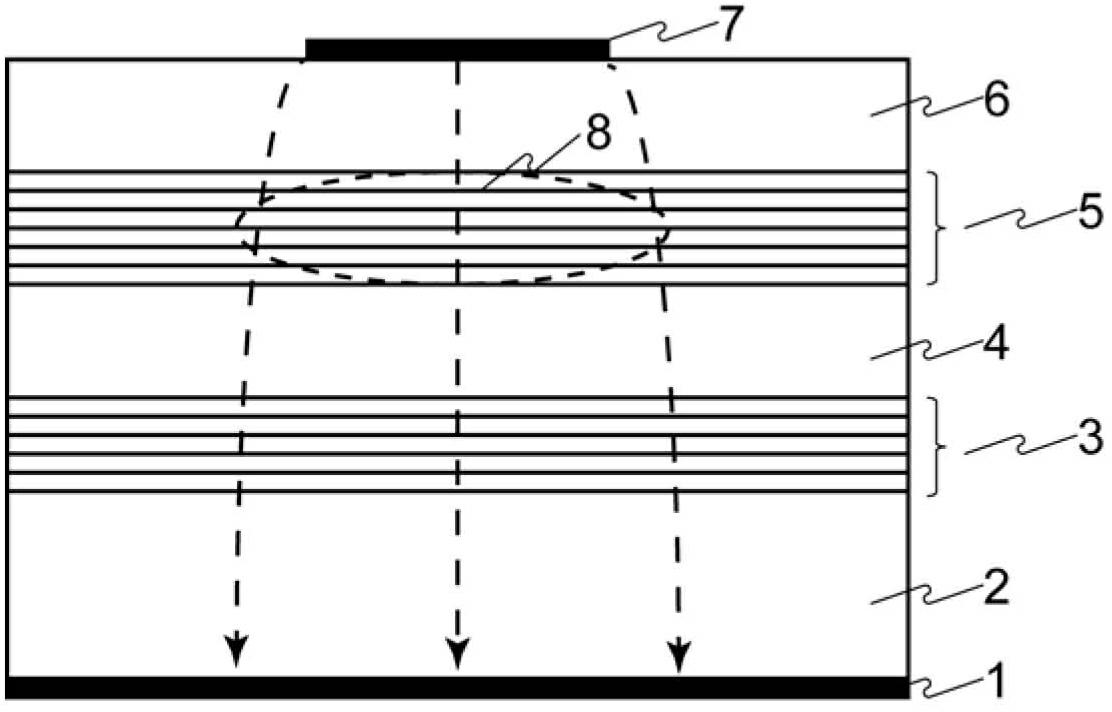

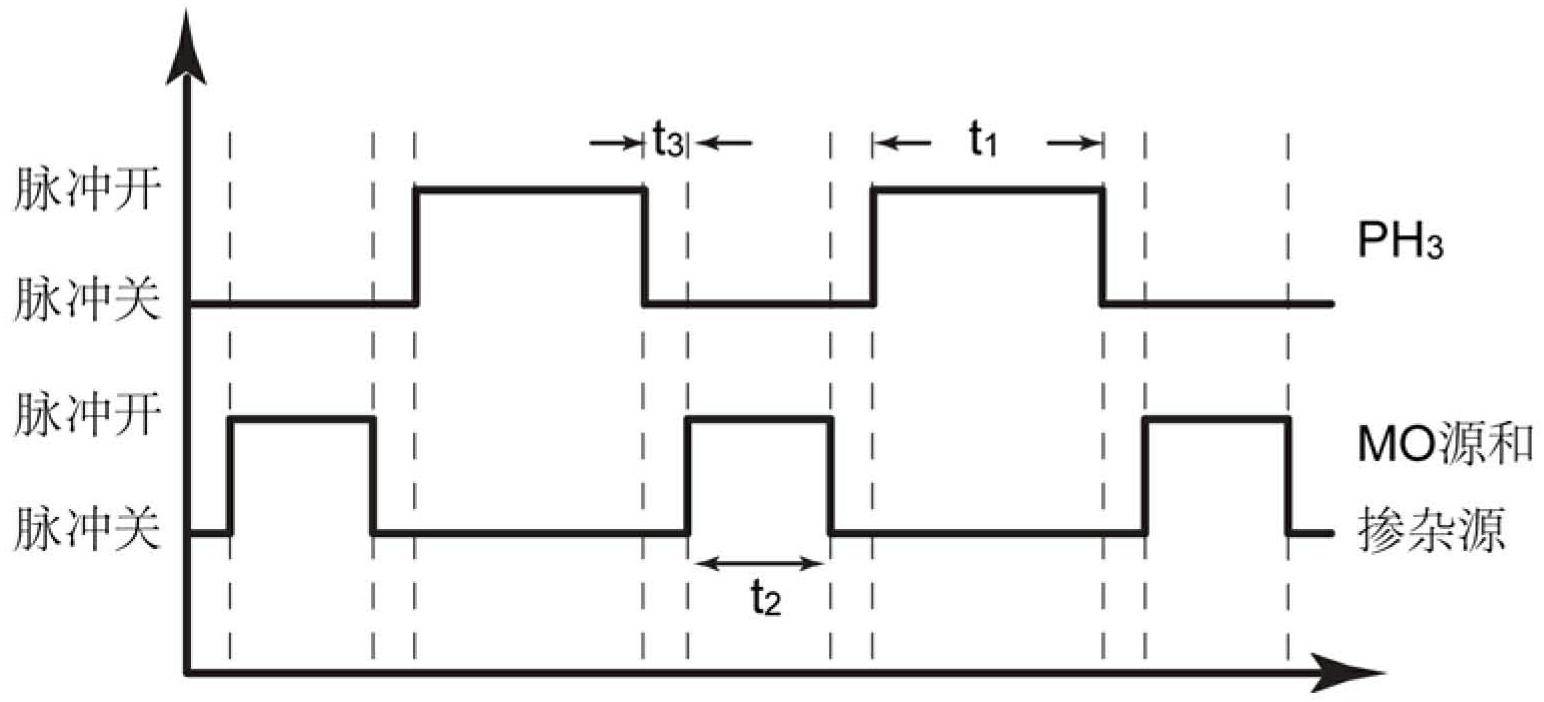

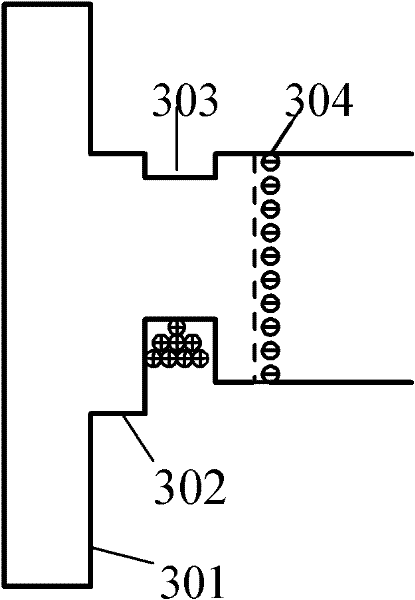

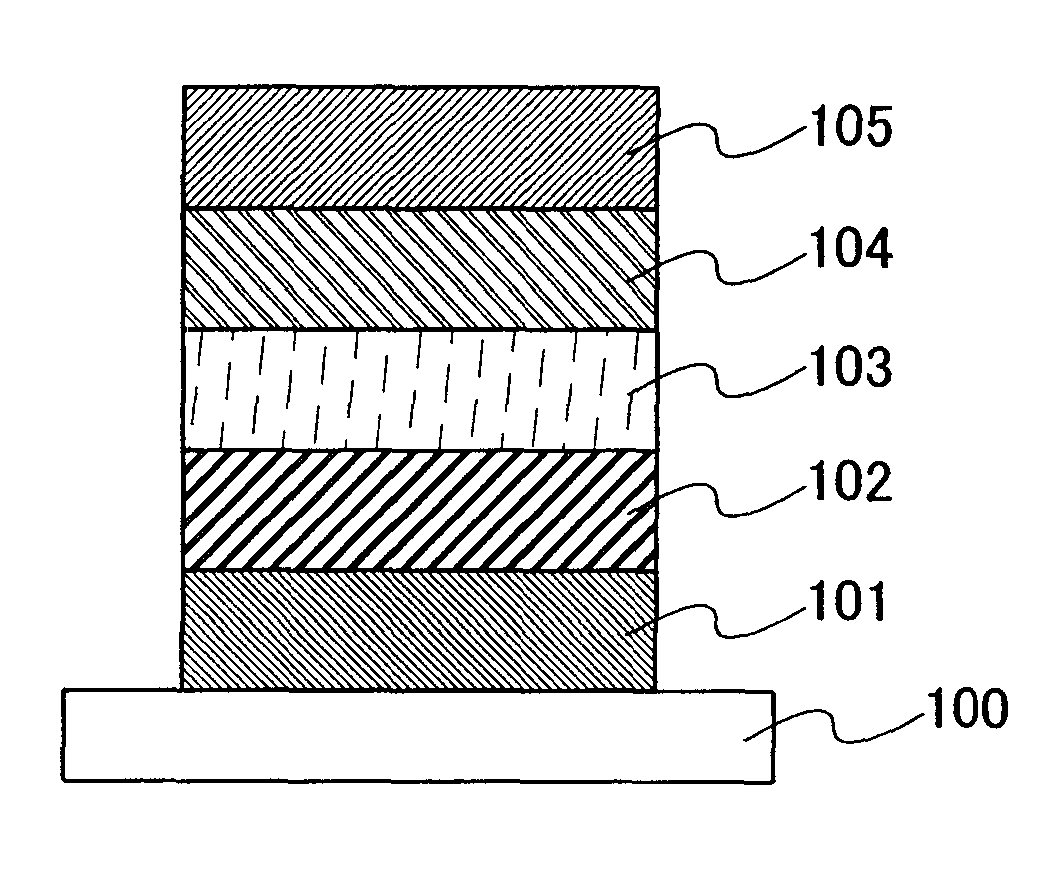

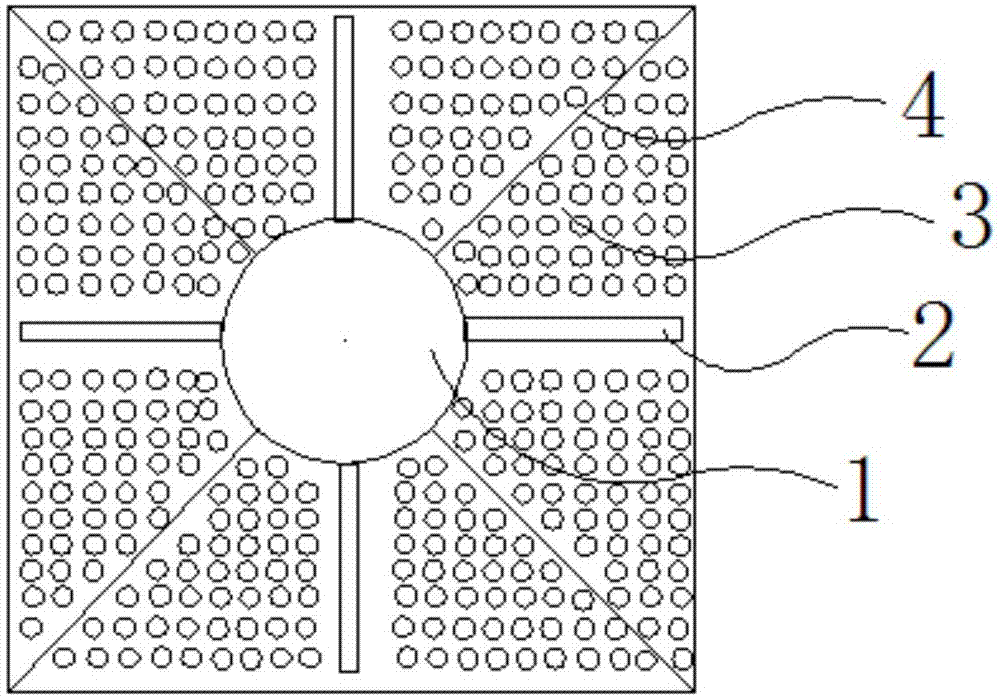

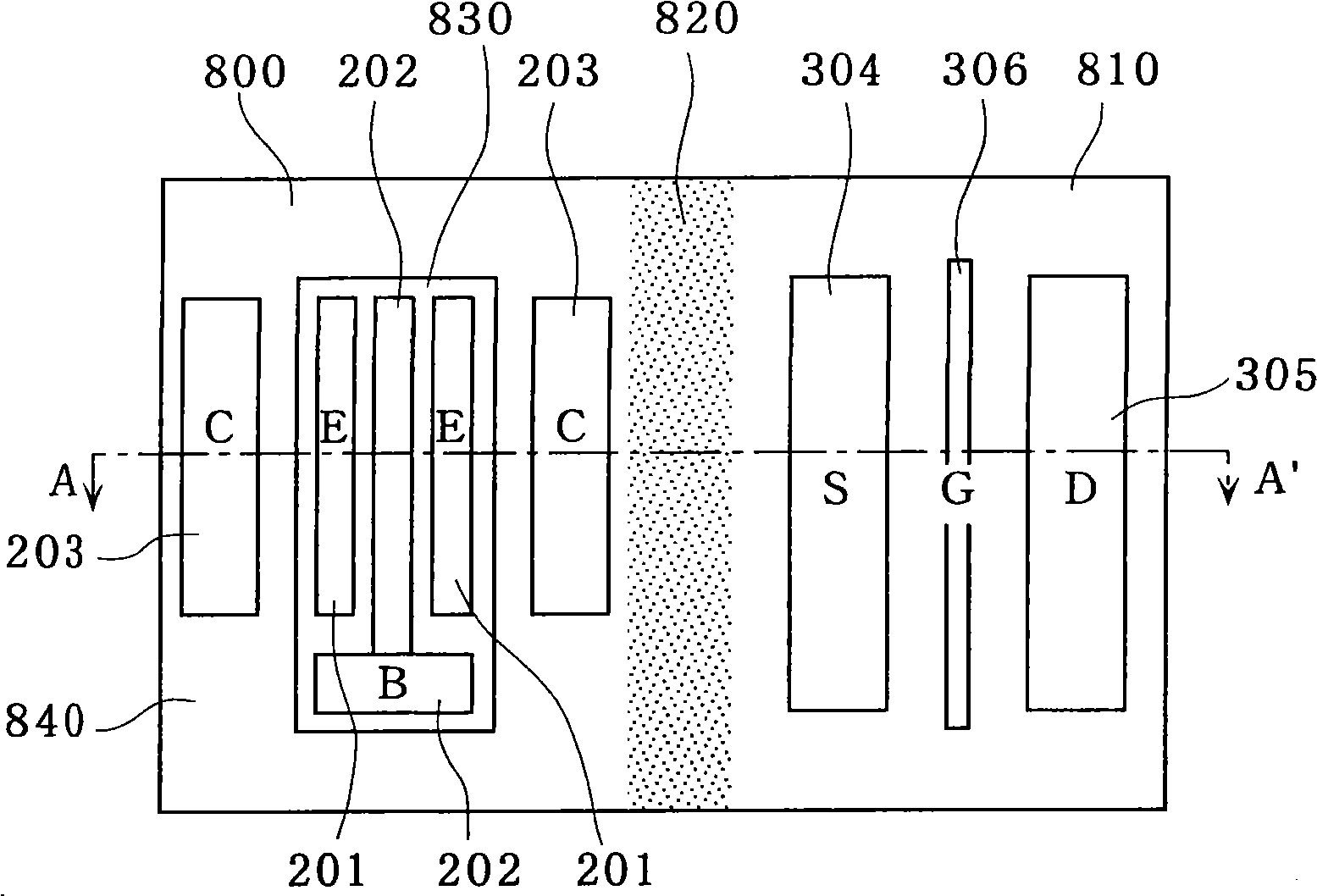

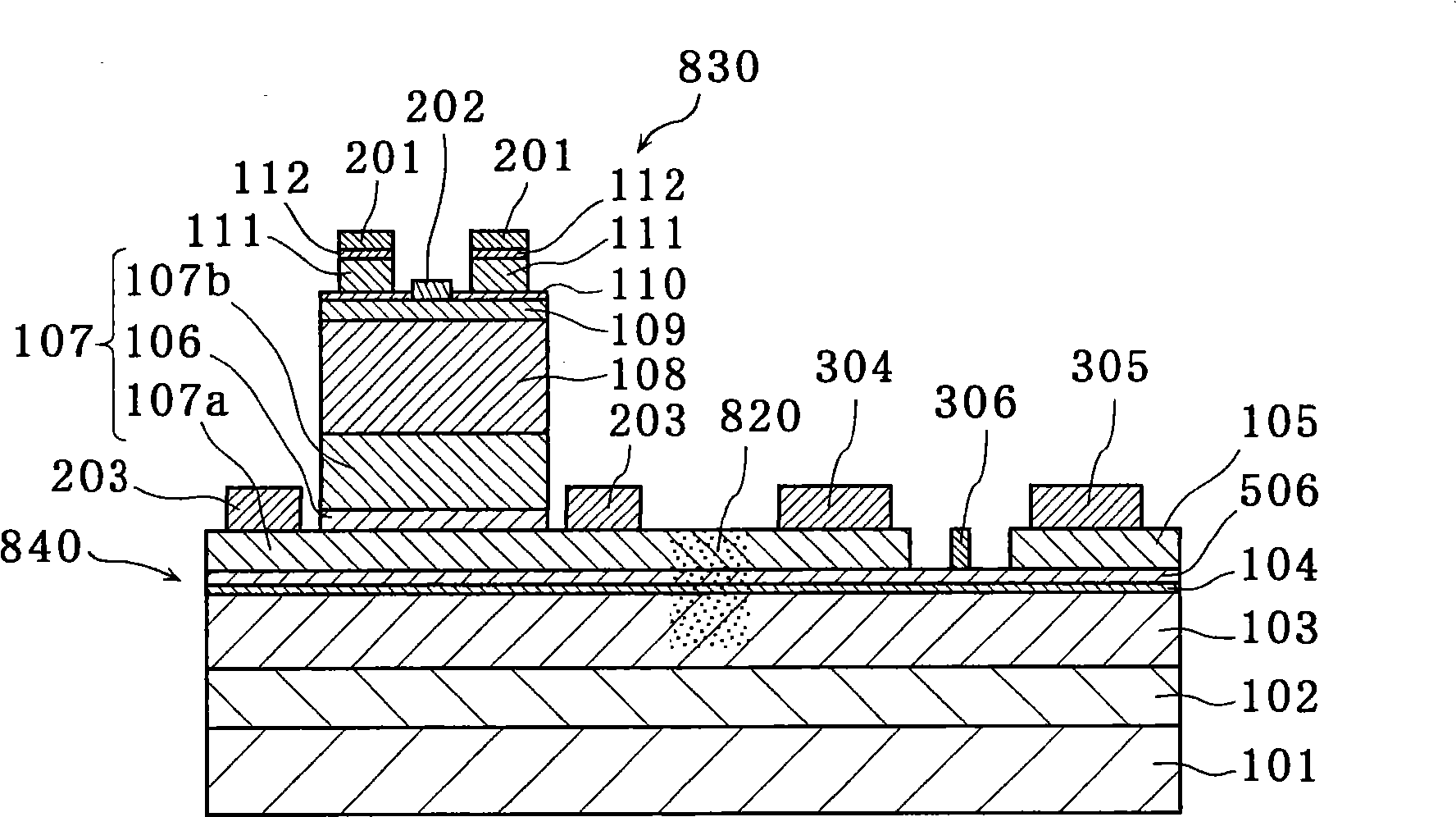

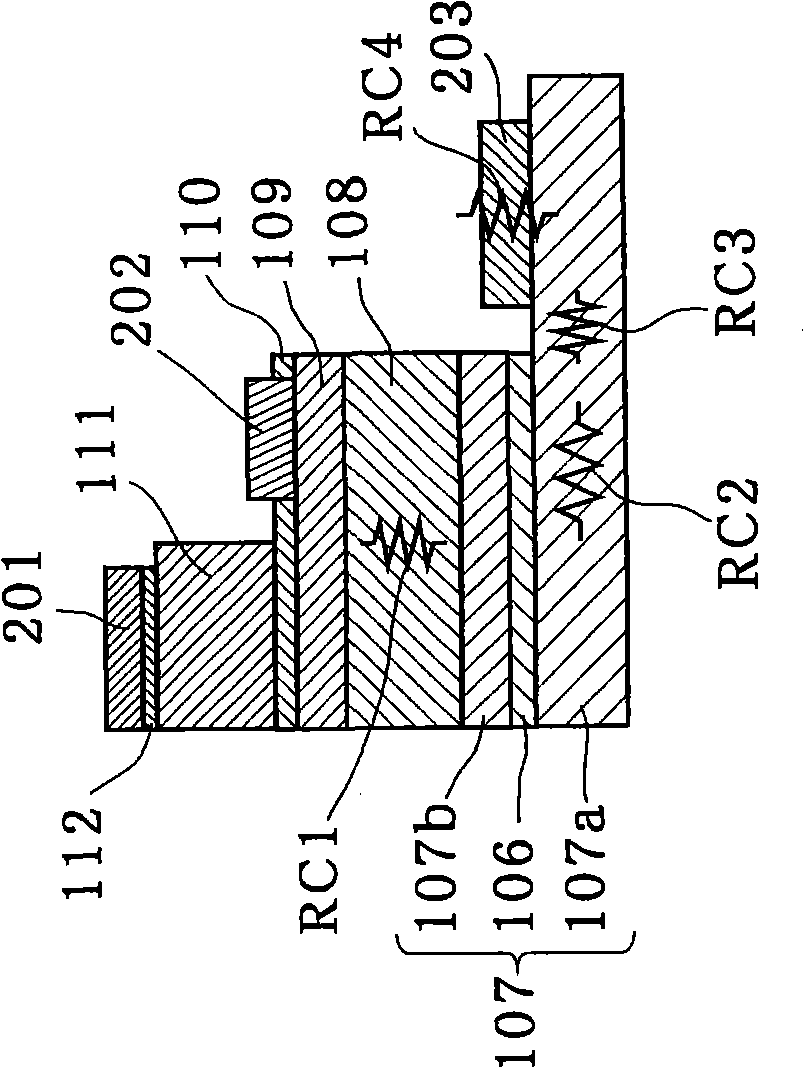

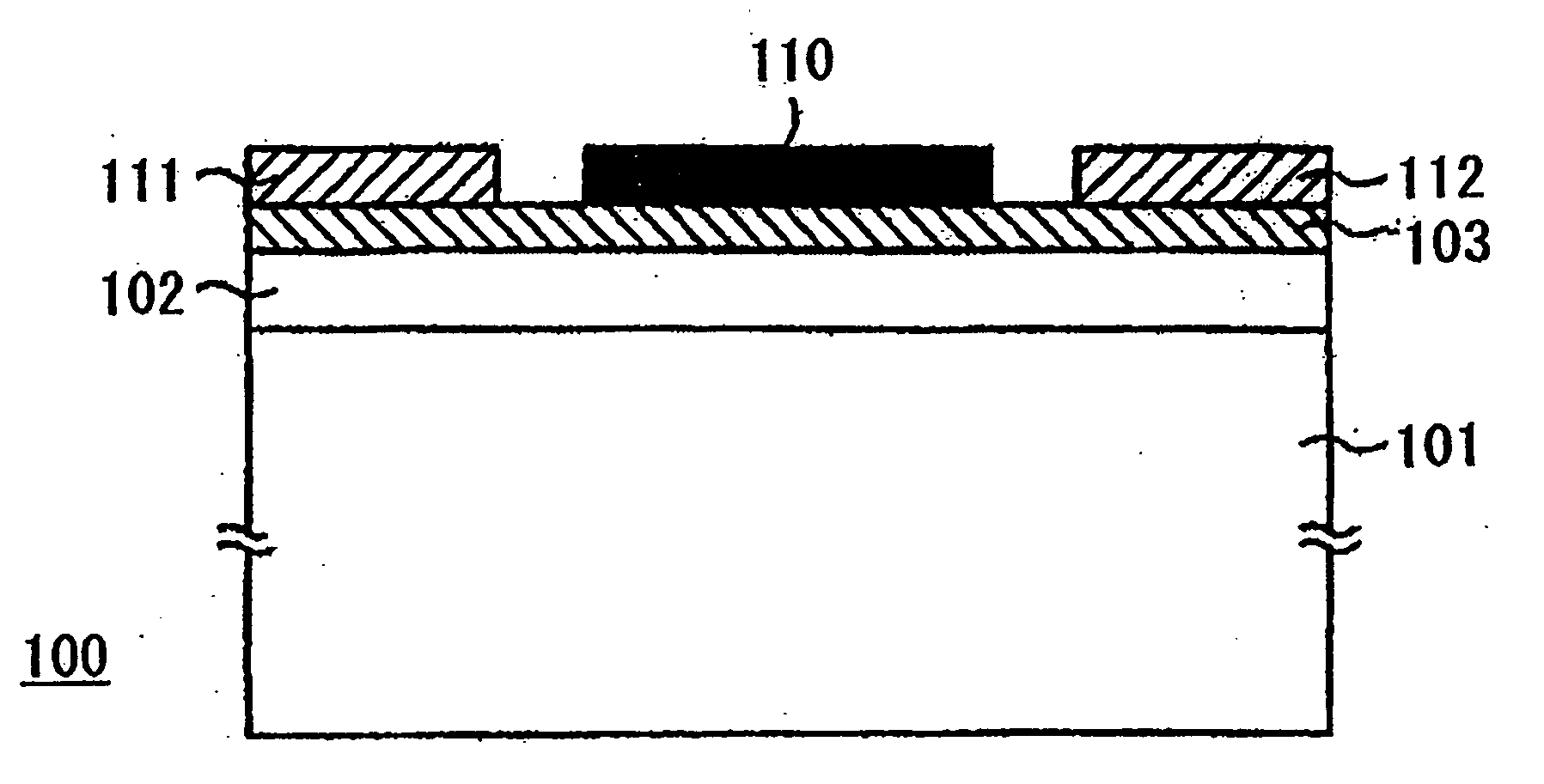

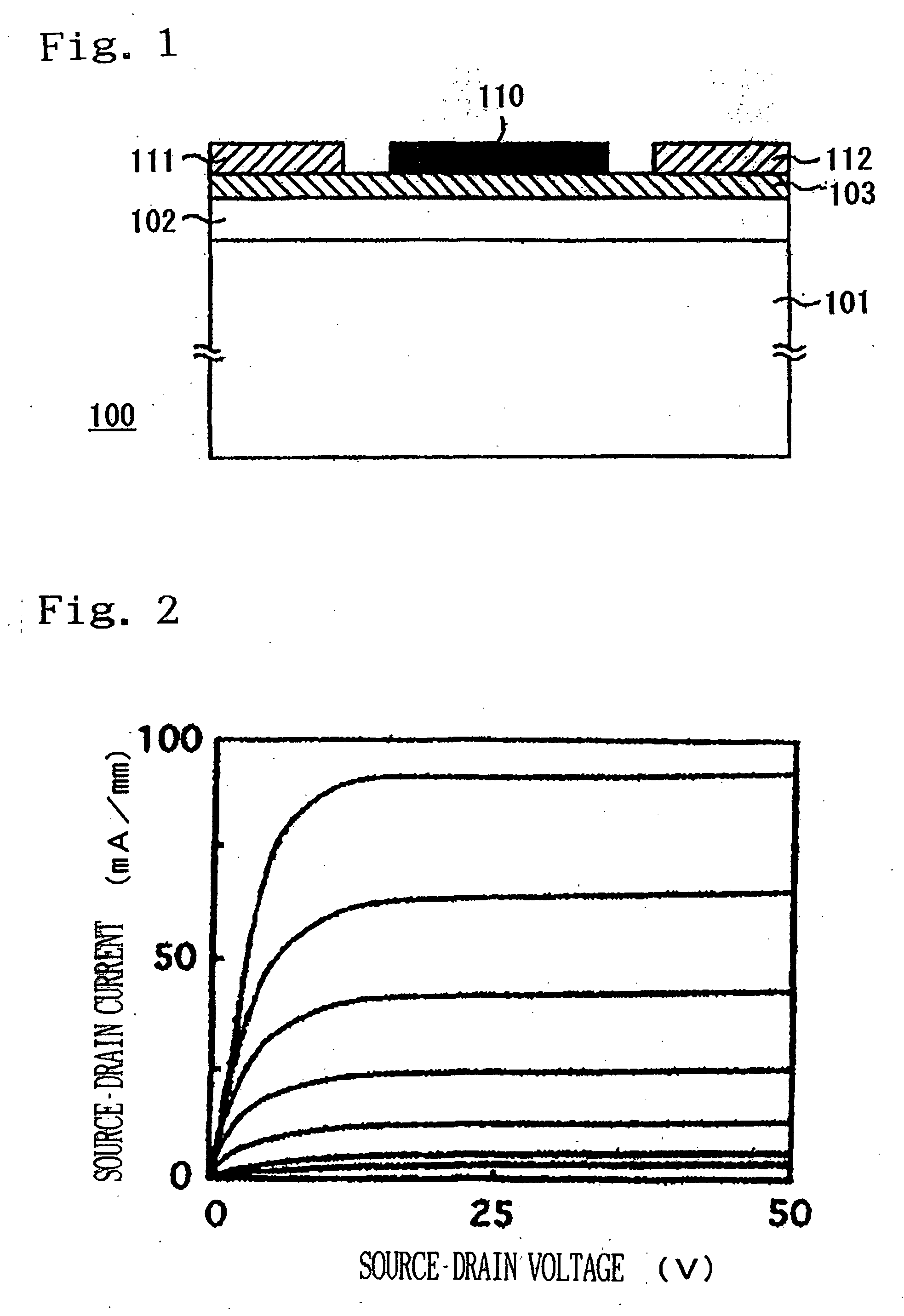

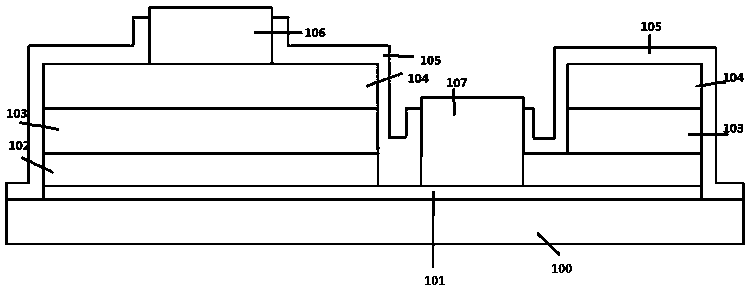

III-V family semiconductor MOS (Metal Oxide Semiconductor) interface structure

InactiveCN102244094AReduce scatterIncrease the two-dimensional electron gas concentrationSemiconductor devicesControl layerGate dielectric

The invention discloses an III-V family semiconductor MOS (Metal Oxide Semiconductor) interface structure which comprises a monocrystal substrate (101), a buffer layer (102), a quantum well bottom barrier layer (103), a high-mobility quantum well channel (104), a gallium phosphide interface control layer (105), a high-k gate dielectric (106) and a metal gate structure (107), wherein the buffer layer (102) is formed on the upper surface of the monocrystal substrate (101); the quantum well bottom barrier layer (103) is formed on the buffer layer (102); the high-mobility quantum well channel (104) is formed on the quantum well bottom barrier layer (103); the gallium phosphide interface control layer (105) is formed on the high-mobility quantum well channel (104); the high-k gate dielectric (106) is formed on the gallium phosphide interface control layer (105); and the metal gate structure (107) is formed on the high-k gate dielectric (106). The MOS (Metal Oxide Semiconductor) interface structure disclosed by the invention which adopts gallium phosphide as the interface control layer has the advantages of realizing high carrier mobility and low interface state density at the same time and meeting the requirements of a high-performance III-V family semiconductor MOS (Metal Oxide Semiconductor) technology with.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Light emitting material, light emitting element, light emitting device and electronic device

InactiveUS20070215880A1Reduce power consumptionLow costElectroluminescent light sourcesSolid-state devicesLow voltageInorganic compound

Owner:SEMICON ENERGY LAB CO LTD

Ion source and repeller structure

InactiveUS9299529B2Improve efficiencyIncrease surface areaVacuum evaporation coatingSputtering coatingEngineeringGallium nitride

A repeller structure comprises a target member configured to be sputtered by a plasma to emit given ions, and provided with a through-hole penetrating between a sputterable surface and a reverse surface thereof, and a repeller body which supports the target member while being inserted in the through-hole of the target member, and has a repeller surface exposed on the side of the sputterable surface through the through-hole. The target member is made of a material selected from the group consisting of gallium oxide, gallium nitride, gallium phosphide, gallium arsenide and gallium fluoride.

Owner:NISSIN ION EQUIP CO LTD

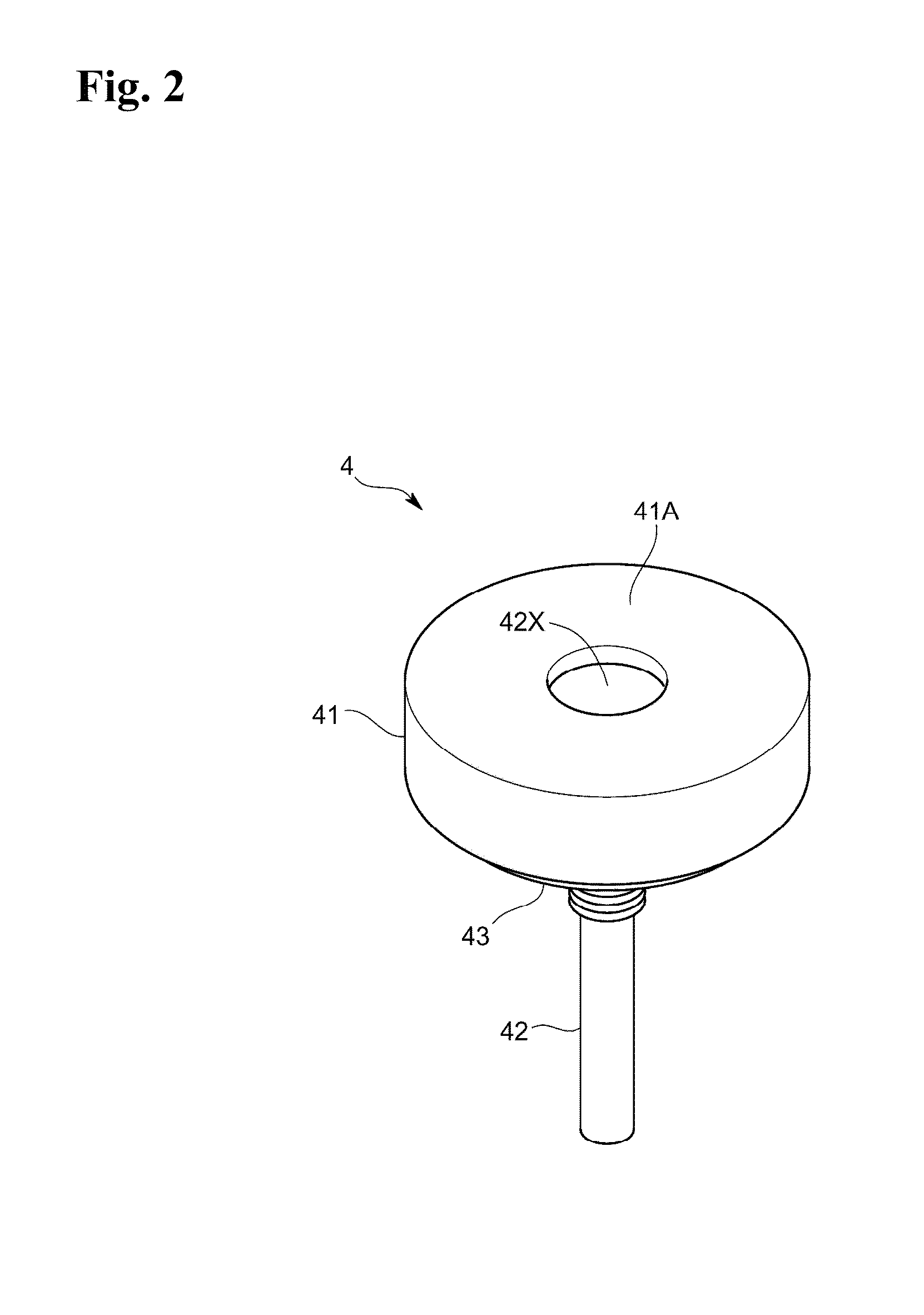

Ultraviolet nanoimprint resist and components thereof

The invention relates to an ultraviolet nanoimprint resist and components thereof, and belongs to the technical field of nanoimprint resists. The resist consists of (methyl) acrylic ester prepolymer cured by free radicals, a monomer, a photoinitiator and an assistant. The resist is suitable for the ultraviolet nanoimprint technology, and particularly suitable for the ultraviolet nanoimprint technology of spin coating. The resist is characterized in that: curing layers of the resist on substrates such as a silicon sheet, a quartz sheet, a sapphire sheet, a gallium nitride sheet, a gallium nitride indium sheet, a gallium nitride aluminum sheet, a gallium phosphide indium sheet and the like, and residual curing layers of the resist on a silicon template and a quartz template can be quickly and conveniently removed with any one of concentrated sulfuric acid, sulfuric acid / hydrogen peroxide. The residual curing layers of the resist on the silicon sheet and the quartz sheet can be conveniently cleaned by oxygen plasma. The resist also has the advantages of high coating planeness, no defect of coating layers, high curing speed, low shrinkage rate, high resolution, high etching selection ratio and the like.

Owner:SHANGHAI NANOTECH PROMOTION CENT

Aluminum diecasting alloy

An aluminum alloy suitable for diecasting of components with high elongation in the cast state contains, as well as aluminum and unavoidable impurities, 8.0 to 11.5 w. % silicon, 0.3 to 0.8 w. % manganese, 0.08 to 0.4 w. % magnesium, max 0.4 w. % iron, max 0.1 w. % copper, max 0.1 w. % zinc, max 0.15 w. % titanium and 0.05 to 0.5 w. % molybdenum. Optionally, the alloy also contains 0.05 to 0.3 w. % zirconium, 30 to 300 ppm strontium or 5 to 30 ppm sodium and / or 1 to 30 ppm calcium for permanent refinement and for grain refinement gallium phosphide and / or indium phosphide in a quantity corresponding to 1 to 250 ppm phosphorus and / or titanium and boron added by way of an aluminum master alloy with 1 to 2 w. % Ti and 1 to 2 w. % B.

Owner:АЛЮМИНИУМ РАЙНФЕЛЬДЕН ГМБХ

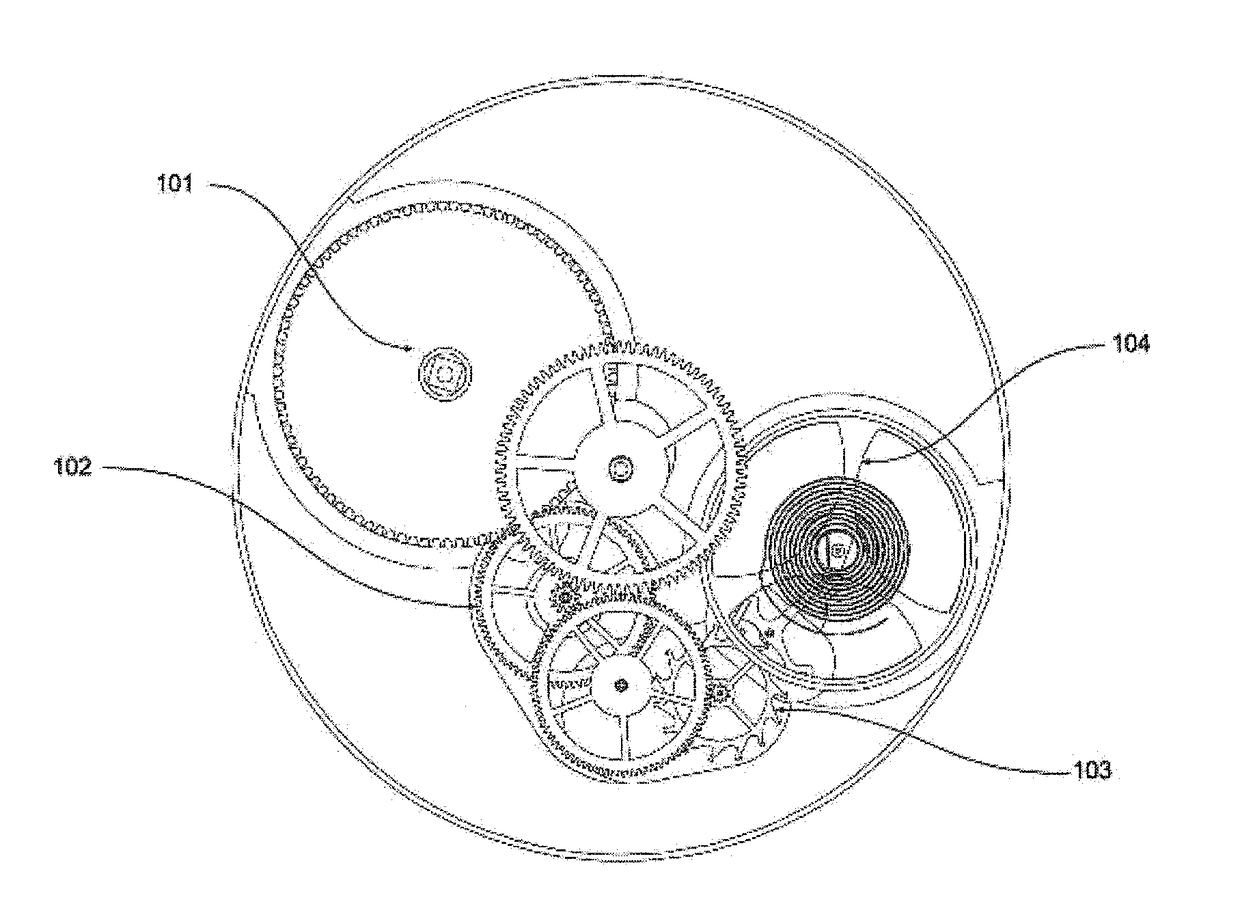

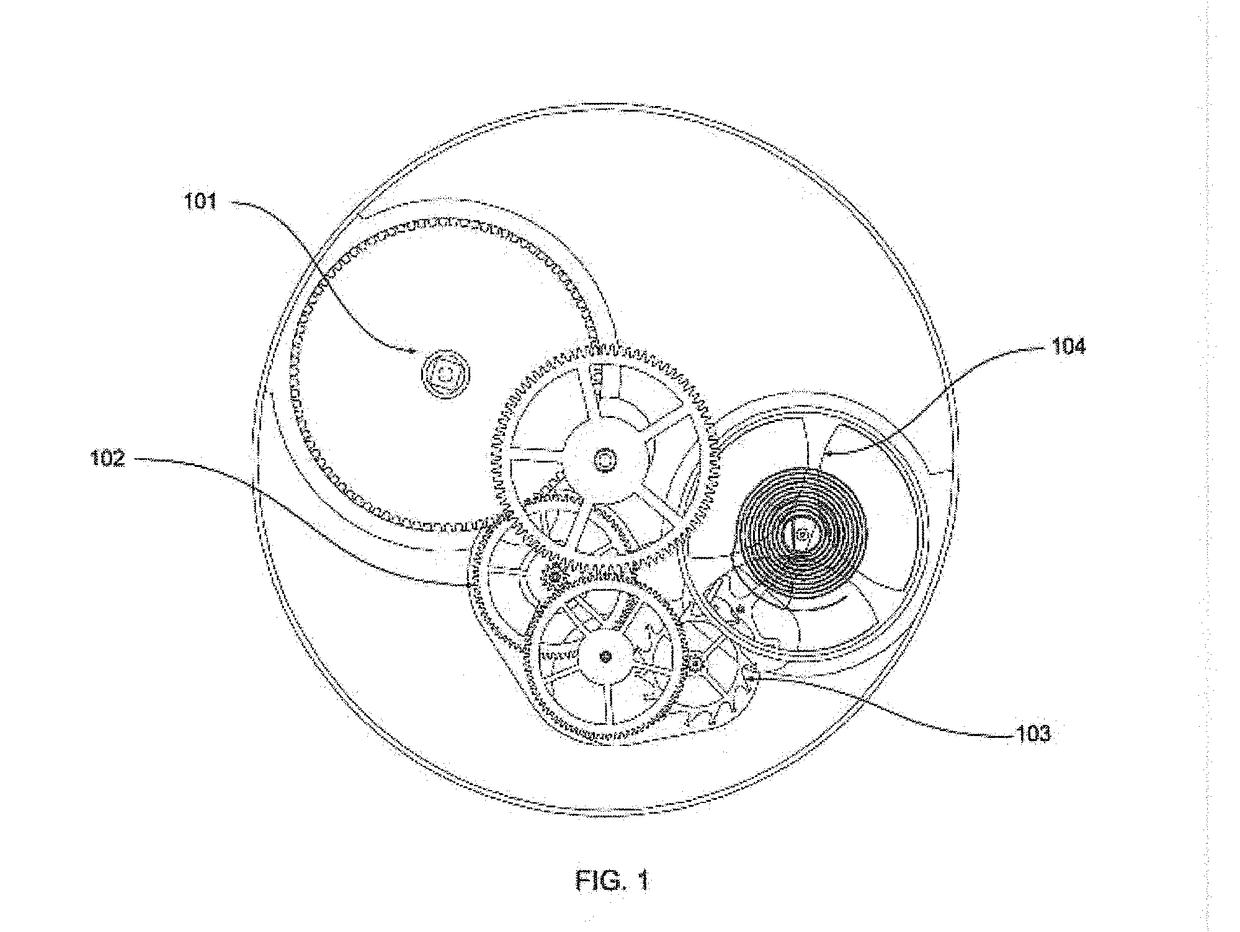

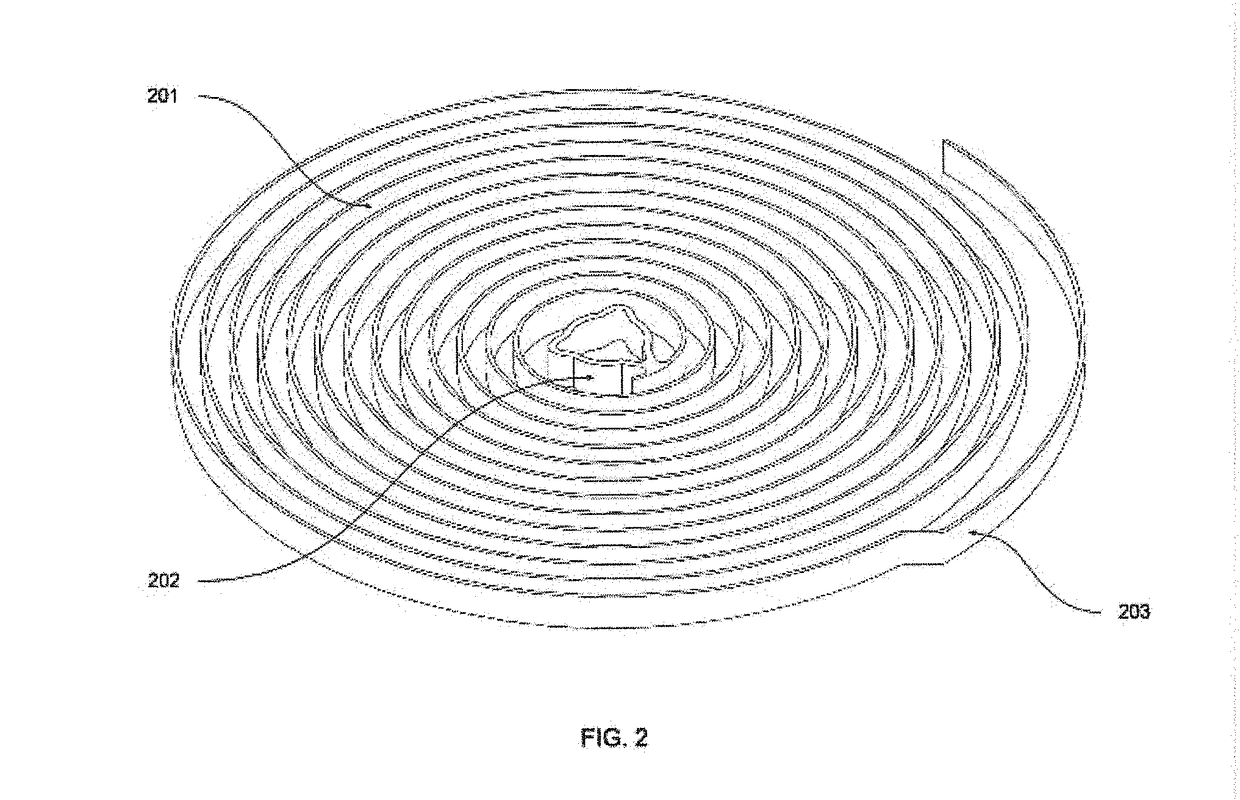

Crystalline Compounds for Use in Mechanical Watches and Methods of Manufacture Thereof

InactiveUS20170285573A1Improve performanceNeutralize effectGearworksVisual indicationEvaporationVarying thickness

This invention teaches a new class of materials that can be used to manufacture hairsprings and / or other components of mechanical watches, and methods for manufacturing these components. The new class of materials is crystalline compounds, including, but not limited to, gallium arsenide, extrinsically doped gallium arsenide, extrinsically doped silicon, gallium nitride, extrinsically doped gallium nitride, gallium phosphide, extrinsically doped gallium phosphide, and quartz. This invention also teaches laminated / coated crystalline compounds. The lamination / coating may be applied by one of the following methods, including but not limited to: plasma enhanced chemical vapor deposition, atomic layer deposition, sputtering, electron beam evaporation, and thermal evaporation. Using crystalline compounds, in particular extrinsically doping the crystalline compounds, affords the possibility to controllably alter the mechanical, electrical, thermal, magnetic, and / or other properties of the watch components. These properties can be further altered by applying single or multiple laminates / coatings of varying thicknesses and / or geometries.

Owner:FIREHOUSE HOROLOGY INC

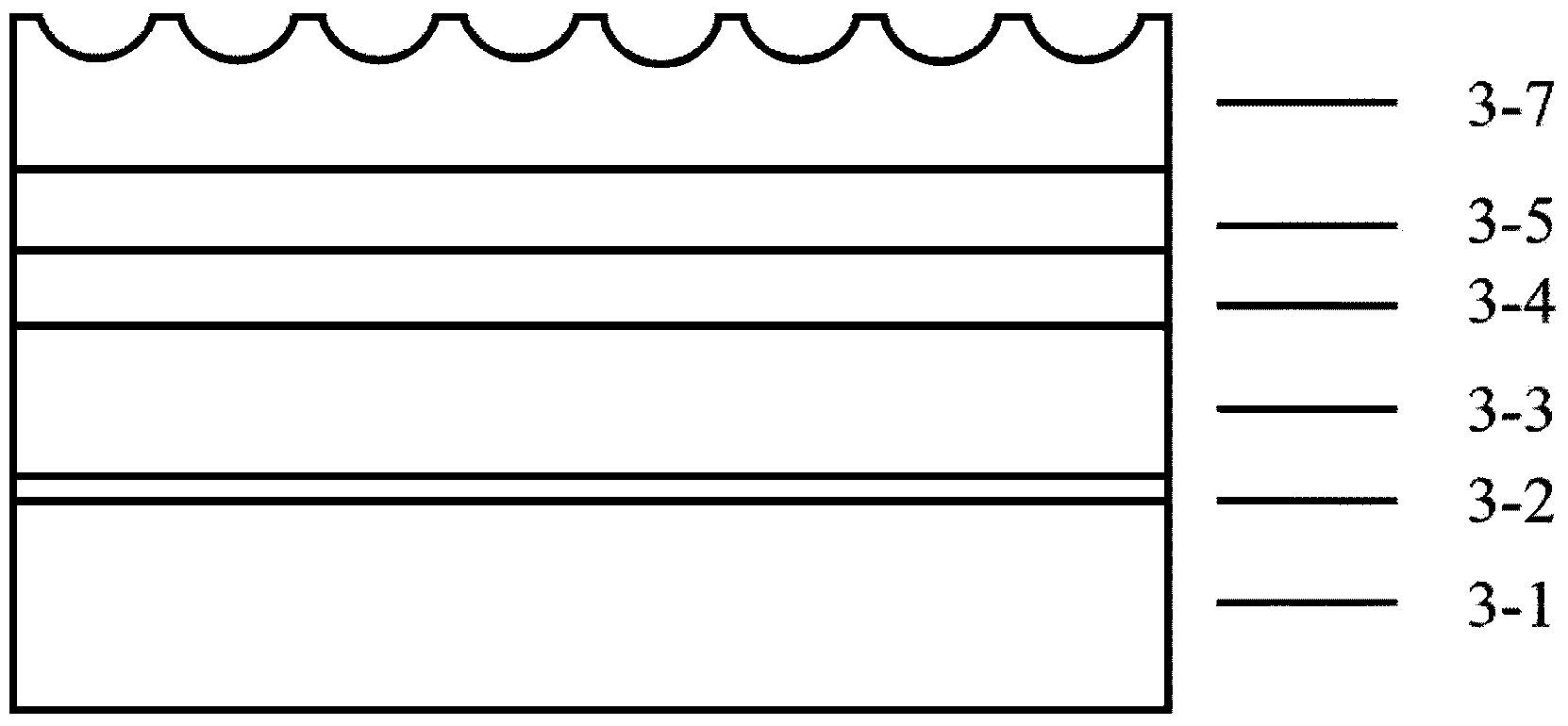

LED (light-emitting diode) chip with novel structure and production method thereof

ActiveCN103972350AImprove effective utilizationImprove luminous efficiencySemiconductor devicesIndiumEngineering

The invention discloses an LED (light-emitting diode) chip with a novel structure and a production method of the LED chip, and belongs to the field of a semiconductor device. The LED chip structure comprises an N-side electrode, a substrate, an active layer, a gallium phosphide layer, an indium-gallium-phosphorus layer, a P-side soldering wire electrode, an expanded electrode and a current barrier groove. The production method comprises the steps: growing the indium-gallium-phosphorus layer with the thickness of 1000 angstroms on a P side of a chip, etching and coarsing the gallium phosphide layer, evaporating the P-side soldering wire electrode and the expanded electrode by utilizing a vacuum film coating technology, etching the current barrier groove by virtue of plasma, and facilitating the ohm contact between the expanded electrode and the gallium phosphide layer in virtue of alloy. By adopting the produced LED chip, the current can be expanded to the entire chip surface through the expanded electrode, so that the effective application of the current is improved; meanwhile, by adopting the surface coarsing, the light emitting rate of the chip can be effectively improved. The LED chip has the advantages of simplicity in structure, simple and feasible production method and easiness in manufacturing.

Owner:马鞍山太时芯光科技有限公司

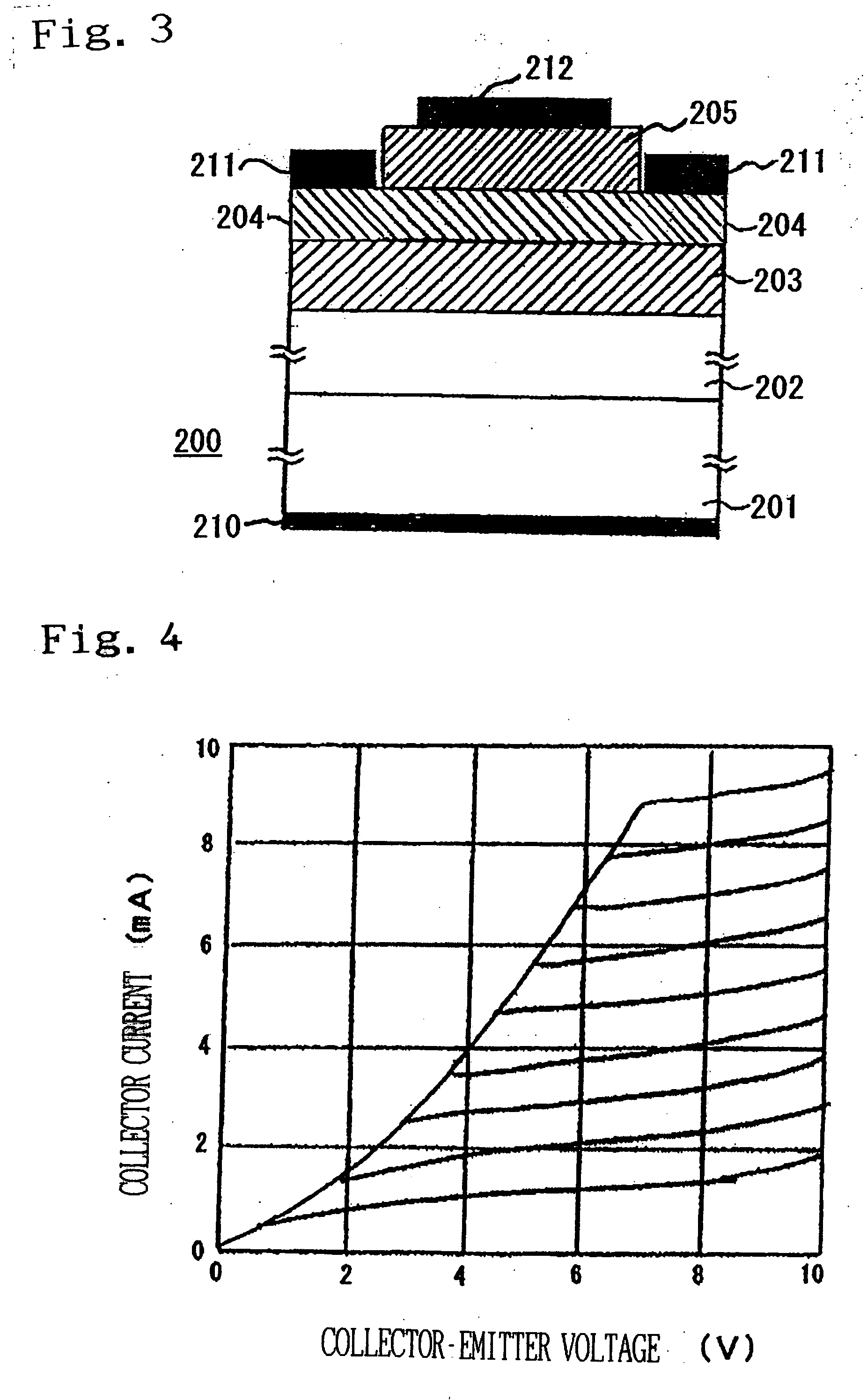

Semiconductor device and manufacturing method thereof

InactiveCN101533841AImprove performanceLower resistanceTransistorSolid-state devicesDevice materialMaterials science

The present invention has as an objective to provide: a semiconductor device to satisfy both of the trade-off characteristic advantages of the HBT; and the HFET and a manufacturing method thereof. The semiconductor device in the present invention is an HBT and HFET integrated circuit. The HBT includes a sub-collector layer, a GaAs collector layer, a GaAs base layer, and an InGaP emitter layer which are sequentially stacked. The sub-collector layer includes a GaAs external sub-collector region, and a GaAs internal sub-collector region disposed on the GaAs external sub-collector region. A mesa-shaped collector part and a collector electrode are separately formed on the GaAs external sub-collector region. The HFET includes a GaAs cap layer, a source electrode, and a drain electrode, the GaAs cap layer including portion of the GaAs external sub-collector region, and the source electrode and the drain electrode being formed on the GaAs cap layer.

Owner:PANASONIC CORP

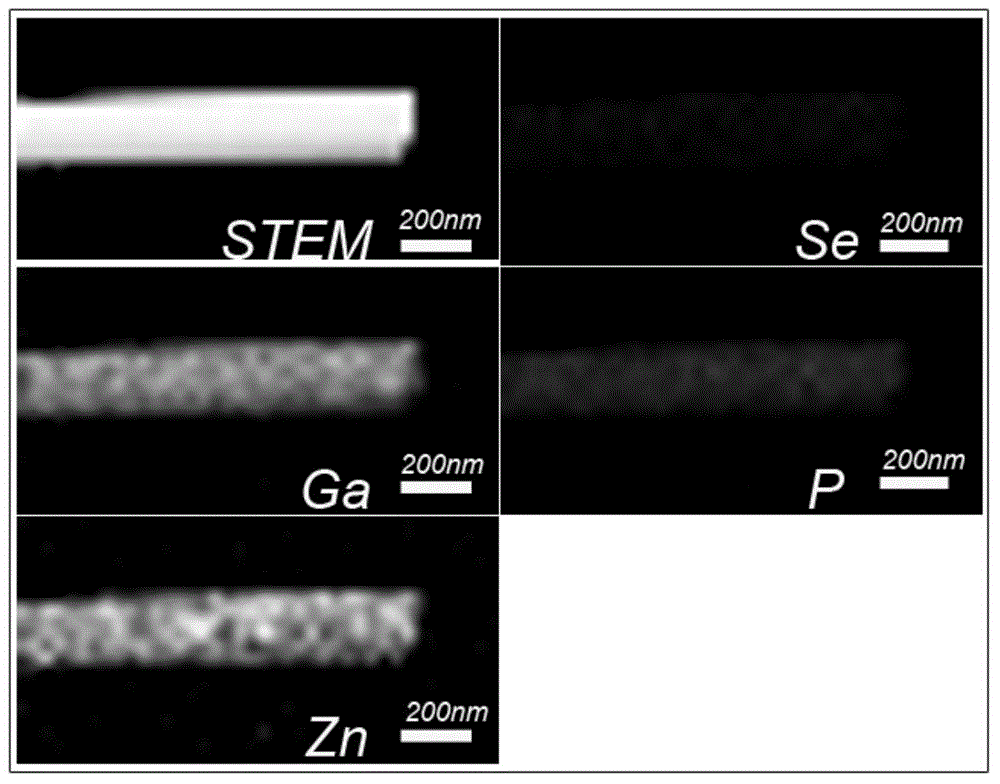

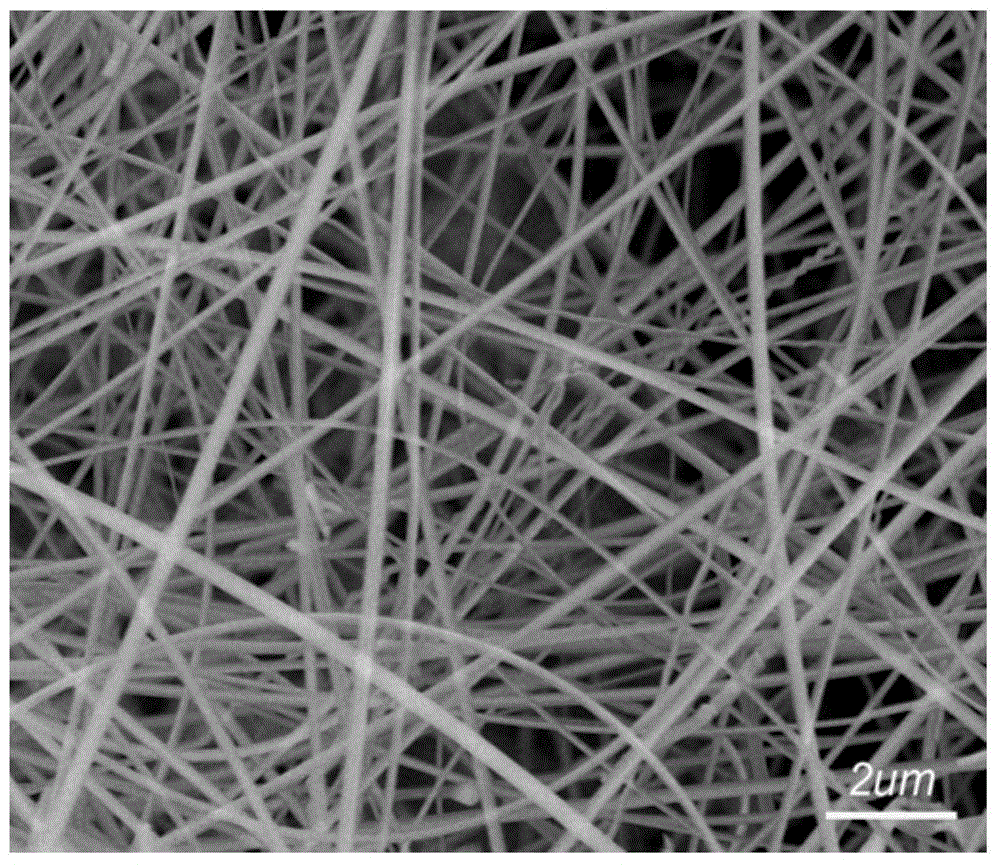

ZnSe-GaP solid solution nanometer material and preparation method thereof

ActiveCN105314608AUniform sizePromote crystallizationMaterial nanotechnologyBinary selenium/tellurium compoundsZinc selenideGraphite substrate

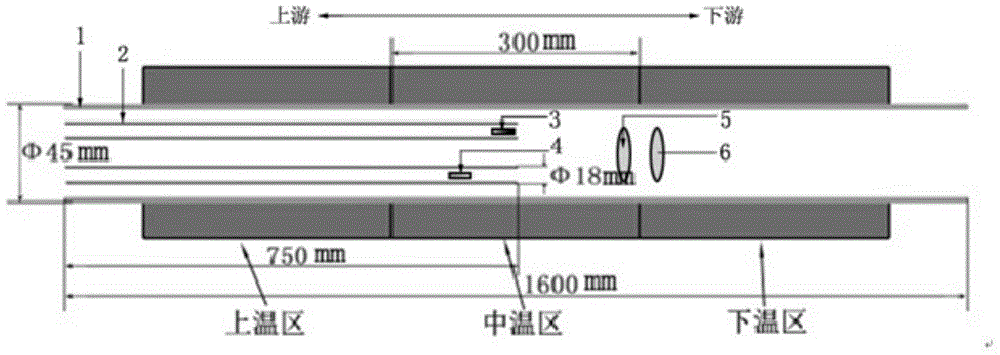

The present invention discloses a ZnSe-GaP solid solution nanometer material and a preparation method thereof. According to the present invention, the prepared ZnSe-GaP solid solution nanometer material has the linear shape, has the diameter of 50-500 nm, and has the length of 5 [mu]m-5 mm; the preparation method comprises: adding zinc selenide, gallium phosphide, selenium powder and zinc powder to a three-temperature-zone tubular furnace, and growing on a graphite substrate by using a CVD method so as to obtain the ZnSe-GaP solid solution nanometer material; and the prepared ZnSe-GaP solid solution nanometer material has characteristics of good crystal, large aspect ratio and uniform size, and the preparation method has characteristics of simple process, easy process parameter control and simple operation, is suitable for large area preparation, and is used for preparation of nanometer optoelectronic devices.

Owner:INST OF METAL RESEARCH - CHINESE ACAD OF SCI

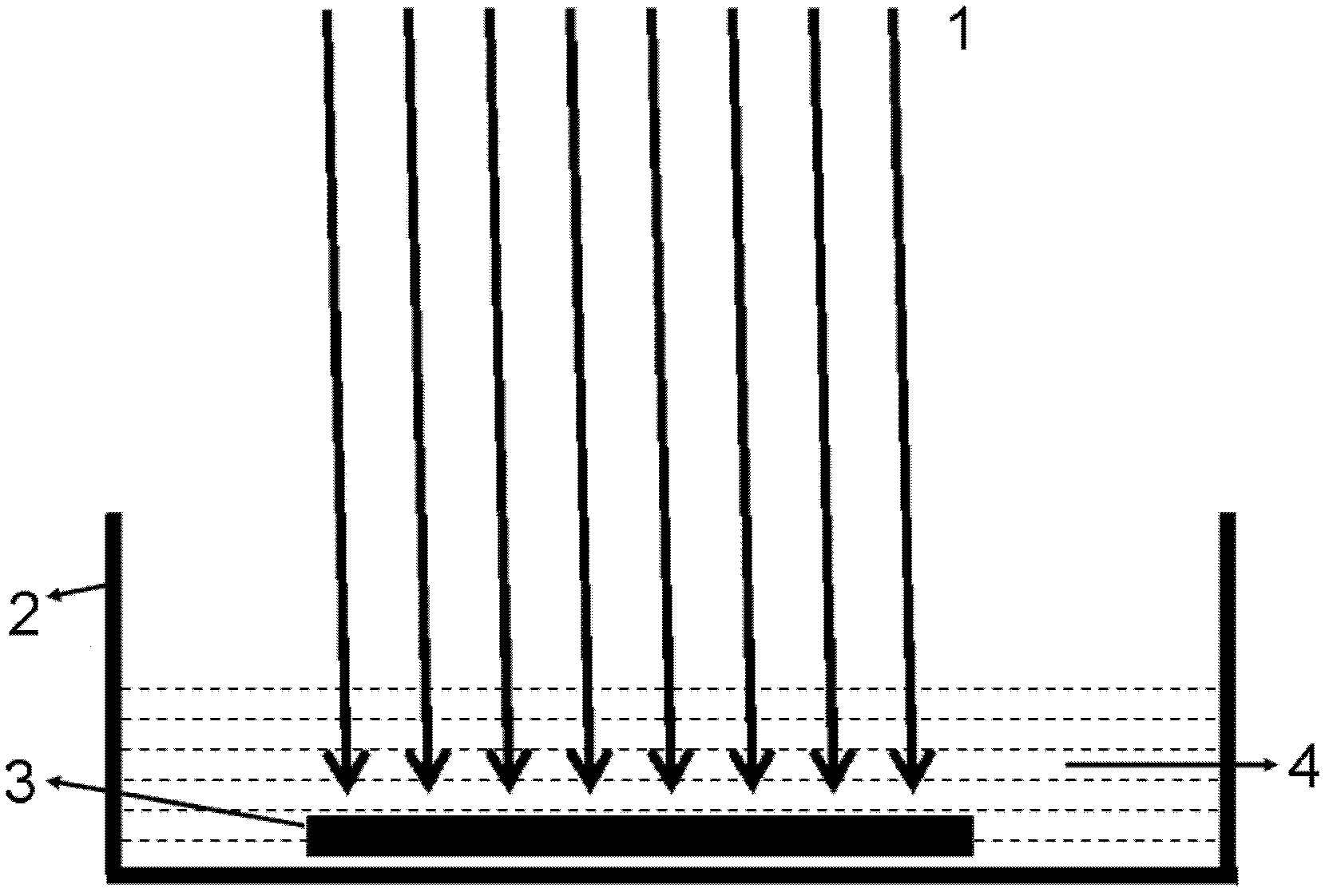

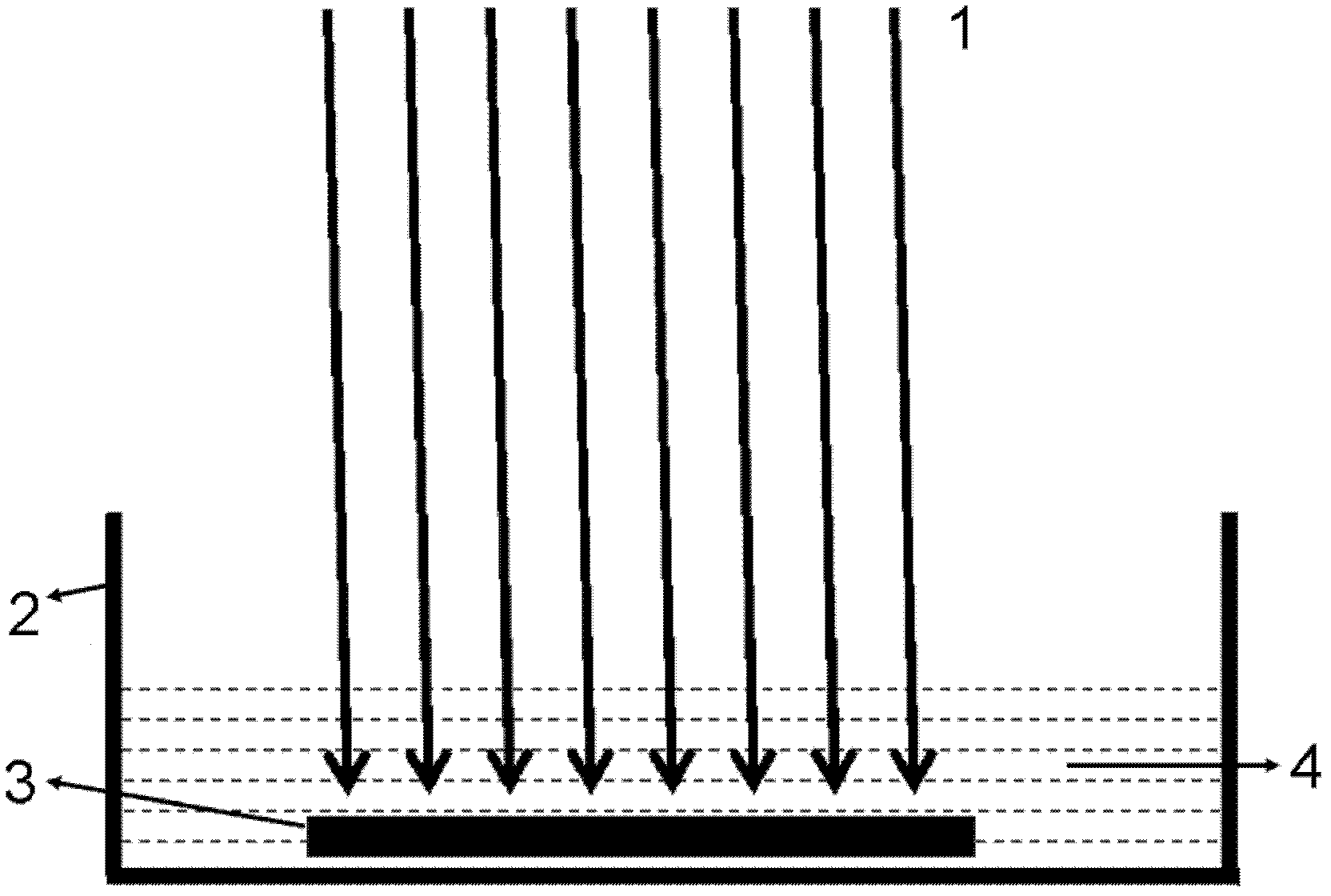

A method for wet roughening of gallium phosphide window layer of light-assisted red LED

InactiveCN102280536ASimple and fast operationLow costSemiconductor devicesHydrofluoric acidPhoto assisted

The invention, which belongs to the LED technology field, relates to a coarsening method of a wet method of a gallium phosphide window layer of a photo-assisted red light LED. A mixed solution of hydrofluoric acid and an oxidizing agent is utilized and light irradiation is utilized; a gallium phosphide window layer can be corroded without a mask layer and a conical composition array is obtained, so that a surface coarsening of the red light LED is realized. A size and a height of the conical composition caused by corrosion can be controlled by controlling corrosion time and a concentration ofcorrosive liquid. According to the invention, a problem of coarsening of the gallium phosphide window layer of the red light LED can be effectively solved and an extraction efficiency of a red light LED chip can be improved more than double. The method has advantages of good coarsening effect, low cost and rapid speed and the like and thus has great application potential in production of a large power red light LED.

Owner:SHANDONG UNIV

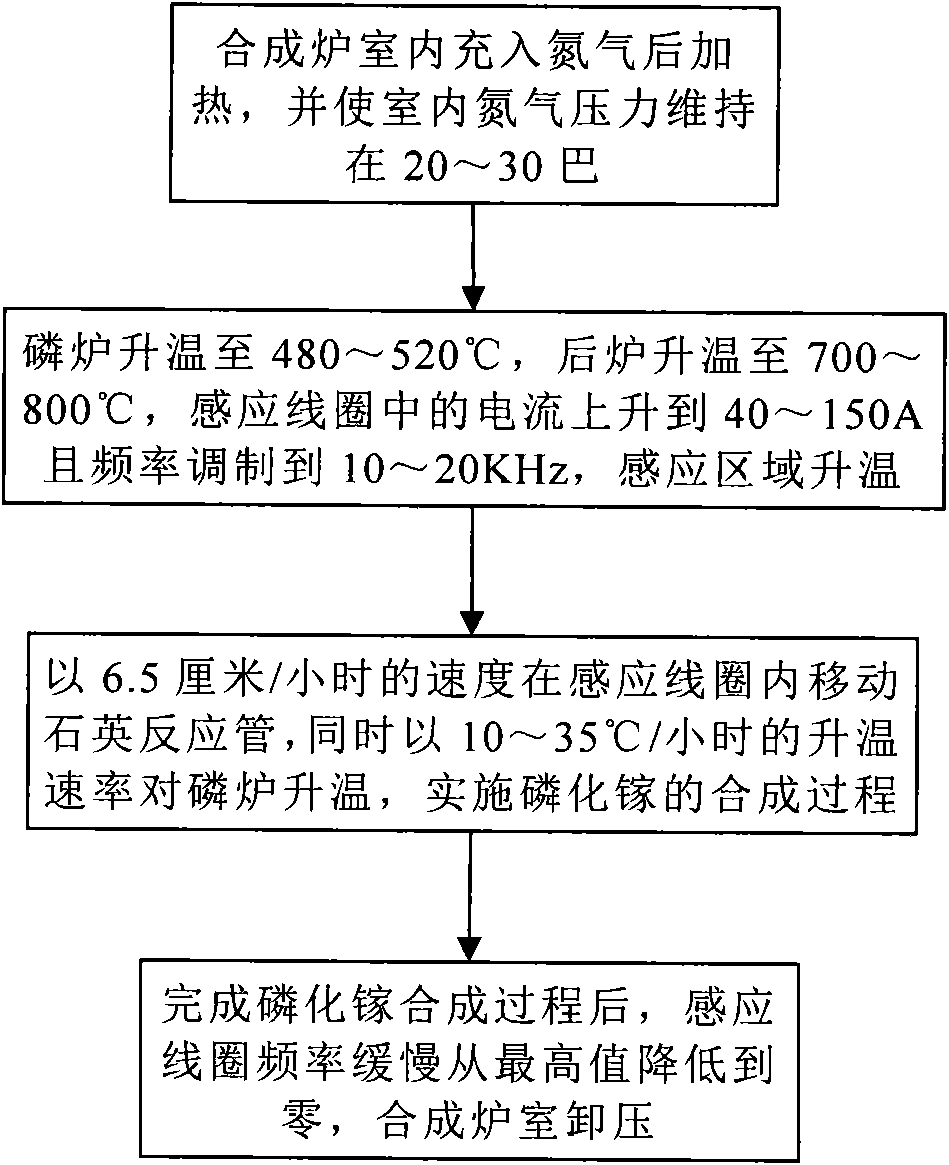

Method for synthesizing gallium phosphide polycrystal

ActiveCN101660207AReduce the number of tube explosionsHigh yieldPolycrystalline material growthSingle crystal growth detailsElectromagnetic radiationNitrogen gas

The invention discloses a method for synthesizing a gallium phosphide polycrystal, which comprises the following steps of: charging nitrogen into a chamber of a synthetic furnace, heating, and maintaining a nitrogen pressure in the furnace to between 20 and 30 bar; raising the temperature of a phosphorus furnace to between 480 and 520 DEG C, raising the temperature of the furnace to between 700 and 800 DEG C, increasing the current in an induction coil to between 40 and 150 A, modulating the frequency to between 10 and 20 KHz and raising the temperature of an induction area; and moving a quartz tube reactor in the induction coil at a speed of 6.5cm / h, simultaneously raising the temperature of the phosphorus furnace at a speed of 10 to 35 DEG C / h and performing a gallium phosphide synthesizing process. After the gallium phosphide synthesizing process is completed, the frequency of the induction coil is slowly reduced to zero from the highest value and then the pressure of the syntheticfurnace is released. By adopting a medium high-frequency heating way to synthesize the gallium phosphide, the method for synthesizing the gallium phosphide polycrystal greatly decreases tube explodingtimes in the gallium phosphide polycrystal synthesizing process, improves the yield and quality of the gallium phosphide polycrystal and does not easily generate an electrode spark phenomenon and strong electromagnetic radiation, thereby avoiding affecting the health of human bodies.

Owner:GRINM GUOJINGHUI NEW MATERIALS CO LTD

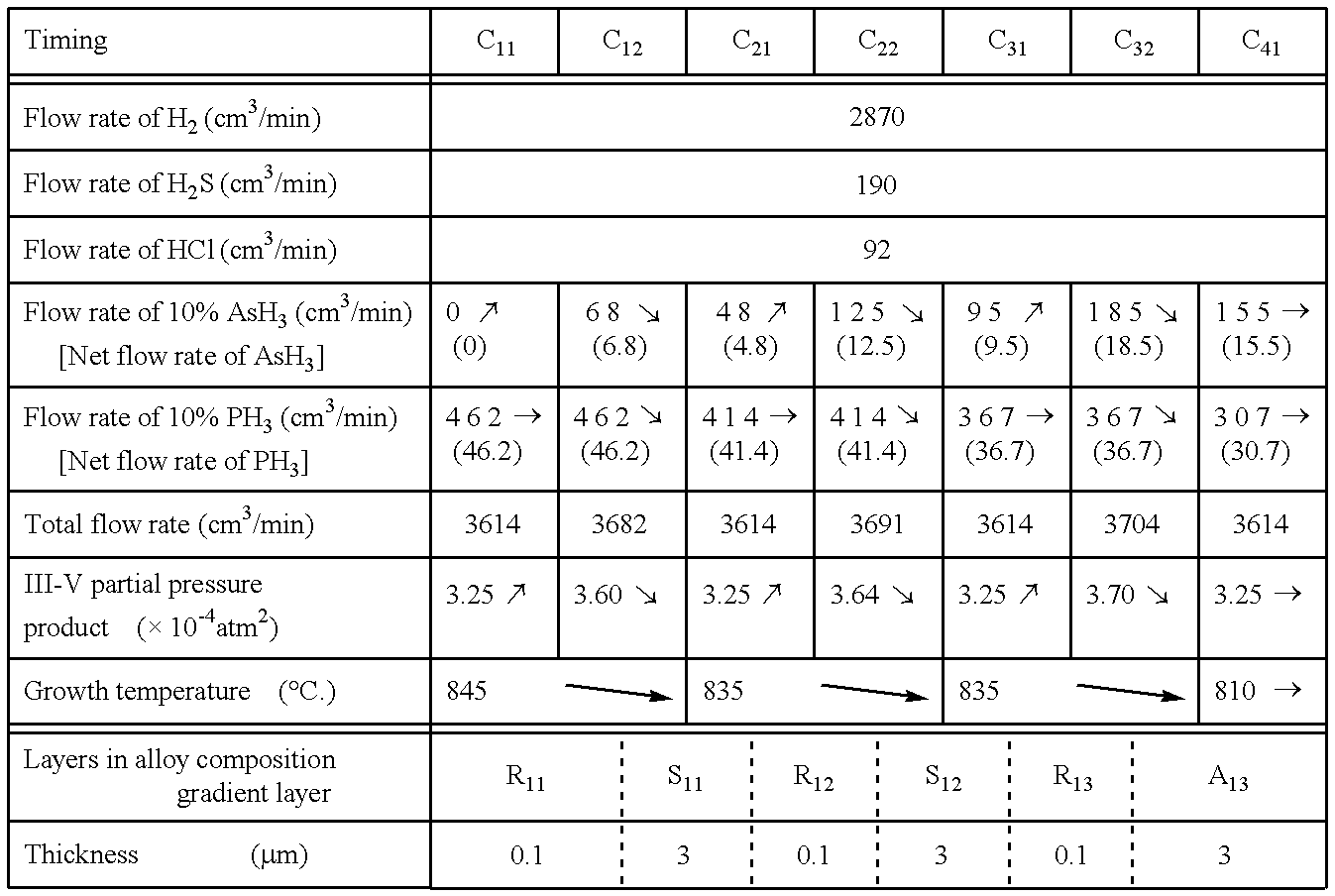

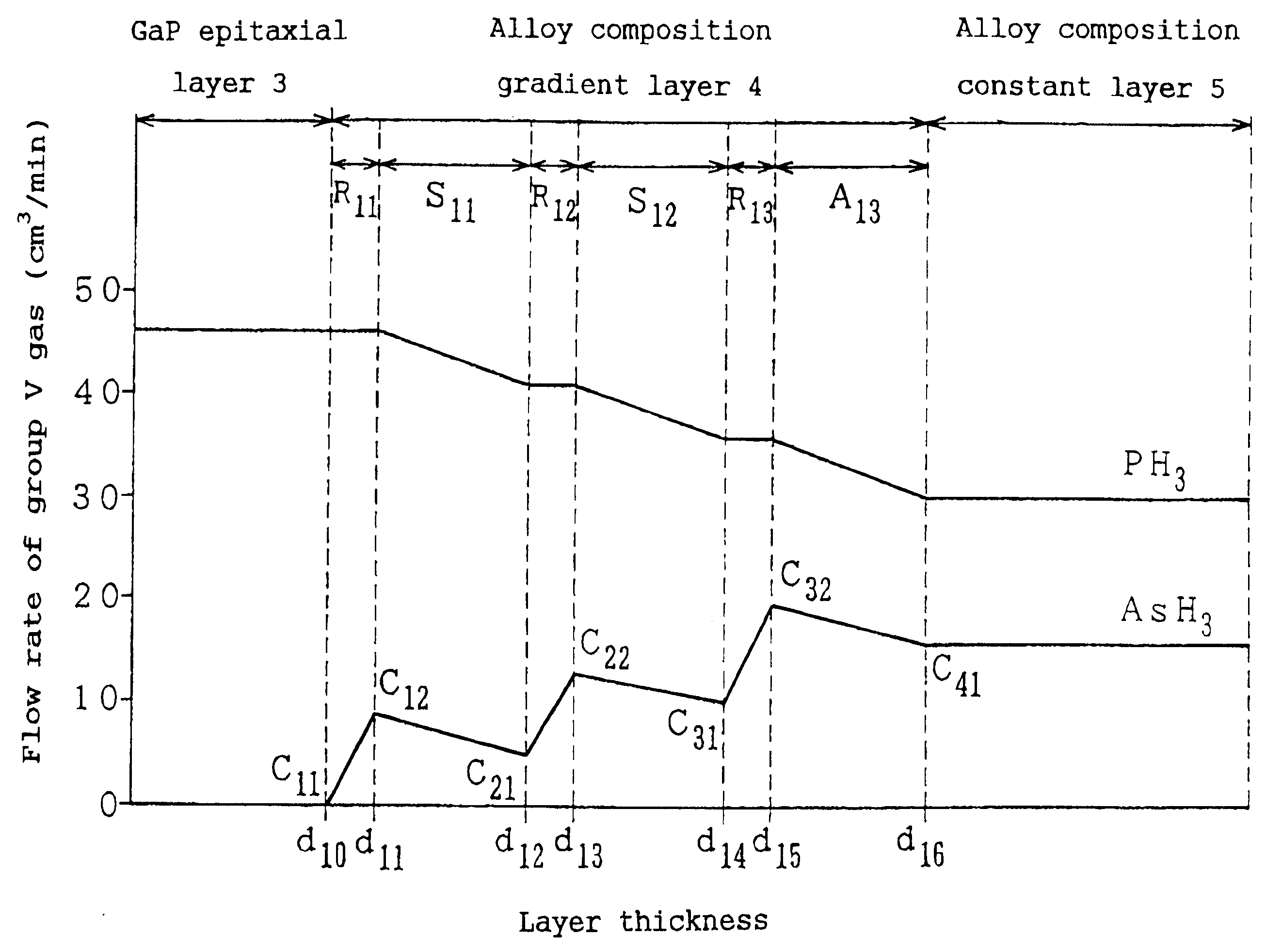

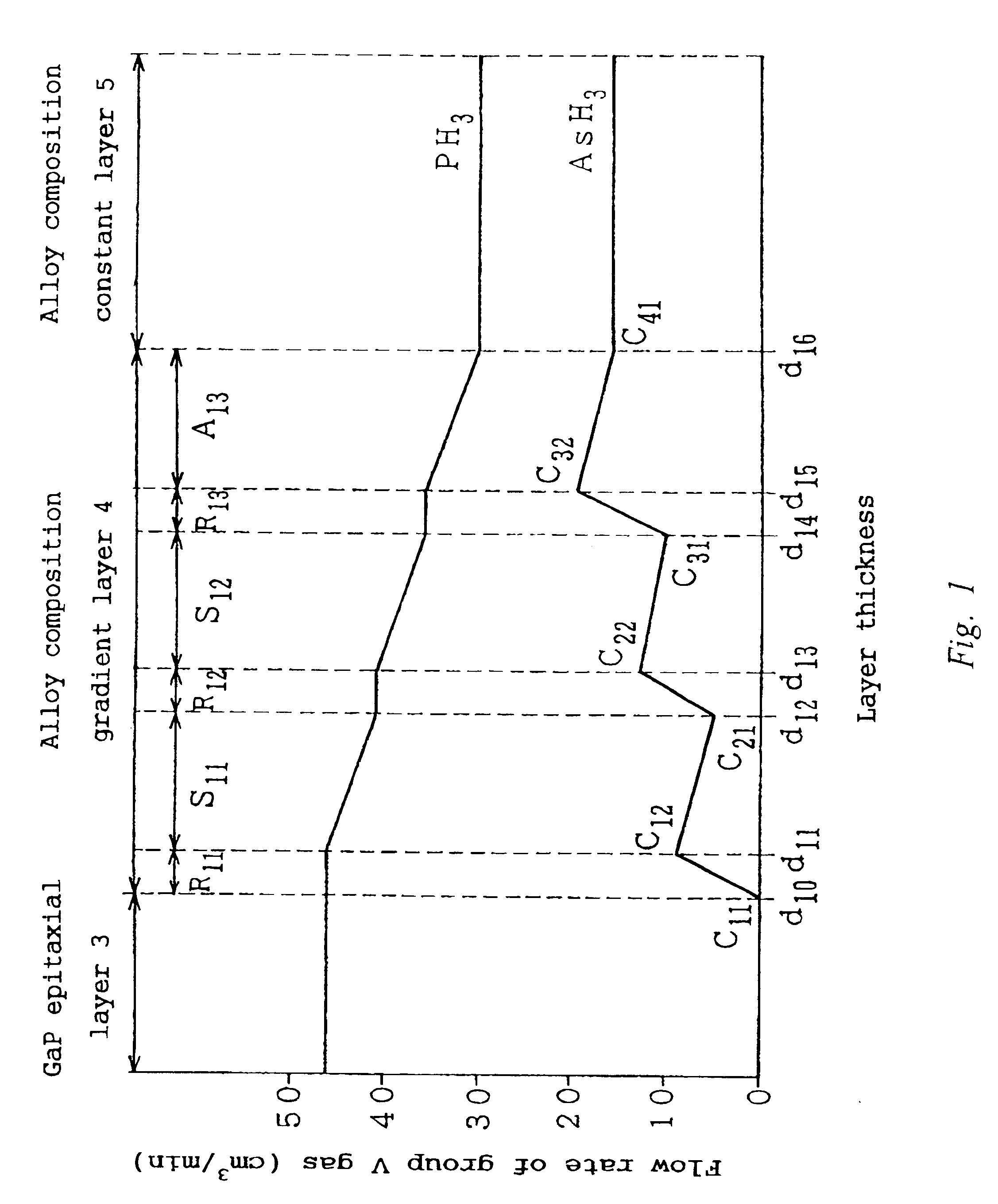

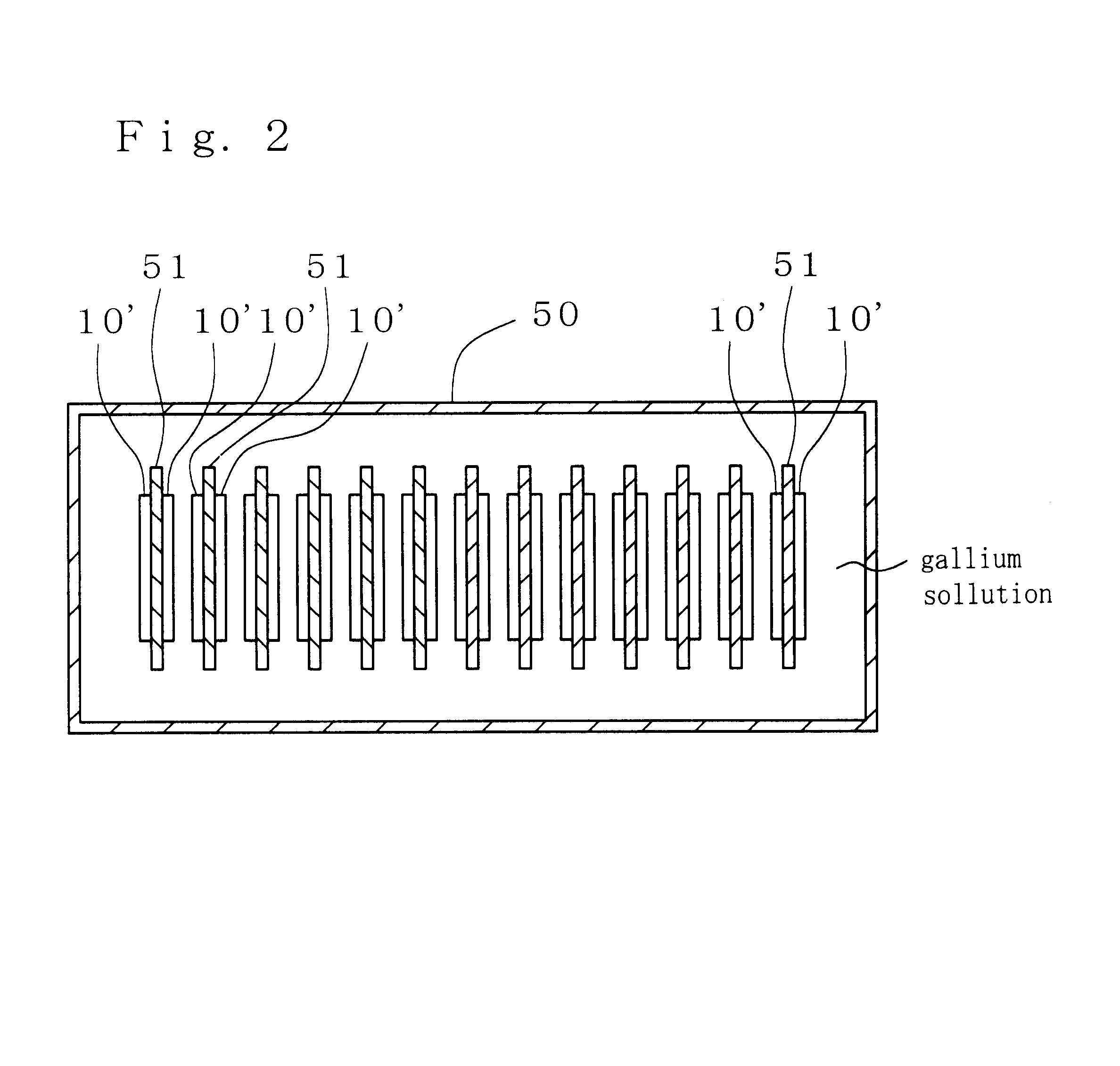

Method for manufacturing compound semiconductor epitaxial wafer

InactiveUS6171394B1Improve efficiencyEfficient growth processPolycrystalline material growthSemiconductor/solid-state device manufacturingGallium arsenide phosphideSingle crystal substrate

A method for manufacturing compound semiconductor epitaxial wafer allowing sharp changes in alloy composition and growth of high-quality epitaxial layers. In a process for epitaxially growing a gallium arsenide phosphide GaAs1-xPx alloy composition gradient layer 4 on a compound semiconductor single-crystalline substrate made of gallium phosphide GaP or gallium arsenide GaAs, one group V gas as a source for the group V element not composing the single-crystalline substrate is varied in its supply volume in at least one cycle of sharp increase / moderate decrease, while the other group V gas as a source for the group V element composing the single-crystalline substrate is moderately decreased, thereby achieving at least one cycle of sharp increase / moderate decrease of a product of partial pressures of the group III and group V gases so that at least one set of an increasing zone and a decreasing zone of the alloy composition is formed within the gallium arsenide phosphide GaAs1-xPx alloy composition gradient layer 4.

Owner:SHIN-ETSU HANDOTAI CO LTD

Electronic devices formed on substrates and their fabrication methods

InactiveUS20060157695A1Improve pressure resistanceLarge bandgapTransistorThyristorAs elementDevice form

The present invention relates to semiconductor electronic devices including molybdenum oxide formed on substrates which consist of materials which are used in known semiconductor electronic devices. The present invention relates to also a new method to fabricate said electronic devices on substrates made of materials which have been used in usual electronic and photonic devices. Suitable substrates consist of materials such as element semiconductors such as silicon and germanium, III-V compound semiconductors such as gallium arsenide and gallium phosphide, II-IV compound semiconductors such as zinc oxide, IV compound semiconductors, organic semiconductors, metal crystals and their derivatives or glasses.

Owner:TAKASHI KATODA

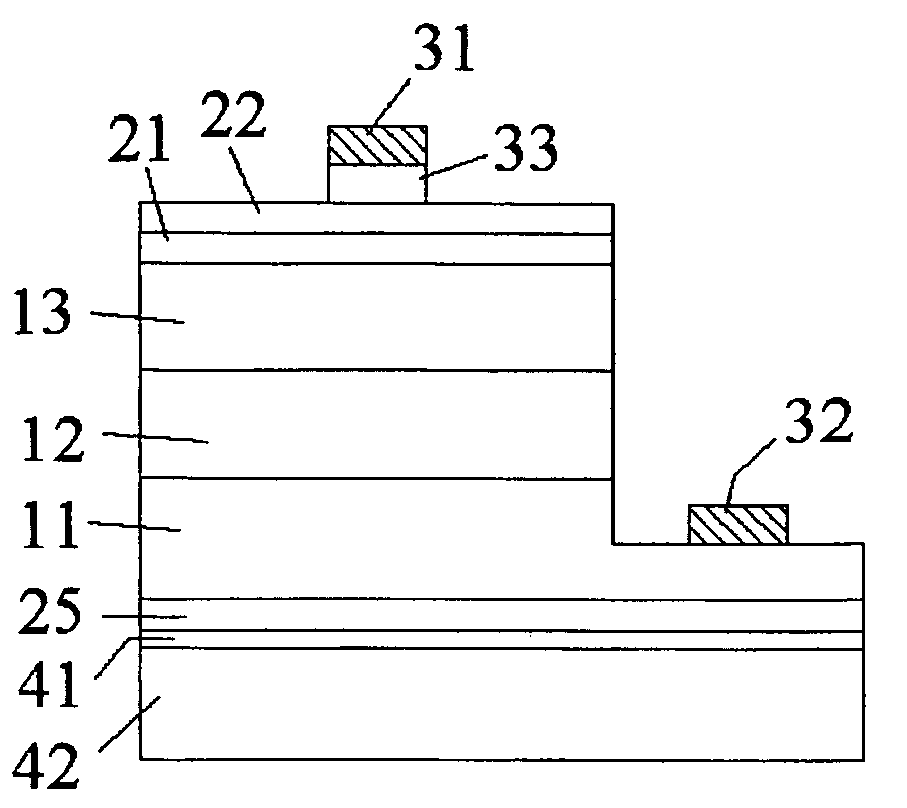

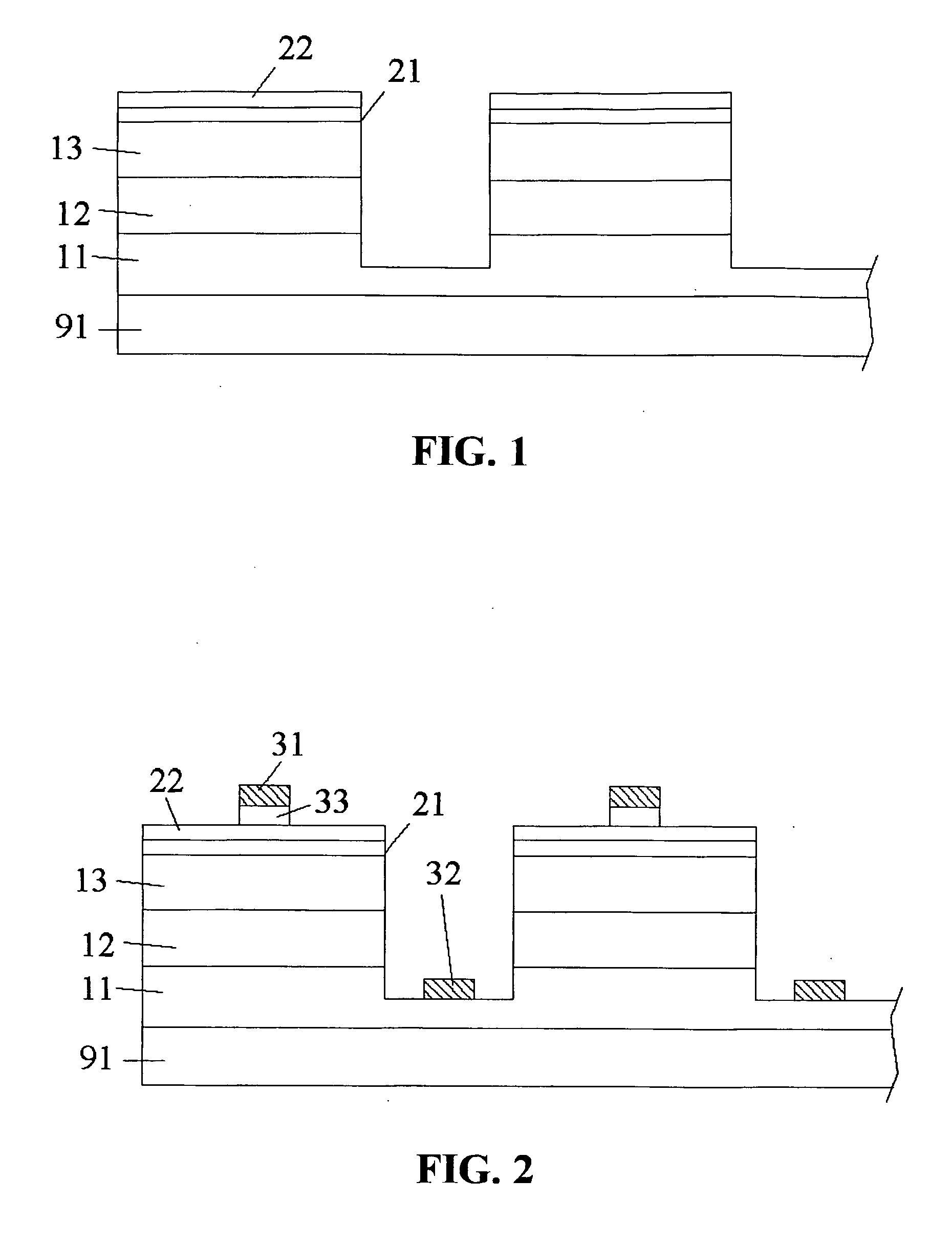

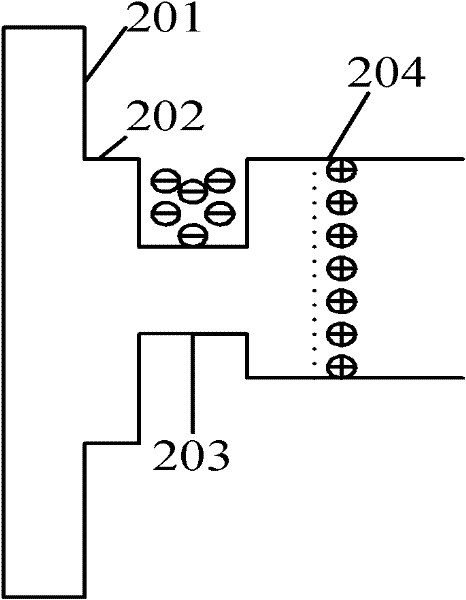

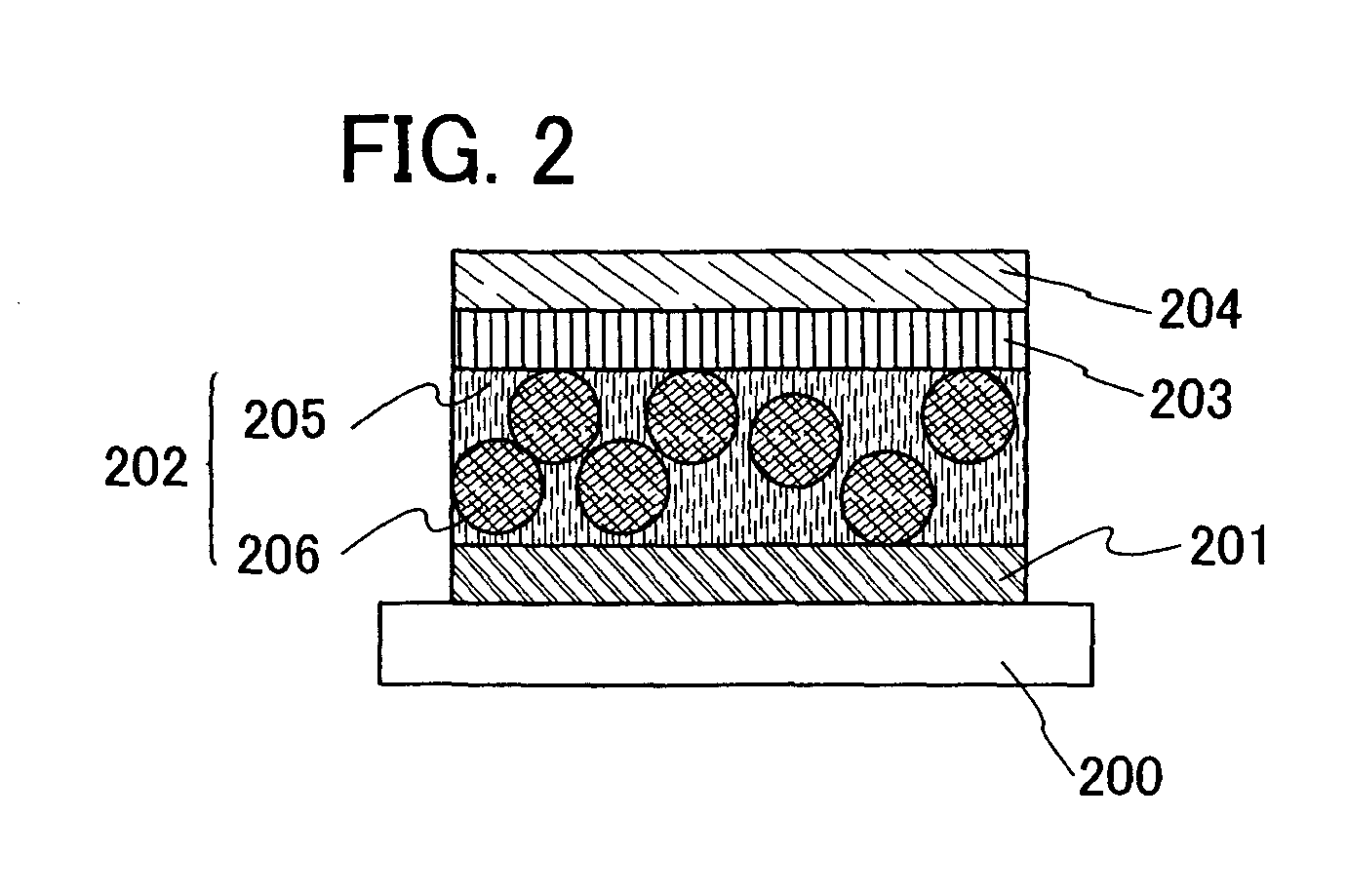

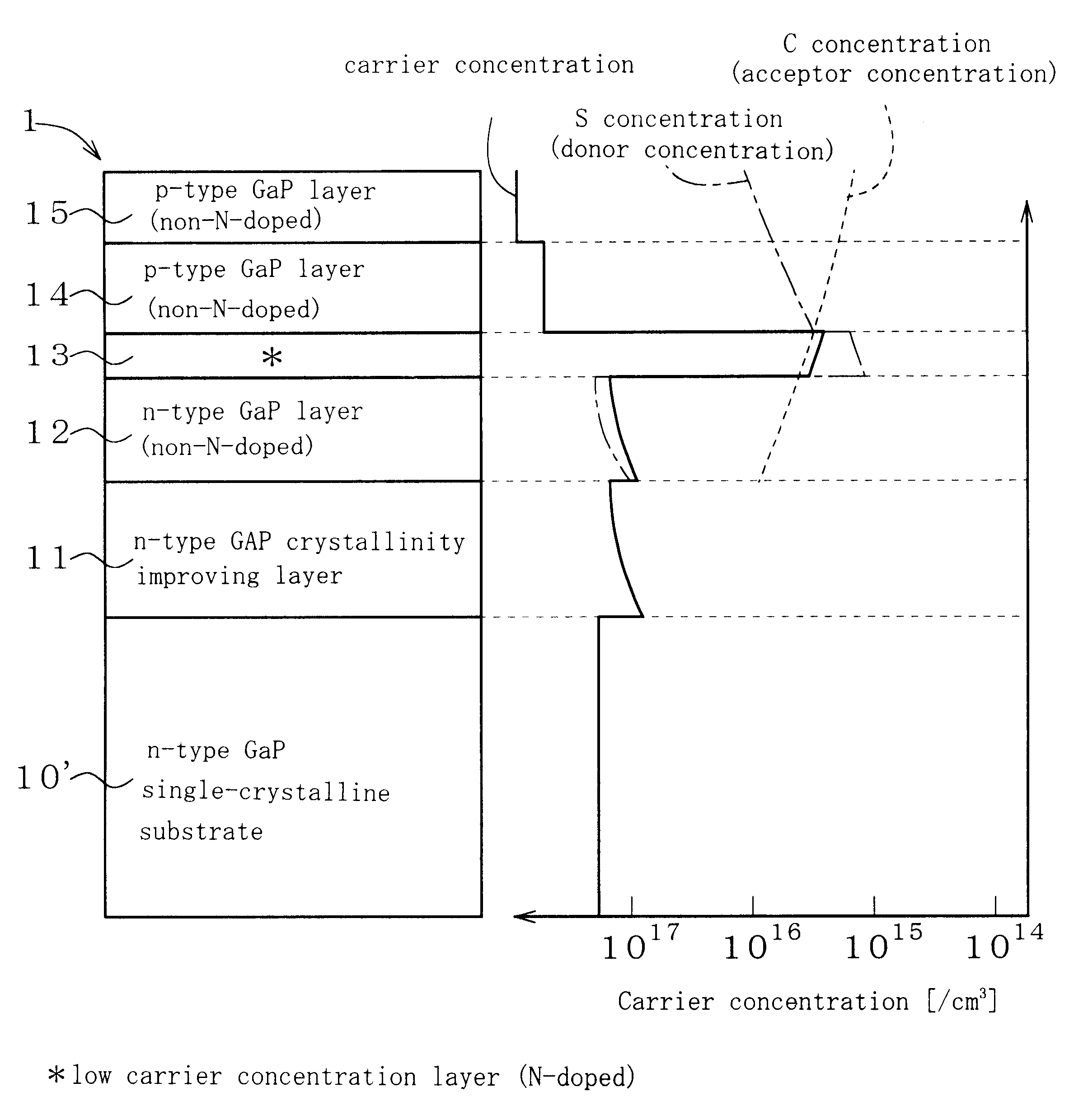

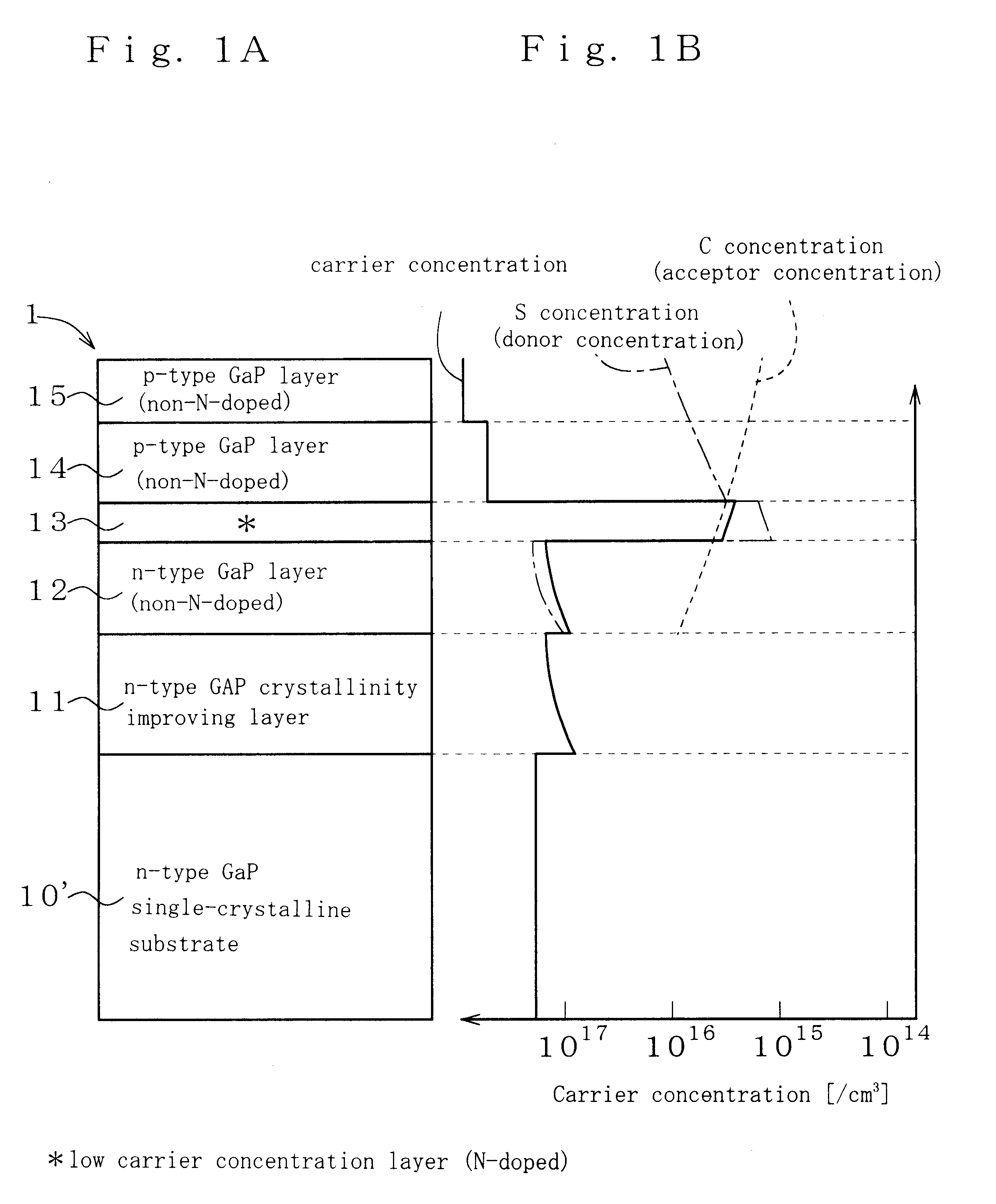

Gallium phosphide luminescent device

InactiveUS6479312B1Solid-state devicesSemiconductor/solid-state device manufacturingCharge carrierP–n junction

By providing a nitrogen-doped low carrier concentration layer 13 having both of a donor concentration and an acceptor concentration controlled below 1x1016 / cm3 at a p-n junction portion between an n-type GaP layer 12 and a p-type GaP layer 14, the luminance of the GaP light emitting device can be improved by as much as 20 to 30% over the conventional one. Suppressing the donor concentration and the acceptor concentration in the low carrier concentration layer 13 below 1x1016 / cm3 inevitably gives a carrier concentration, which is expressed as a difference between both concentrations, lower than 1x1016 / cm3 accordingly. The emission efficiency upon injection of electrons or holes can be improved by suppressing the concentration of the donor which serves as non-emissive center below 1x1016 / cm3 to thereby extend the carrier lifetime; and by concomitantly suppressing the carrier concentration at a level significantly lower than that in the adjacent layers 12 and 14.

Owner:SHIN-ETSU HANDOTAI CO LTD

Method for improving light extraction efficiency of light-emitting diode by means of nanoindentations

InactiveCN104241462AImprove light extraction efficiencyAvoid pollutionSemiconductor devicesManufacturing technologyGallium

The invention provides a method for improving the light extraction efficiency of a light-emitting diode by means of nanoindentations. According to the method for improving the light extraction efficiency of the light-emitting diode by means of the nanoindentations, a nanoscale patterned sapphire substrate is taken as a template, a large area of periodical nanoindentation structures are formed on a gallium phoshpide window layer of an epitaxial wafer of the light-emitting diode by exerting loads on the patterned sapphire substrate and the epitaxial wafer of the light-emitting diode, and thus the light extraction efficiency of the light-emitting diode is improved. According to the method for improving the light extraction efficiency of the light-emitting diode by means of the nanoindentations, the sizes, the shapes and the periods of the periodical nanoindentation structures formed on the gallium phoshpide window layer of the epitaxial wafer of the light-emitting diode can be effectively controlled by adjusting the shape and the period of the patterned sapphire substrate and the loads. Compared with an existing manufacturing technology, the method for improving the light extraction efficiency of the light-emitting diode by means of the nanoindentations has the advantages that operation is easy, cost is extremely low, and a large area of good nanoindentations can be formed on the surface of the epitaxial wafer of the light-emitting diode rapidly.

Owner:SHANDONG UNIV

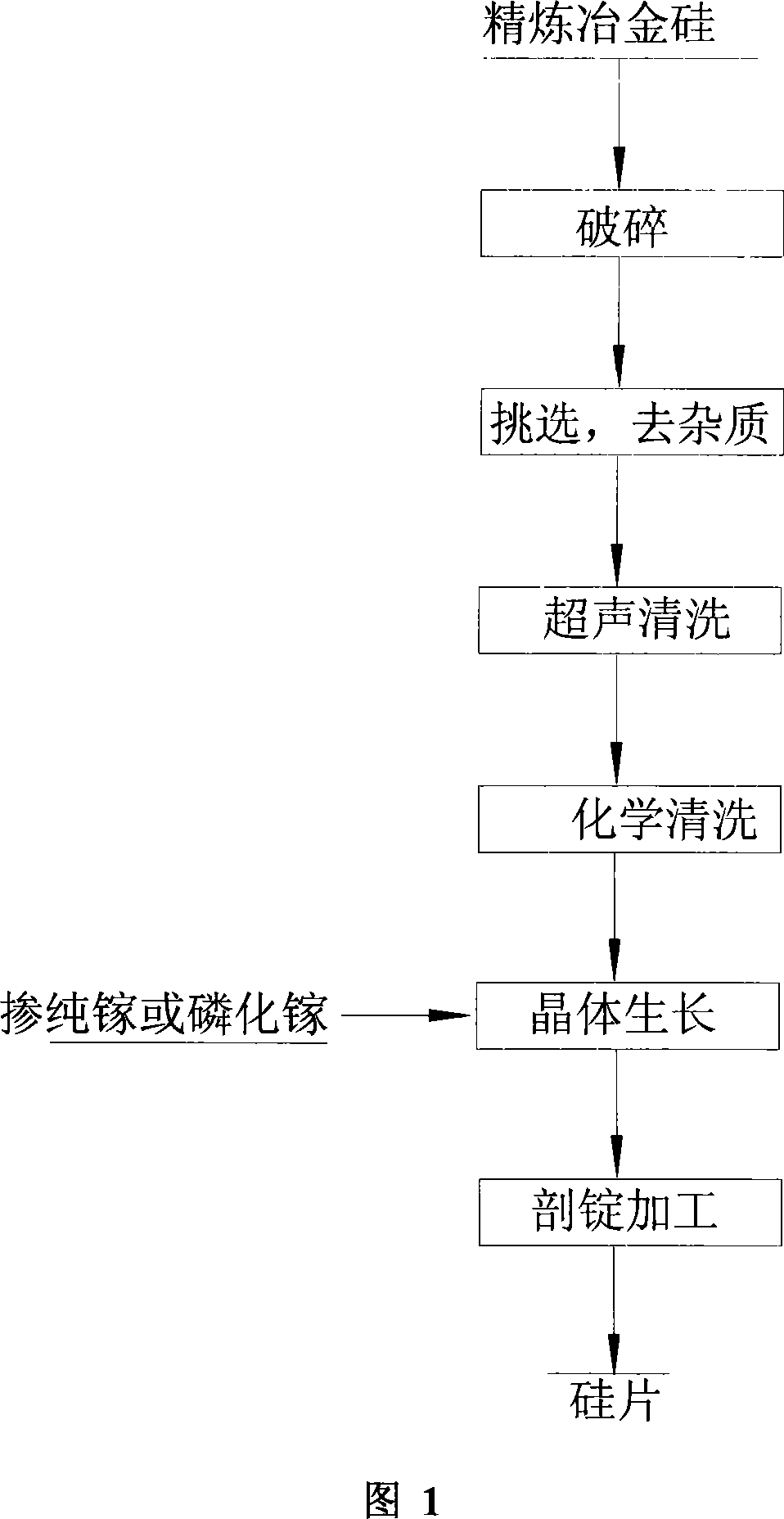

Method for manufacturing silicon crystal plate for solar battery

InactiveCN101220507AIncrease profitLow costPolycrystalline material growthFinal product manufactureIngotSilicon solar cell

The invention discloses a preparing method of a silicon wafer used in a solar cell. At first refining metallurgical silicon is crushed, and visible impurity is removed, and then the silicon is chemically cleaned and thrown into a crystal bar (or ingot) growth furnace, and at the same time, gallium or gallium phosphide is added into the furnace, and the amount is 5 to 14ppma calculated according to the atomic concentration of gallium. After the crystal rod (or ingot) finishes growing, ingot sections processing measurement is operated, and then the needed silicon wafer can be obtained. The method of the invention can use refining metallurgical silicon for producing solar cells, and the method reduces the material cost and is beneficial to the popular application of silicon solar cells.

Owner:CSI CELLS CO LTD

Micro light emitting element and manufacturing method thereof

The invention discloses a micro light emitting element and a manufacturing method thereof. By use of a temporary substrate, an epitaxial structure of a micro light emitting element made of a gallium arsenide and gallium phosphide substrate is transferred. After an epitaxial growing substrate is removed, the following preparation technology of the micro light emitting element is performed. Comparedwith the traditional technology where a chip structure is prepared by use of the epitaxial structure, corrosion to the epitaxial side face can be effectively avoided when the growing substrate is removed through wet etching.

Owner:TIANJIN SANAN OPTOELECTRONICS

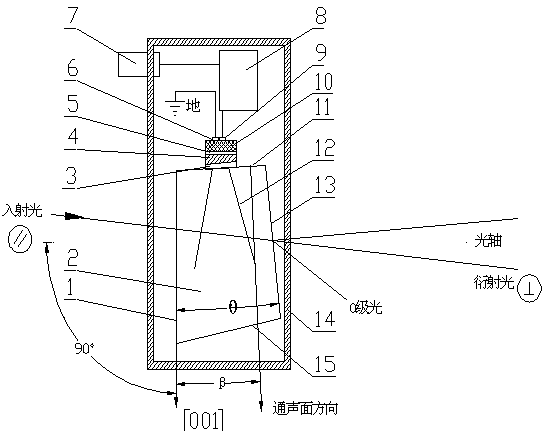

Abnormal broadband acousto-optic deflection device

The invention discloses an abnormal broadband acousto-optic deflection device. An acousto-optic medium is arranged inside a base; a lower electrode layer, a bonding layer and an upper electrode layer are arranged on the sound transmission surface of the acousto-optic medium; an energy converter is arranged on the upper electrode layer; the energy converter is provided with a first surface electrode and a second surface electrode. The acousto-optic medium is a gallium phoshpide crystal, an included angle beta between the direction of the sound transmission surface of the acousto-optic medium and the axis of the gallium phoshpide crystal [001] is smaller than 5 degree, and the optical axis is vertical to the light incoming surface; the energy converter is made of X cutting type lithium niobate crystal for stimulating transverse waves, and the thickness of the energy converter is 1.4-1.6 microns; a correction included angel theta is formed between the light incoming surface and the light outgoing surface of the acousto-optic medium, and the correction included angel theta enables diffracted light to be symmetrical about the optical axis in a working frequency range. According to the abnormal broadband acousto-optic defection device, the scanning angle of the diffracted light is increased, the diffraction efficiency is improved, and the volume of a signal processing system is greatly reduced.

Owner:CHINA ELECTRONICS TECH GRP NO 26 RES INST