Semiconductor device and manufacturing method thereof

A manufacturing method, semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] Hereinafter, an integrated circuit (Bi-HFET) of an HBT and an HFET in an embodiment of the present invention and a method of manufacturing the same will be described with reference to the drawings.

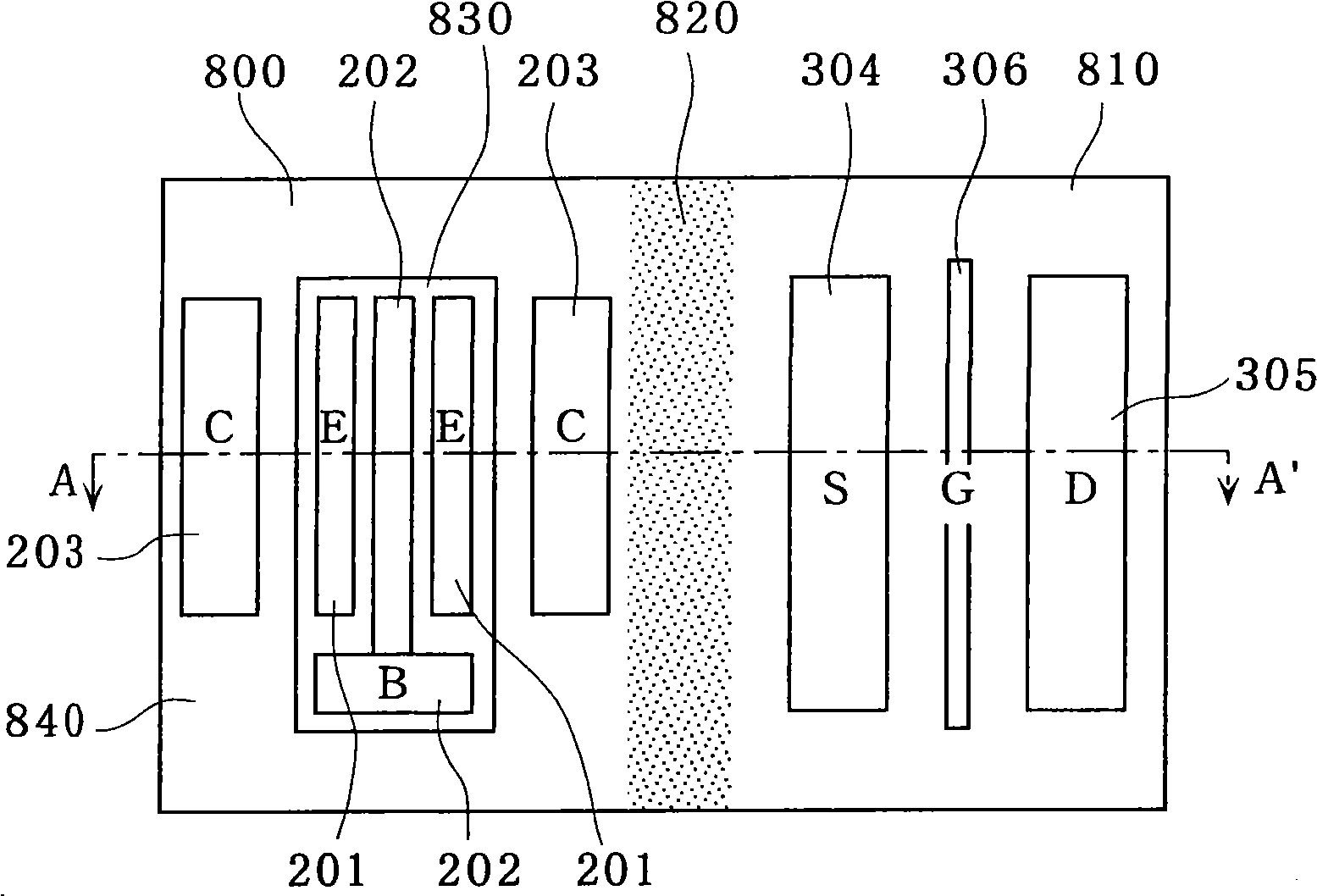

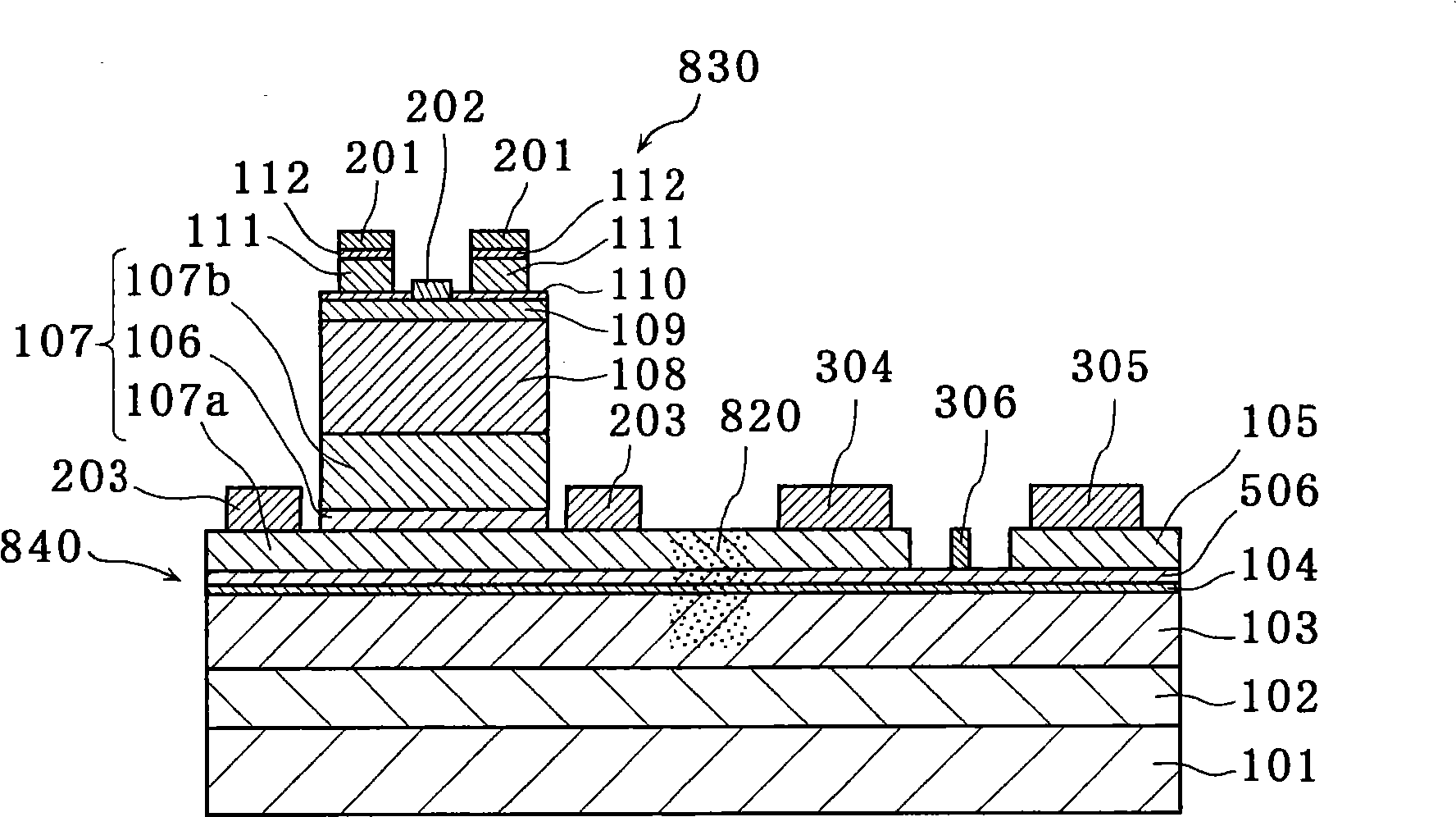

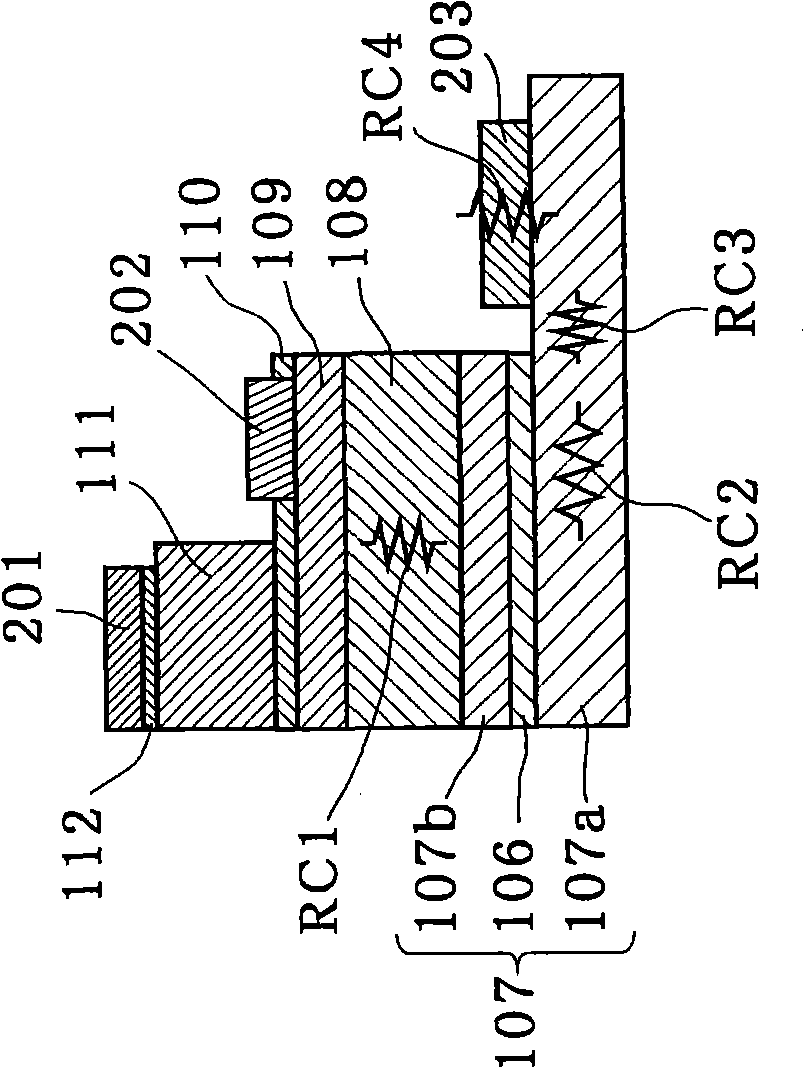

[0054] Figure 1A It is a plan view of the Bi-HFET according to this example. and, Figure 1B is a cross-sectional view of the structure of the Bi-HFET ( Figure 1A sectional view on line A-A').

[0055] This Bi-HFET is a semiconductor device having HBT and HFET formed on the same semiconductor substrate, and has a region 800 where the HBT is formed (HBT region) and a region 810 where the HFET is formed (HFET region). The HBT region 800 and the HFET region 810 are electrically isolated by an implant isolation region 820 .

[0056] In the HFET region 810 , a GaAs / AlGaAs superlattice layer 102 , an AlGaAs barrier layer 103 , an InGaAs channel layer 104 , an electron supply layer 506 and a GaAs cladding layer 105 are sequentially stacked on a semi-insulating GaAs substrate...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More