Preparation method for silicon surface anti-reflection nanometer array structure

A technology of nano-array and array structure, which is applied in the field of preparation of controlling the surface nano-structure morphology, can solve the problems of rough and porous structure surface, reduce the performance of black silicon, enhance the surface recombination effect, etc., and achieve good broadband anti-reflection characteristics, Effect of improving photoelectric conversion performance and high surface minority carrier lifetime

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

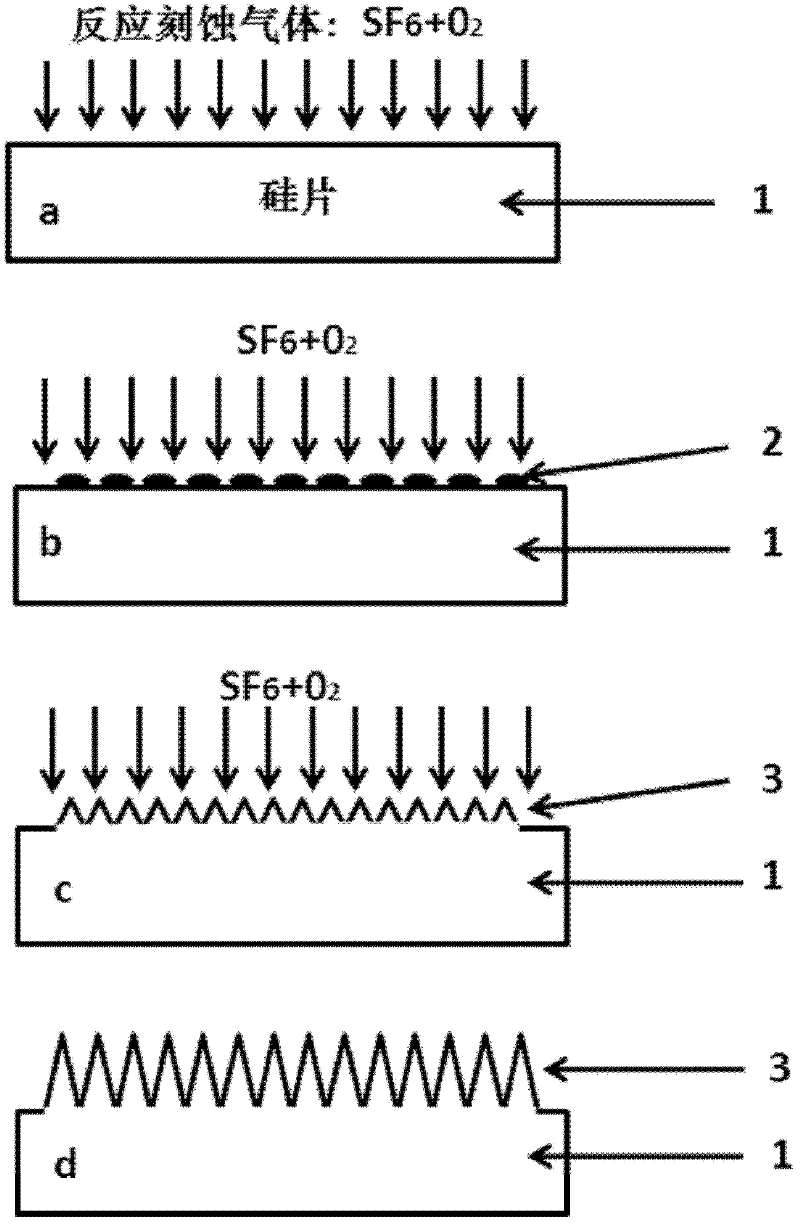

[0029] The preparation method of silicon surface super anti-reflection structure provided by the invention is as follows: figure 1 shown, including the following two steps:

[0030] 1) Wafer cleaning: put a 4-inch P(111) oriented monocrystalline silicon wafer 1 into acetone, alcohol and deionized water in order to ultrasonically clean it, and then dry it with nitrogen;

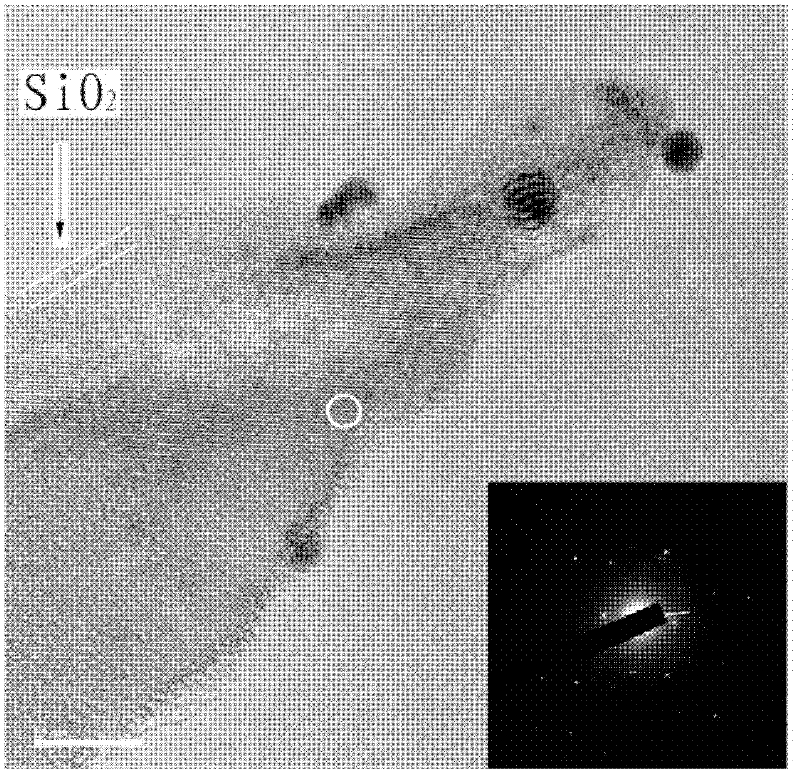

[0031] 2) Etching on the silicon wafer 1 to prepare the super anti-reflection structure on the silicon surface: put the silicon wafer 1 that has been ultrasonically cleaned in step 1 into the ICP system, and obtain the super anti-reflection structure 2 on the silicon surface through low-temperature etching. The specific process conditions As follows: the basic vacuum is about 1.0×10 -6 Torr, from -100°C to -140°C, SF 6 / O 2 The working pressure is 36 / 22-44 / 14, the working pressure is 6-25mTorr, the RIE power is 3-6W, the ICP power is 800-1000W, and the etching time is 7-17 minutes. Etching on the silicon w...

Embodiment 1

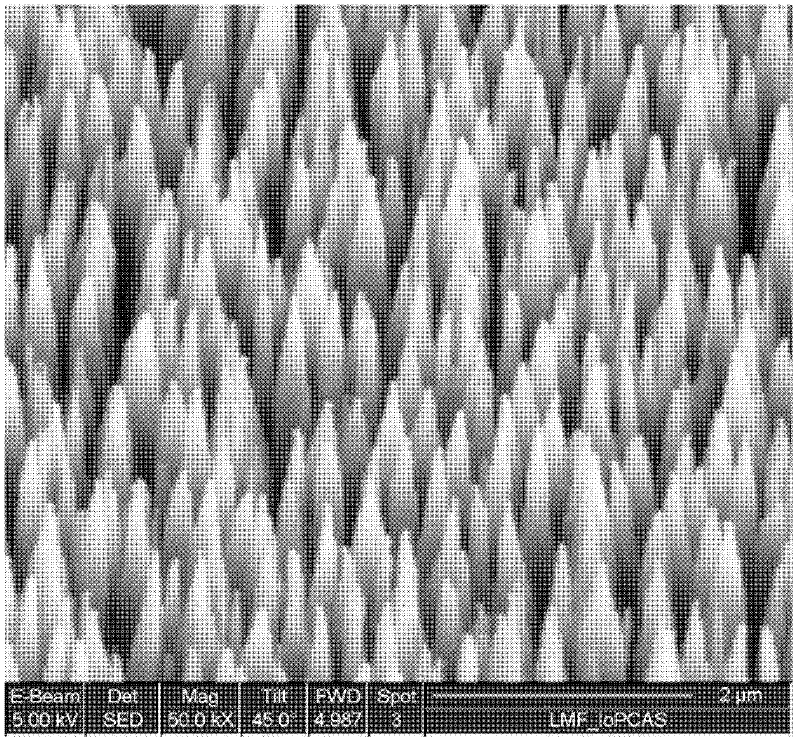

[0041] The surface morphology of the silicon surface super anti-reflection structure prepared in this embodiment can be found in Figure 6 a: The areal density of the super anti-reflective structure on the prepared silicon surface is about 1.3×10 9 / cm 2 , the height is about 1 μm, and the aspect ratio is between 10-20. Its detailed process flow is as follows:

[0042] 1) Clean the silicon wafer: take a 4-inch P(111) oriented monocrystalline silicon 1, use the traditional semiconductor cleaning process, clean it in acetone, alcohol and deionized water in sequence, and then dry it with nitrogen;

[0043] 2) Etching to obtain super anti-reflection surface nanostructures: put the single crystal silicon 1 cleaned in step 1) into the ICP system, and use a low-temperature etching process to prepare ultra-high anti-reflection structures 2 on the silicon surface. The specific process parameters are as follows: The base vacuum is about 1.0×10 -6 Torr, substrate temperature maintain...

Embodiment 2

[0045] The silicon surface super anti-reflection structure of this embodiment can be found in Figure 6 b: The areal density of the prepared silicon surface nanostructures is about 2.0×10 8 / cm 2 , the height is about 3.3 μm, and the aspect ratio is between 4-6. Its detailed process flow is as follows:

[0046] 1) Clean the silicon wafer: take a 4-inch P(111) oriented monocrystalline silicon 1, use the traditional semiconductor cleaning process, clean it in acetone, alcohol and deionized water in sequence, and then dry it with nitrogen;

[0047] 2) Etching to obtain nanostructures on the silicon surface: put the single crystal silicon 1 cleaned in step 1 into the ICP system, and use a low-temperature etching process to prepare black silicon 2. The specific process parameters are as follows: the basic vacuum is 1.0×10 -6 Torr, substrate temperature maintained at -120°C, SF 6 with O 2 The ratio is 40 / 18 (the unit is sccm), the working air pressure is maintained at 25mTorr, ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| height | aaaaa | aaaaa |

| height | aaaaa | aaaaa |

| height | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More