Electrostatic discharge (ESD) protection structure between silicon-on-insulator (SOI)/CMOS integrated circuit power supply and ground

An ESD protection, integrated circuit technology, applied in circuits, electrical components, electrical solid devices, etc., can solve the problems of ESD damage, functional failure, surge, etc., to achieve the effect of easy implementation, simple structure, and compatible process steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The present invention will be further described below in conjunction with specific drawings and embodiments.

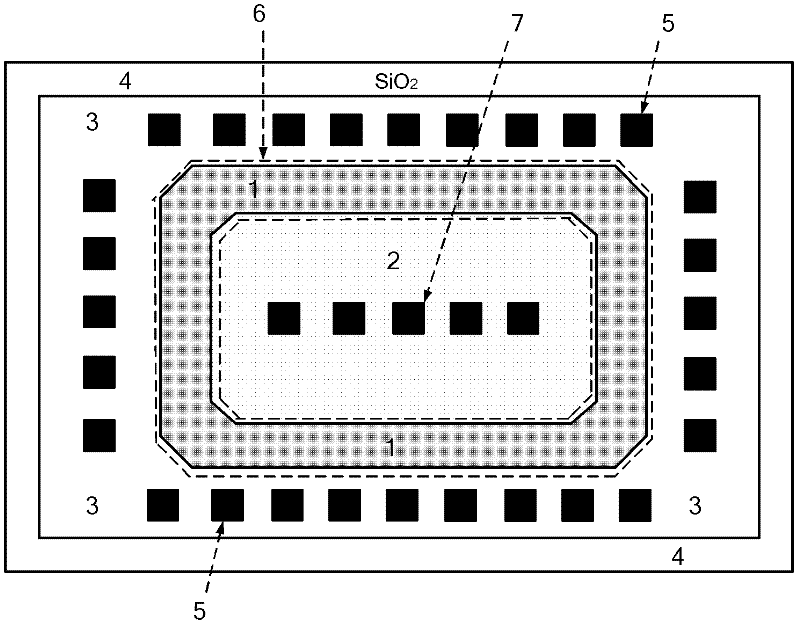

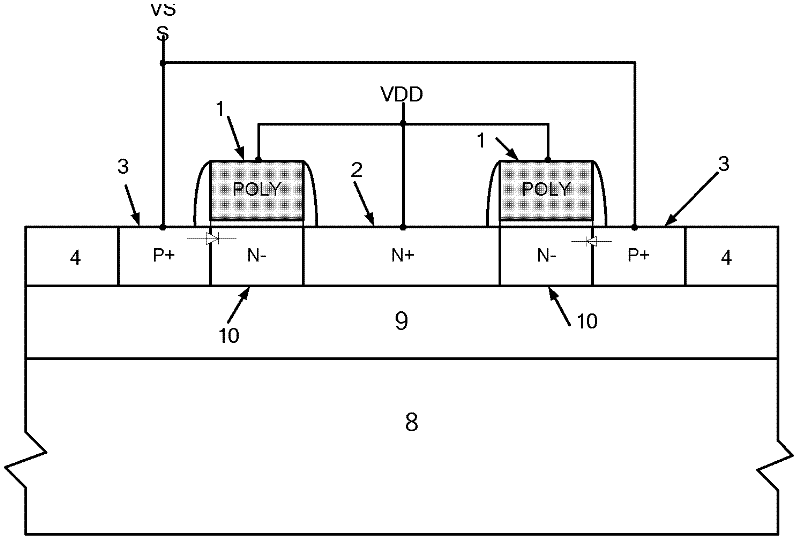

[0018] Such as figure 1 and figure 2 As shown: the ESD protection structure includes an SOI substrate, the SOI substrate includes a substrate 8 , a buried oxide layer 9 is provided on the substrate 8 , and a silicon film is provided on the buried oxide layer 9 . An active area for forming an ESD structure is formed on the silicon film, and an isolation area 4 is provided on the outer periphery of the active area, and the isolation area 4 is silicon dioxide. The active region includes a diffusion region 2 of the first conductivity type, a substrate 10 of the first conductivity type is provided on the outer circumference of the diffusion region 2 of the first conductivity type, and a substrate 10 of the first conductivity type is provided on the outer circumference of the substrate 10 of the first conductivity type. The diffusion region 3 of the second conduct...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More