High-isolation integrated circuit packaged by adopting ceramic casing

A high isolation, ceramic shell technology, used in circuits, electrical components, electrical solid devices, etc., can solve problems affecting the working characteristics of RF chips, malfunction of surrounding circuits and systems, and great impact on circuit performance, and achieve good applications. Prospects, reducing the number of shots, improving work efficiency and economic benefits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

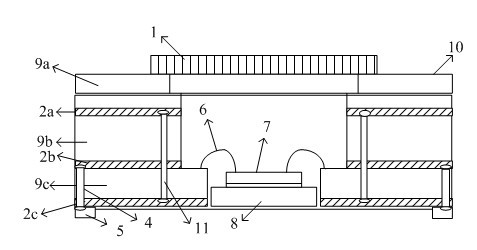

[0022] Embodiment one, see figure 1 , an integrated circuit with high isolation packaged in a ceramic case, including a tube case and a chip 7, the tube case is composed of a case bottom 8, a case 10 and a cover plate 1, the chip 7 is placed on the case bottom 8, and the case 10 includes a first dielectric layer 9a, a first metal base layer 2a, a second dielectric layer 9b, a second metal base layer 2b, a third dielectric layer 9c and a third metal base layer 2c; the first dielectric layer 9a, the first metal base layer 2a, the second dielectric layer 9b, the second metal base layer 2b, the third dielectric layer 9c and the third metal base layer 2c are laminated in order from top to bottom, and the chip 7 is connected to the second metal base layer 2a through the bonding wire 6, the second The second metal base layer 2a is connected to the lead wire 5 through the second through hole 4; the first metal base layer 2a and the third metal base layer 2c are connected through the f...

Embodiment 2

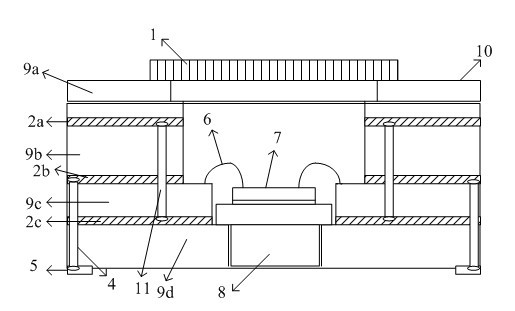

[0023] Embodiment two: see figure 2 The difference between the second embodiment and the first embodiment is that: the housing 10 also includes a fourth dielectric layer 9d, and the fourth dielectric layer 9d is laminated under the third metal base layer 2c; the shell bottom 8 is a heat sink, and the heat sink Made of tungsten-copper alloy material, the metal base layer is made of iron-nickel-cobalt alloy material, the dielectric layer is made of aluminum oxide material, and the third metal base layer 2c is connected to the shell bottom 8; when the chip does not need to dissipate heat through a heat sink, The shell bottom 8 can also be made of aluminum oxide, and connects the first metal base layer 2a to the ground.

Embodiment 3

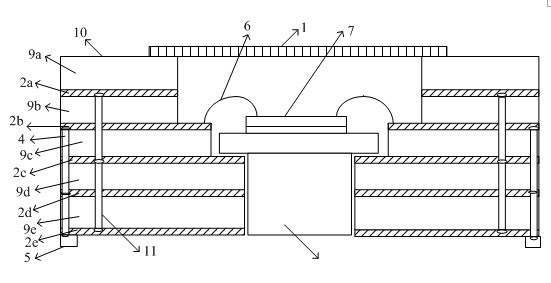

[0024] Embodiment three: see image 3 , an integrated circuit with high isolation packaged in a ceramic case, including a tube case and a chip 7, the tube case is composed of a case bottom 8, a case 10 and a cover plate 1, the chip 7 is placed on the case bottom 8, and the case 10 includes a first dielectric layer 9a, a first metal base layer 2a, a second dielectric layer 9b, a second metal base layer 2b, a third dielectric layer 9c, a third metal base layer 2c, a fourth dielectric layer 9d, a fourth metal base layer 2d, The fifth dielectric layer 9e, the fifth metal base layer 2e and the sixth dielectric layer 9f; the first dielectric layer 9a, the first metal base layer 2a, the second dielectric layer 9b, the second metal base layer 2b, the third dielectric layer 9c, The third metal base layer 2c, the fourth dielectric layer 9d, the fourth metal base layer 2d, the fifth dielectric layer 9e and the fifth metal base layer 2e are laminated in order from top to bottom, and the c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com