Formation method of trench mos

A groove type and groove technology, which is applied in the manufacture of electrical components, semiconductor/solid-state devices, circuits, etc., can solve problems such as low process yield and poor electrical performance, and achieve improved electrical performance, uniform thickness, and breakdown voltage. The effect of increasing the value

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The electrical performance of the trench MOS formed by the existing process is poor, and the process yield is low. For this reason, the inventor of the present invention studies the existing trench type MOS formation process, first provides a kind of formation method of trench type MOS such as Figure 1 to Figure 3 shown.

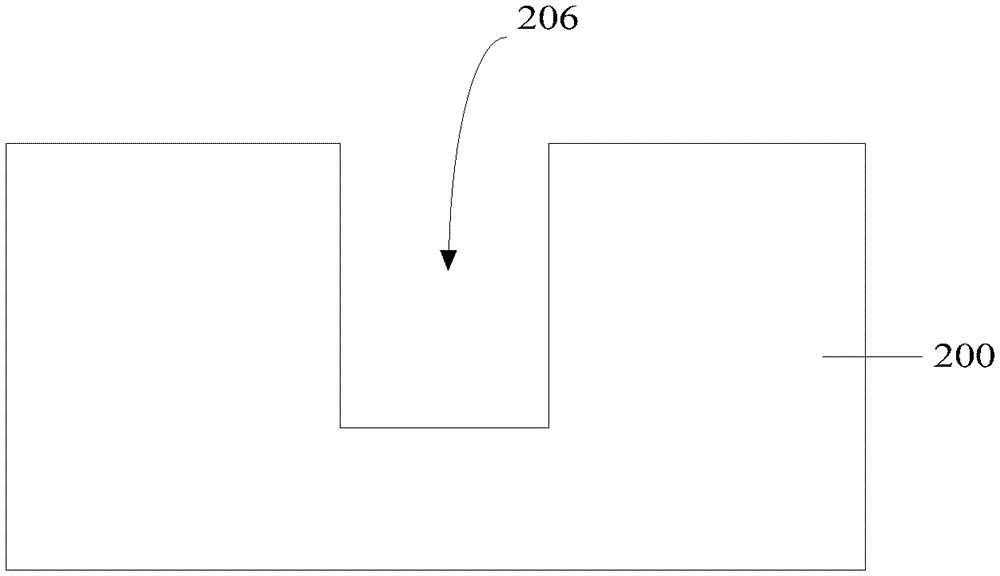

[0030] Please refer to figure 1 , a semiconductor substrate 200 is provided, and a trench 206 is formed in the semiconductor substrate 200 .

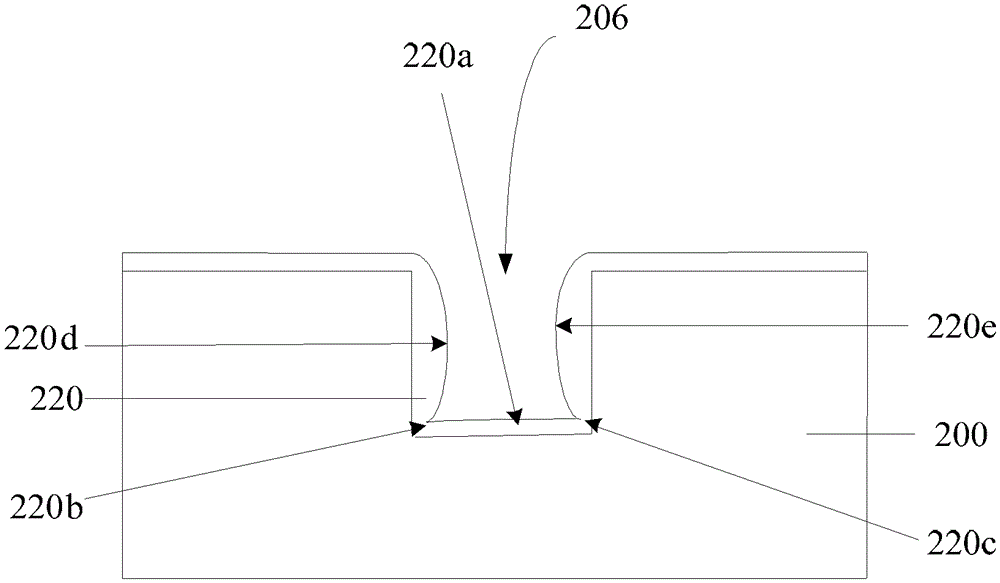

[0031] Please refer to figure 2 , using a thermal oxidation process to form a gate dielectric layer 220 on the bottom and sidewalls of the trench 206, and the gate dielectric layer 220 is silicon oxide.

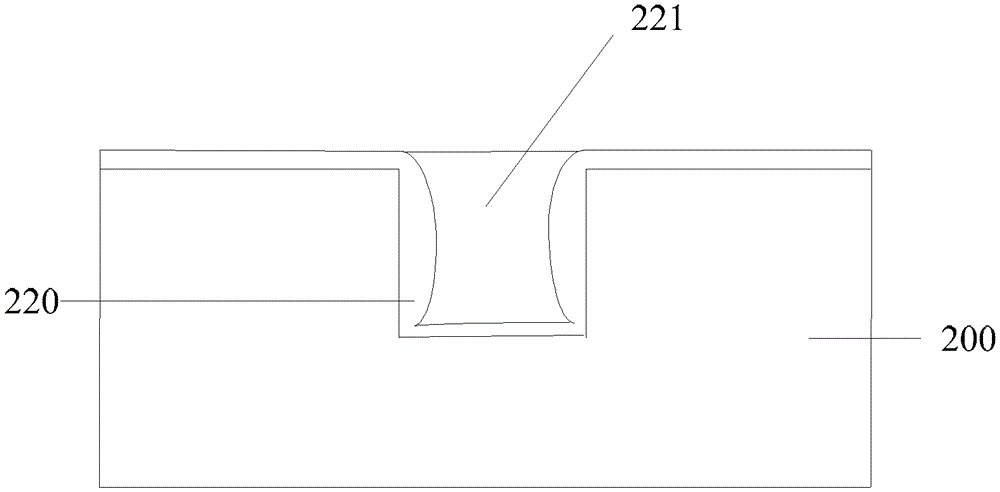

[0032] Please refer to image 3 , forming a trench gate 221 in the trench 206 .

[0033] The inventor discovered and analyzed that, such as figure 2 As shown, after the trench 206 is formed in the substrate, the gate dielectric layer 220 is directly formed on the surface of the trench by a thermal oxi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More