MOS (Metal Oxide Semiconductor) transistor structure integrated with resistive random access memory and manufacturing method of MOS transistor structure

A technology of a resistive memory and a manufacturing method, which is applied to electric solid devices, semiconductor devices, electrical components, etc., can solve the problems of complex integrated structure of resistive memory and MOS transistors, unfavorable device process integration device development, etc., and achieves easy process integration. , the effect of simple process steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

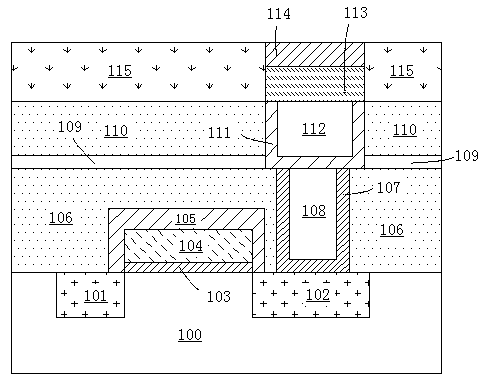

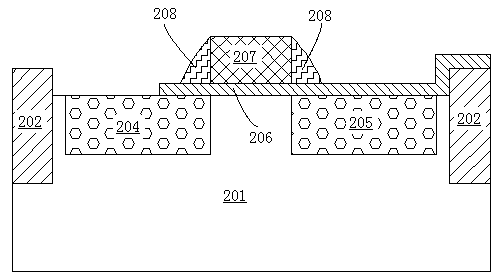

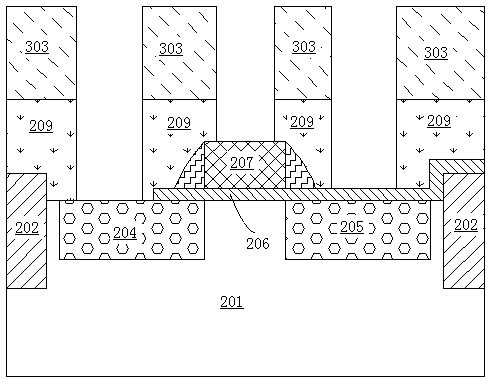

[0031] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments. In the drawings, for the convenience of illustration, the thicknesses of layers and regions are enlarged or reduced, and the sizes shown do not represent actual sizes. Although these figures do not fully reflect the actual size of the device, they still completely reflect the mutual positions between the regions and the constituent structures, especially the upper-lower and adjacent relationships between the constituent structures.

[0032] figure 2 It is an embodiment of the MOS transistor structure of the integrated resistive memory disclosed in the present invention, and it is a cross-sectional view along the channel length direction of the device. Such as figure 2 As shown, the device is typically formed within a semiconductor substrate or doped well 20 that is typically doped with a low concentration of n-type or p-type impuriti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More