Processor fault injection method oriented to BIT software test and simulator thereof

A technology of fault injection and software testing, applied in the field of processors, can solve problems such as failure to execute, failure to inject components, complex operation structure, etc., to achieve the effect of ensuring reliability and accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The present invention will be further described in detail with reference to the accompanying drawings and embodiments.

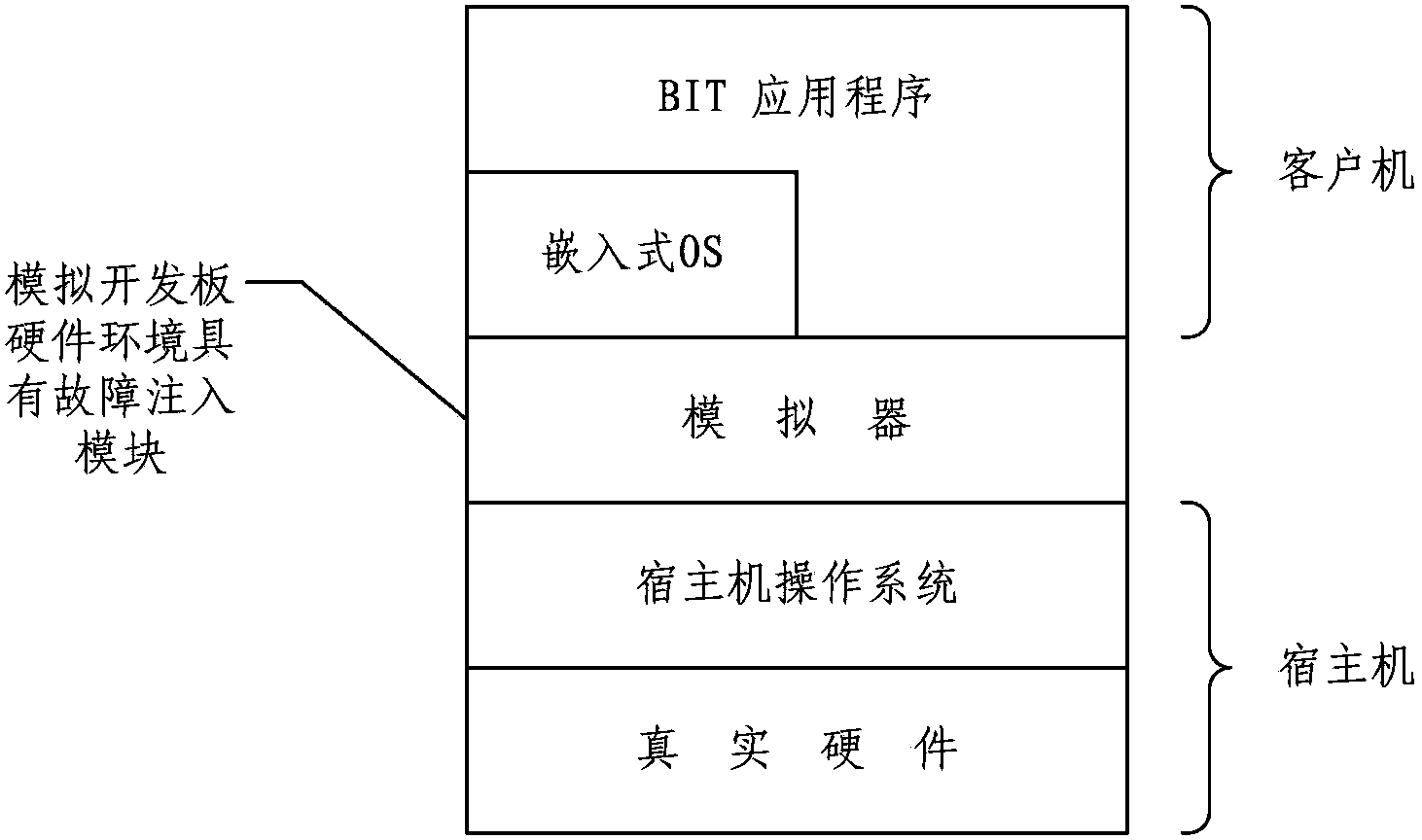

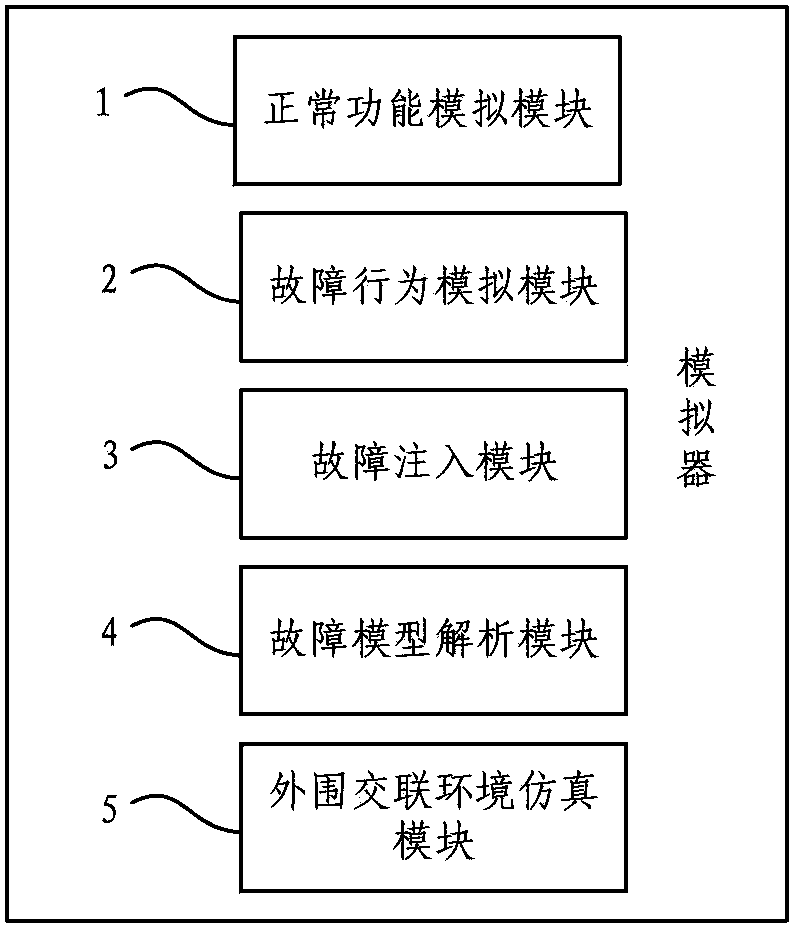

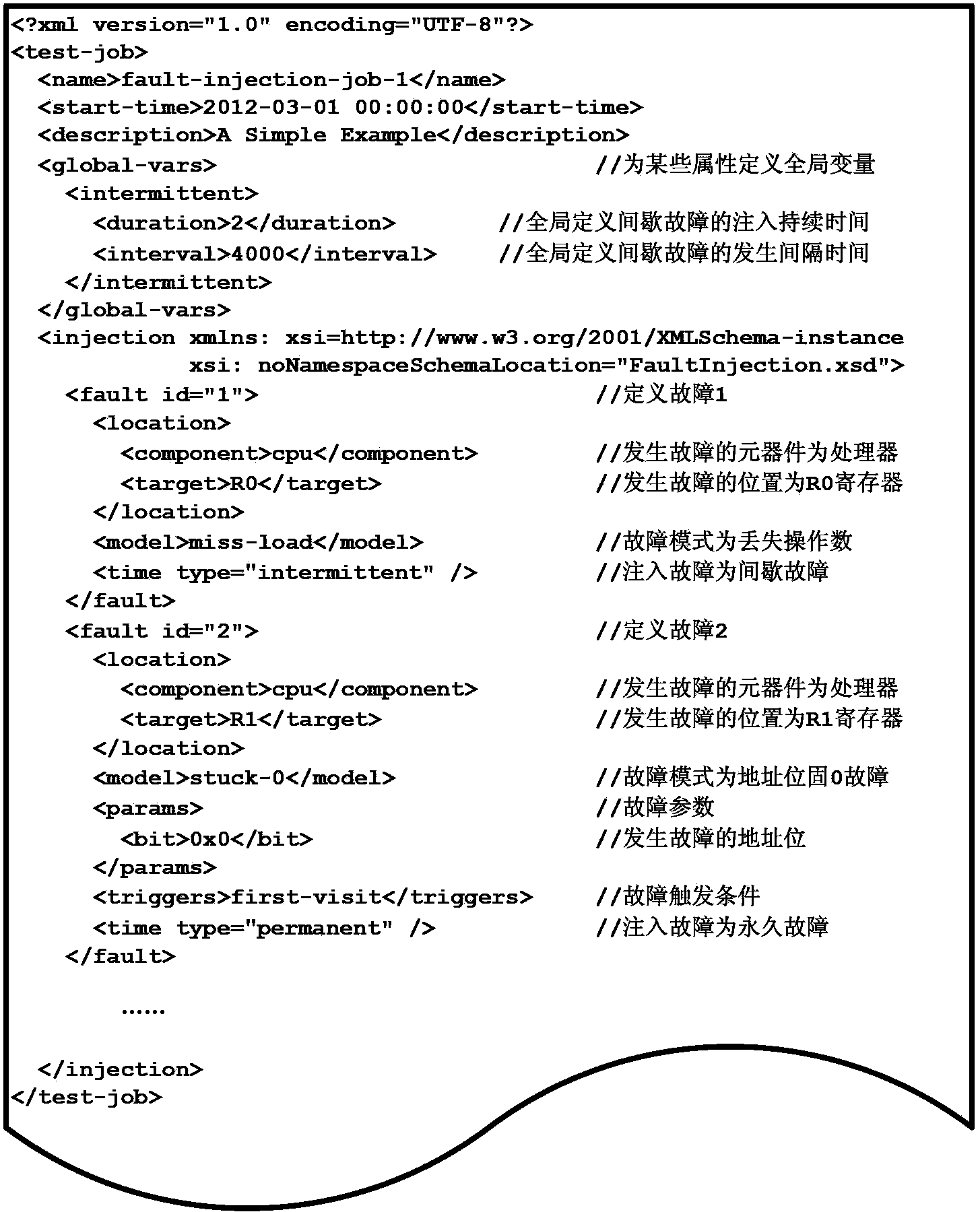

[0043] BIT software, as an embedded software in avionics equipment, cannot directly run on x86 architecture PCs. The hardware circuit boards it runs are generally PowerPC, ARM and other RISC architectures. Due to the closedness and non-invasiveness of aviation boards For other reasons, faults cannot be directly injected into the hardware. Since the emulator is implemented in software according to the real hardware functions, it can be modified arbitrarily without intrusion and damage to the hardware and the applications running on it. Therefore, it is a feasible solution to apply the simulator and fault injection technology to BIT software testing. The basic technical thought of the present invention is: take the hardware circuit board of running BIT software as simulation object, adopt the method for simulator simulation to solve the bottleneck prob...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More