Anti-radiation complementary metal oxide semiconductor (CMOS) device and preparation method thereof

A device and vertical channel technology, which is applied in the radiation-resistant CMOS device and its preparation field, can solve the problems of a single radiation resistance index and does not consider the small-size charge sharing effect, so as to improve the characteristics of single particles, improve the charge sharing effect, Effect of Improving Dosage Characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

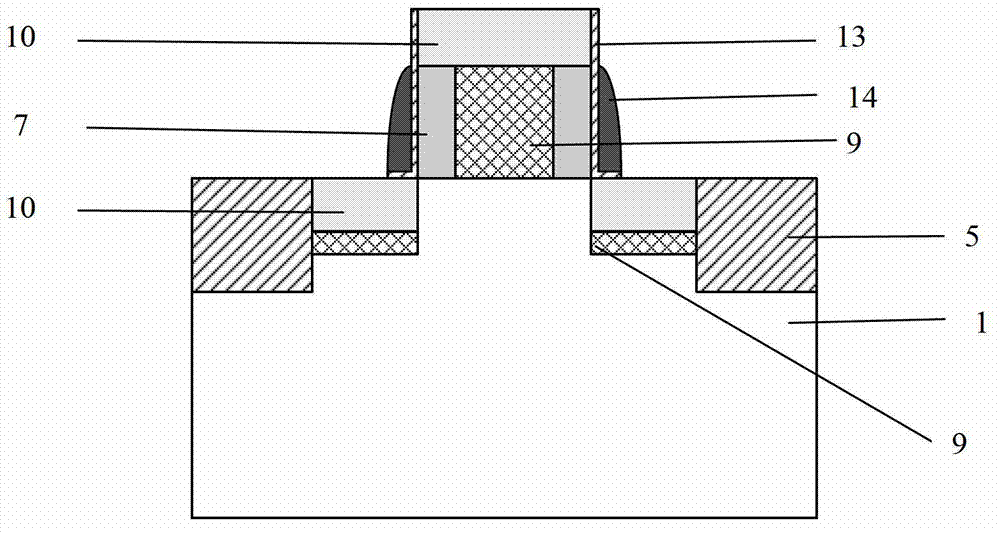

[0024] The embodiments of the present invention will be described in detail below by taking NMOS as an example with reference to the accompanying drawings, wherein the material of the dielectric protection area is silicon nitride.

[0025] 1) Preparation: prepare P-type (100) silicon substrate 1;

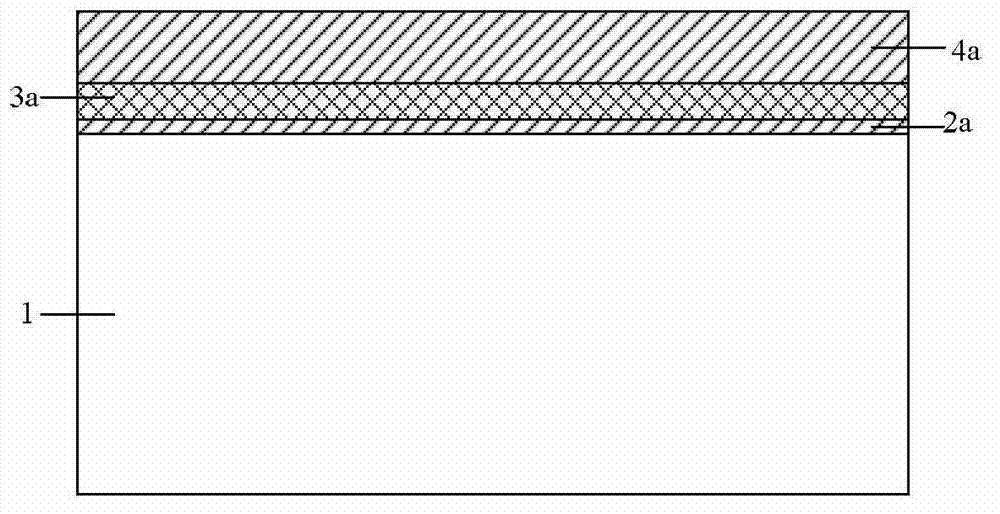

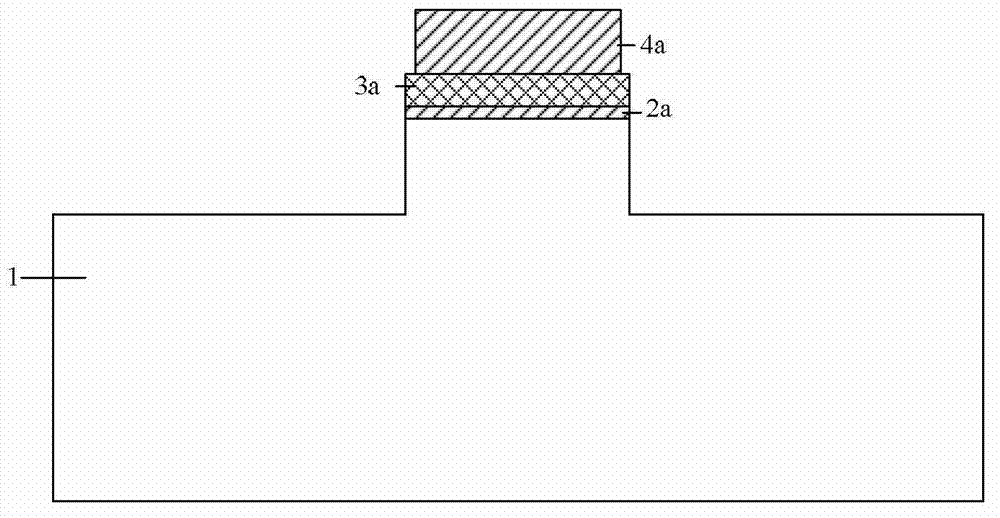

[0026] 2) Etching the active area silicon stage: first thermally oxidize a thin layer of silicon dioxide 2a on the substrate, then low-pressure chemical vapor deposition (LPCVD) a layer of silicon nitride 3a, and then LPCVD a layer of silicon dioxide 4a, such as Figure 2(a); photolithography, reactive ion etching (RIE) silicon dioxide 4a, RIE etching silicon nitride 3a, hydrofluoric acid etching silicon dioxide 2a, so that the etched silicon dioxide 4a and nitride There are tiny steps between the silicon 3a; inductively coupled plasma (ICP) etches the silicon substrate 1 to form a silicon mesa in the active region, as shown in Figure 2(b);

[0027] 3) Form the device isolation regi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More