ESD (Electronic Static Discharge) protection structure based on partial depletion mode SOI (Silicon on Insulator) process

An ESD protection and depletion-type technology, which is applied in the direction of electrical components, electric solid-state devices, circuits, etc., can solve the problems that it is difficult to meet the diverse needs of input/output ports, so as to improve the ESD tolerance level, simple structure, and easy to use. convenient effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

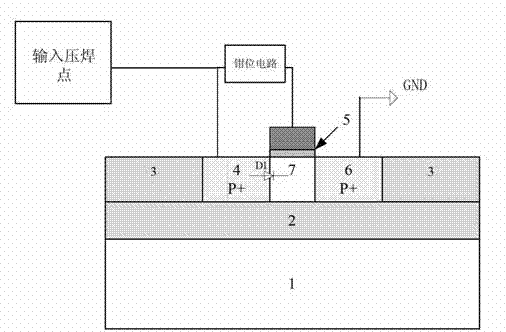

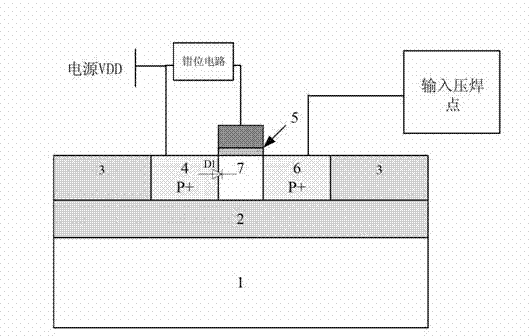

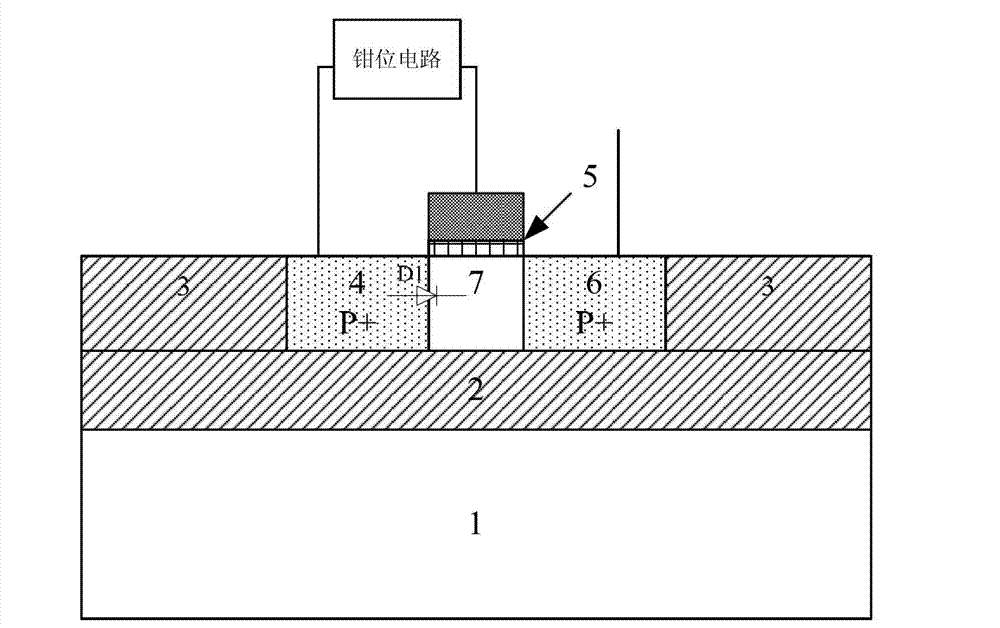

[0024] like figure 1 , as shown in 2, the present invention includes an N-type substrate PMOS tube structure, and the N-type substrate PMOS tube structure includes: gate (ploy gate) 5, P+ source diffusion region 4, P+ drain diffusion region 6, N well 7. Silicon dioxide isolation region 3, buried oxide layer (BOX) 2 and silicon substrate 1, the buried oxide layer 2 is located on the silicon substrate 1, the P+ source diffusion region 4, P+ drain diffusion region 6, The N well 7 and the silicon dioxide isolation region 3 are located on the buried oxide layer 2; the N well 7 is located between the P+ source diffusion region 4 and the P+ drain diffusion region 6, and between the P+ source diffusion region 4 and the N well 7 A parasitic diode D1 is formed, and a silicon dioxide isolation region 3 surrounds the P+ source diffusion region 4 and the P+ drain d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More