Silicon-based InGaAs PIN photoelectric detector based on heterogeneous integration and vertical optical coupling

A photodetector and vertical coupling technology, applied in the coupling of optical waveguides, circuits, electrical components, etc., can solve problems such as the impact of bonding yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The device structure of the present invention will be further described below in conjunction with the accompanying drawings, which are not drawn to scale for the convenience of illustration.

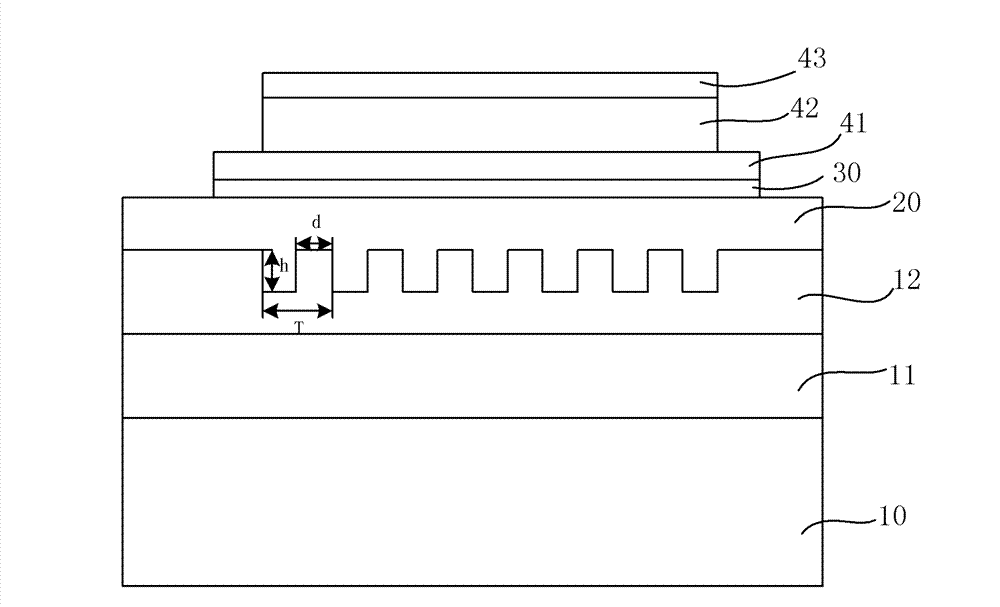

[0030] This embodiment provides a silicon-based InGaAs PIN photodetector based on heterogeneous integration and vertical optical coupling, such as figure 1 shown, including:

[0031] SOI substrate, the SOI substrate includes an underlying substrate 10, a buried oxide layer (BOX, buried oxide) 11 located on the underlying substrate 10, and a top silicon layer 12 located on the buried oxide layer 11;

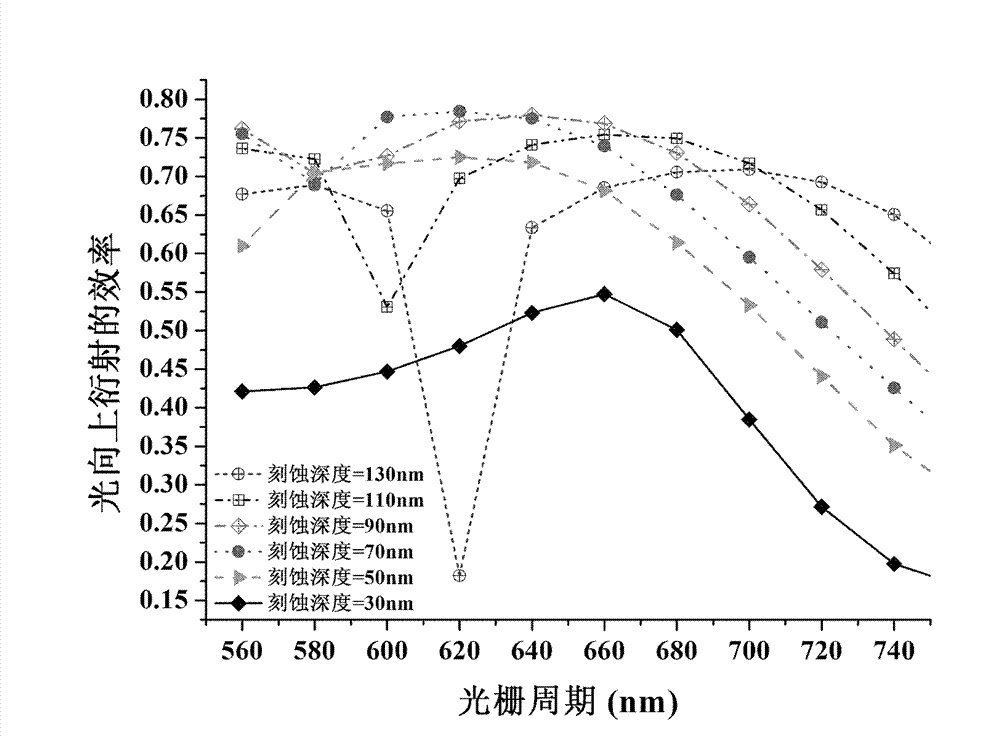

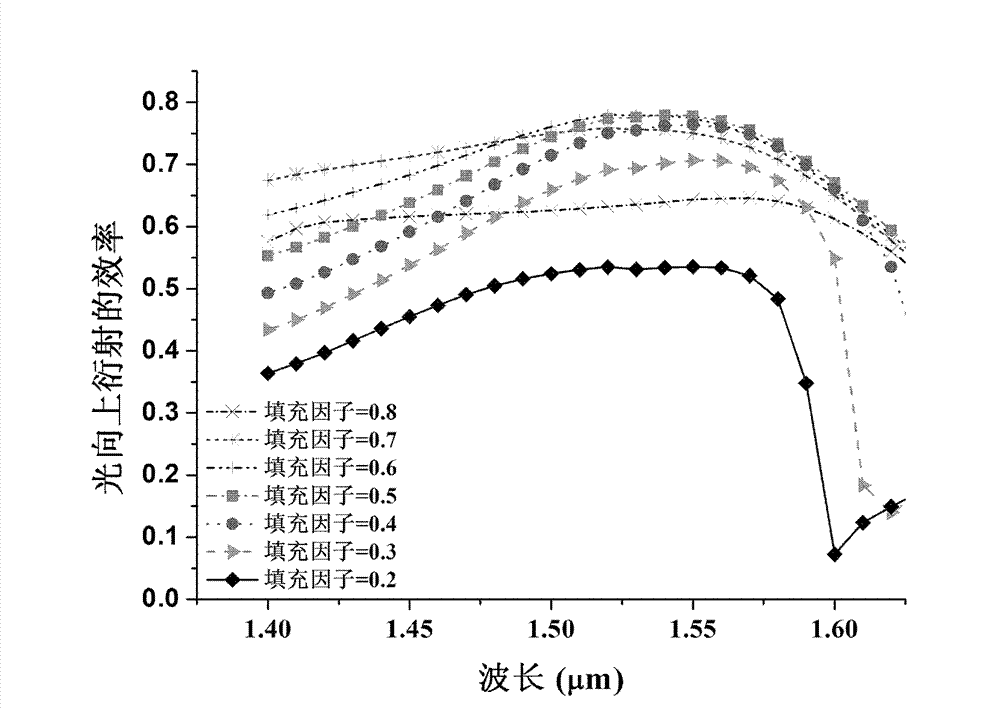

[0032] a vertical coupling grating fabricated in the top silicon 12 of the SOI substrate, the vertical coupling grating is made by etching the top silicon 12 of the SOI substrate, figure 1 where h is the etching depth, T is the grating period, and d is the grating tooth width;

[0033] a BCB bonding layer 20 covering the vertical coupling grating;

[0034] An anti-reflection layer ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Etching depth | aaaaa | aaaaa |

| Etching depth | aaaaa | aaaaa |

| Etching depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More