Double capture-silicon oxide nitride oxide semiconductor (SONOS) memorizer with double layer dielectric charge trapping layer and preparation method thereof

A DC-SONOS, charge trapping layer technology, applied in electric solid-state devices, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of insufficient data retention performance, singleness, etc., to improve the erasing speed and resistance to erasing and writing. ability, improved performance, the effect of suppressing vertical transport of holes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0032] This embodiment provides a specific preparation method of the memory of the present invention.

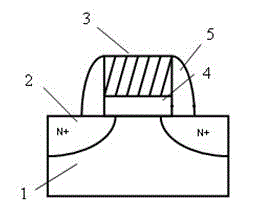

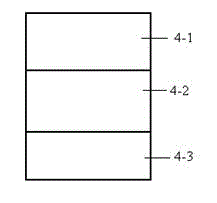

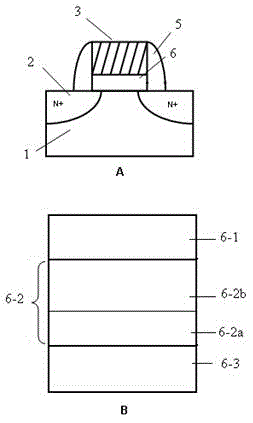

[0033] First provide a semiconductor substrate 1, and then dry oxygen oxidation on the substrate to form a layer of SiO 2, the thickness of this layer is 54?, which is the tunneling layer 6-3. Then use LPCVD technology to form 20 ? Si3N4 successively, which is the first layer of dielectric 6-2a. A layer of SiN is then formed on top of it using PECVD technology, which is the second layer of dielectric 6-2b with a thickness of 40 Å. These two layers together form the composite charge trapping layer 6-2. A 60 Å SiO2 blocking layer 6-1 is then formed on the charge trapping layer using LPCVD technology. Then a gate 3 is formed on it by LPCVD, and sidewalls 5 are formed on both sides of the gate 3 . Finally, the source terminal and the drain terminal 2 are formed by self-aligned ion implantation.

[0034] In actual use of the DC-SONOS memory of the present invention, when ther...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More