Method for growing thick gate oxide layer for high-voltage metal oxide semiconductor (MOS) device

A technology of oxide semiconductors and high-voltage devices, which is applied in the direction of semiconductor devices, can solve problems such as high risk and complex process, and achieve the effects of reducing risk, simple process, and avoiding changes in electrical characteristics and reliability performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] The present invention proposes for the first time that the growth of the thick gate oxide layer of the high-voltage device occurs before the shallow trench isolation (STI), and the silicon nitride layer is used as a hard mask to ensure the thickness of the thick gate oxide layer. The method can avoid changes in the electrical characteristics and reliability performance of low-voltage devices and non-volatile memory devices during the high-voltage gate oxidation process, reduce risks, and at the same time, the process is simple and the number of photolithographic plates remains unchanged. The specific process is as follows:

[0038] Protection of thick gate oxide growth for high-voltage devices occurs prior to shallow trench isolation (STI) formation, through silicon nitride layers as hard masks associated with the process flow. details as follows:

[0039] (1) if figure 1 As shown, thick gate oxide (SiO2①) growth for high-voltage devices.

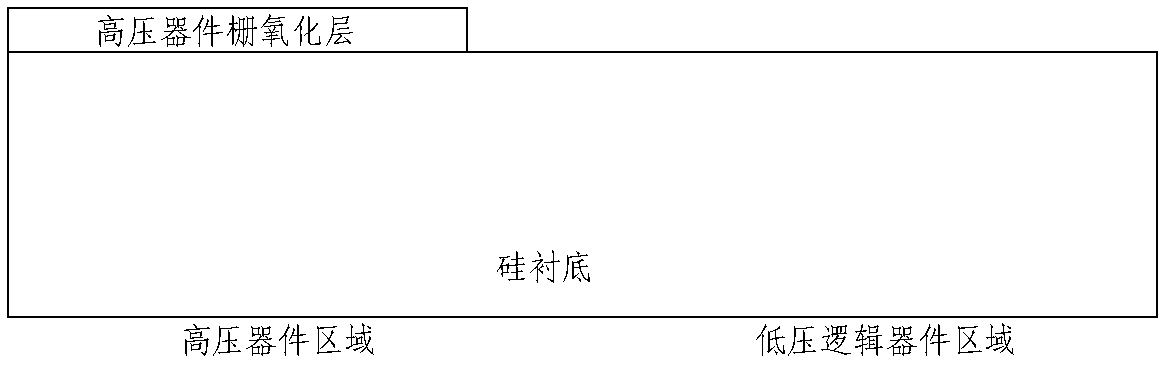

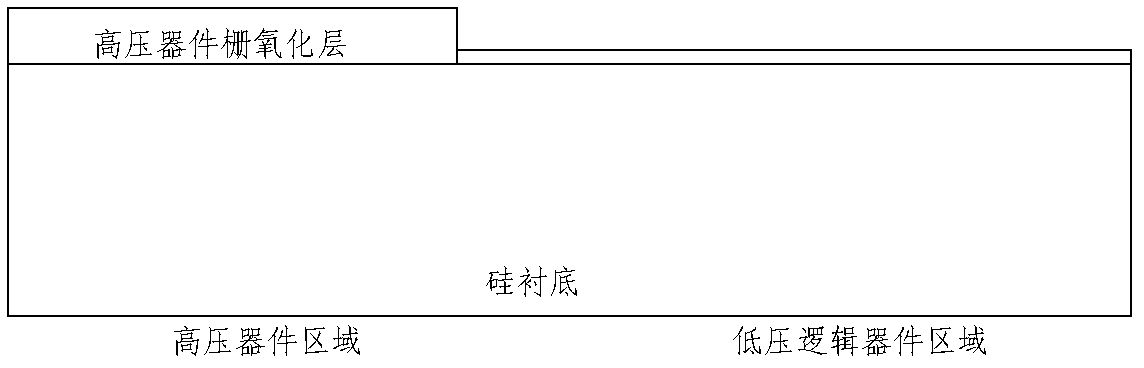

[0040] (2) if figure 2 A...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More