Method of manufacturing field termination type insulated gate bipolar translator (IGBT) component in patching mode

A technology for manufacturing fields and devices, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of broken, large silicon wafers, increased costs, etc., and achieve the effect of reducing the probability of fragmentation and saving huge costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

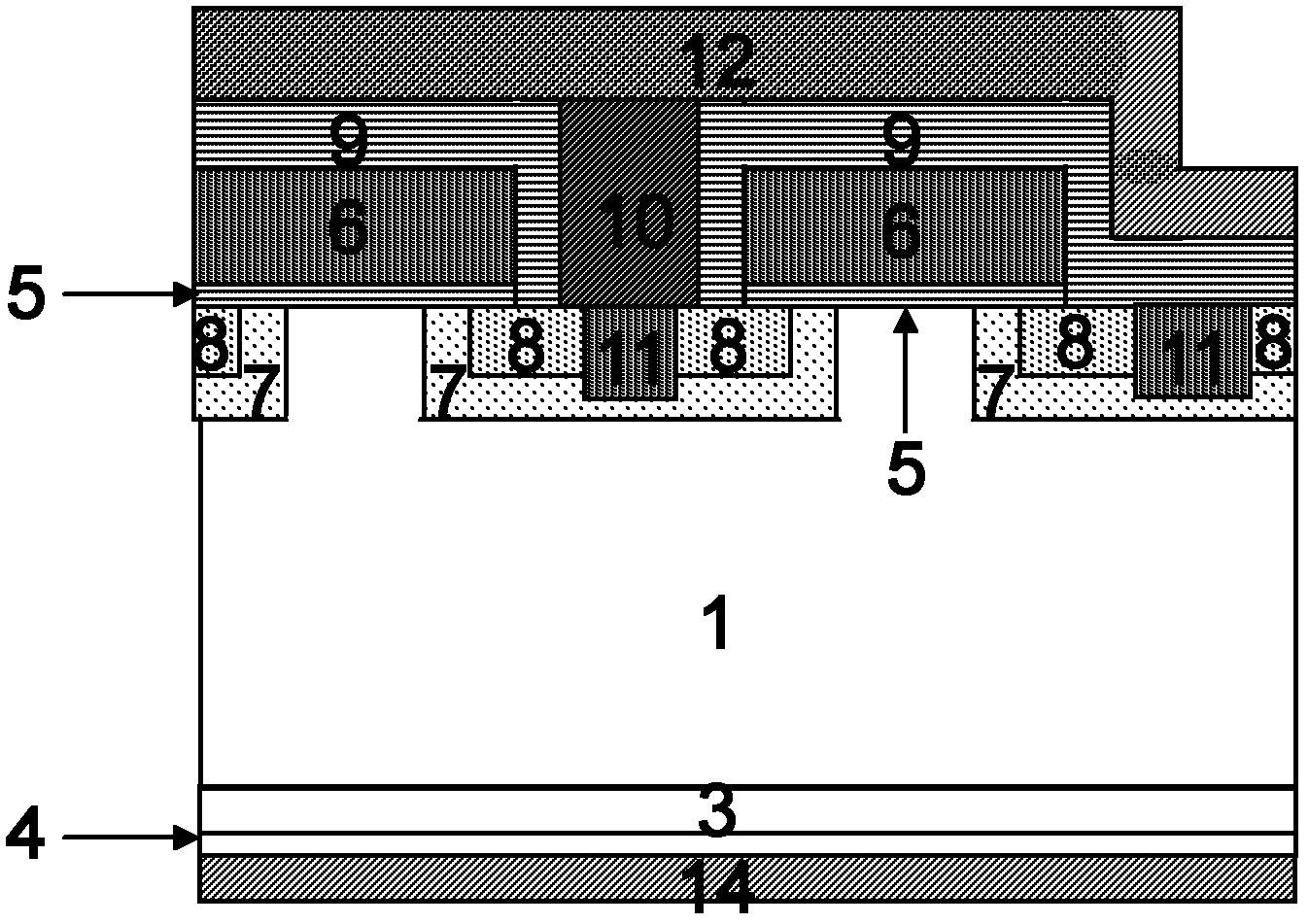

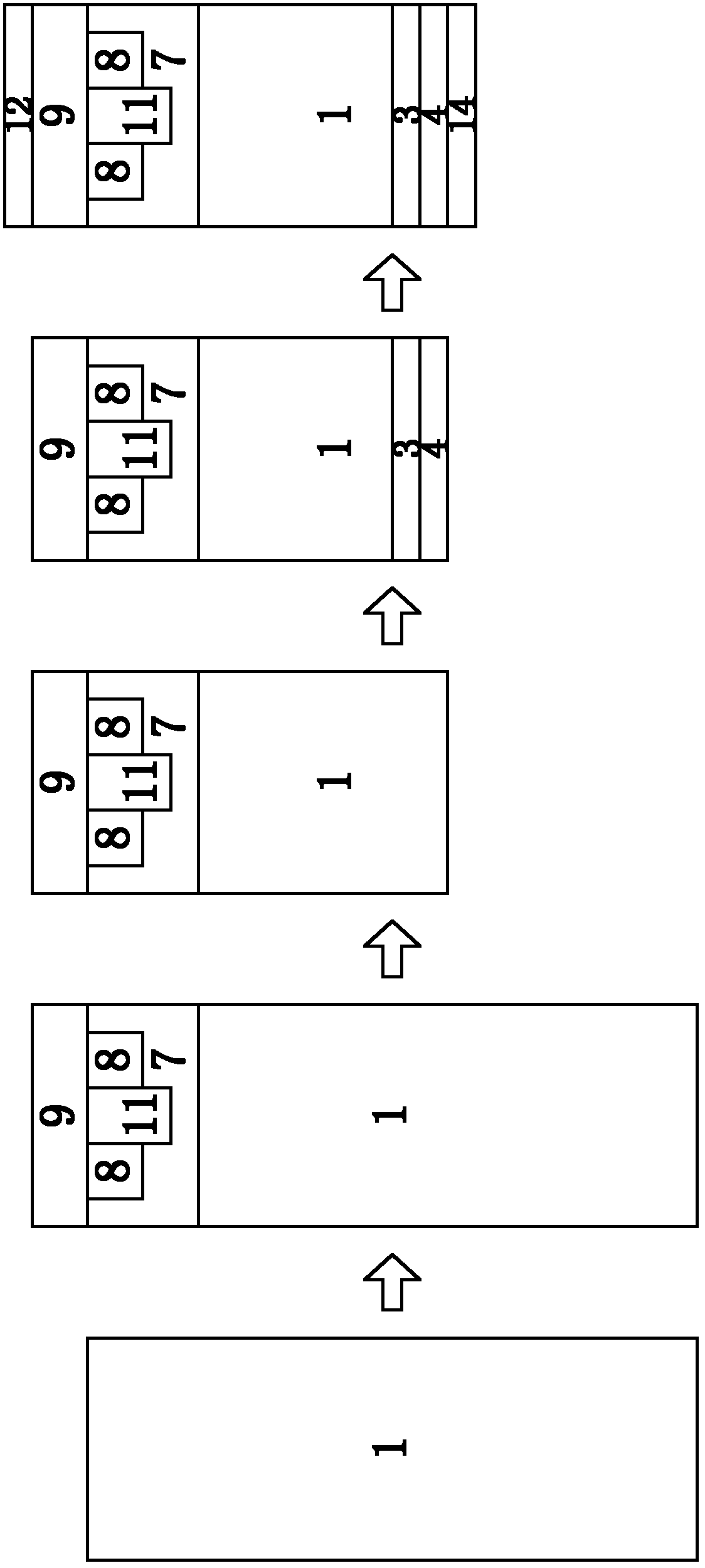

[0024] see image 3 , which is the first embodiment of the method for manufacturing a field-stop type IGBT device in the patch mode of the present invention, which includes the following steps:

[0025] In the first step, the first silicon substrate 10 and the second silicon substrate 40 are selected, both of which are zone-fused single crystal silicon (FZ-Si). The first silicon substrate 10 is preferably n-type medium-low doped, with a doping concentration of 1×10 11 ~1×10 14 Atoms per cubic centimeter, but can also be undoped, p-type doped, etc. The second silicon substrate 40 is preferably p-type heavily doped, with a doping concentration of 1×10 16 ~1×10 19 Atoms per cubic centimeter, but can also be undoped, n-type doped, etc.

[0026] The first silicon substrate 10 is thinned from the front side or the back side, such as chemical mechanical polishing (CMP) process, and the remaining thickness is between 50-300 μm, preferably 60 μm.

[0027] On the front side of the...

no. 2 example

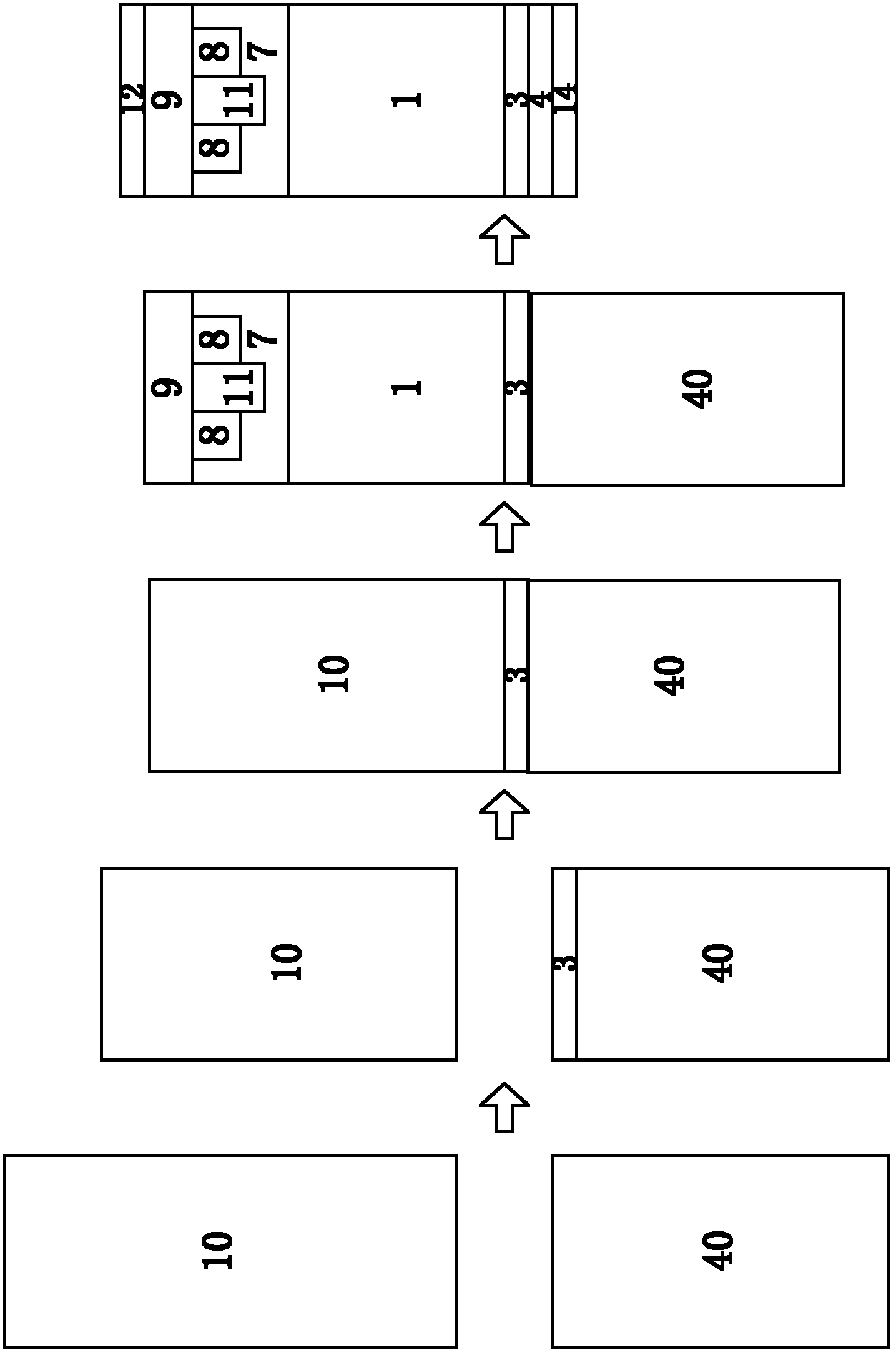

[0055] see Figure 4 , which is the second embodiment of the method for manufacturing a field-stop type IGBT device in the patch mode of the present invention, including the following steps:

[0056] In step 1', the first silicon substrate 10 and the second silicon substrate 40 of single-crystal silicon are selectively melted, and the first silicon substrate 10 is thinned to 50-300 μm, preferably 60 μm, and the second silicon substrate The front side of 40 forms n-type heavily doped field stop region 3 by ion implantation and annealing process.

[0057] In step 2', the second silicon substrate 40 is thinned from the back to 300-700 μm, preferably 600 μm.

[0058] In step 3', the back side of the first silicon substrate 10 and the front side of the second silicon substrate 40 (i.e. the surface of the n-type heavily doped field stop region 3) are formed into one body by a bonding process.

[0059] In the 4th step, the front structure of the IGBT device is manufactured on the f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More