Silicon through-hole test structure and corresponding test method

A technology of test structure and test method, applied in semiconductor/solid-state device test/measurement, measurement device, electromagnetic measurement device, etc., can solve the problems of high test cost, complex test structure, cumbersome detection, etc., and achieve simple structure and simple test. handy effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

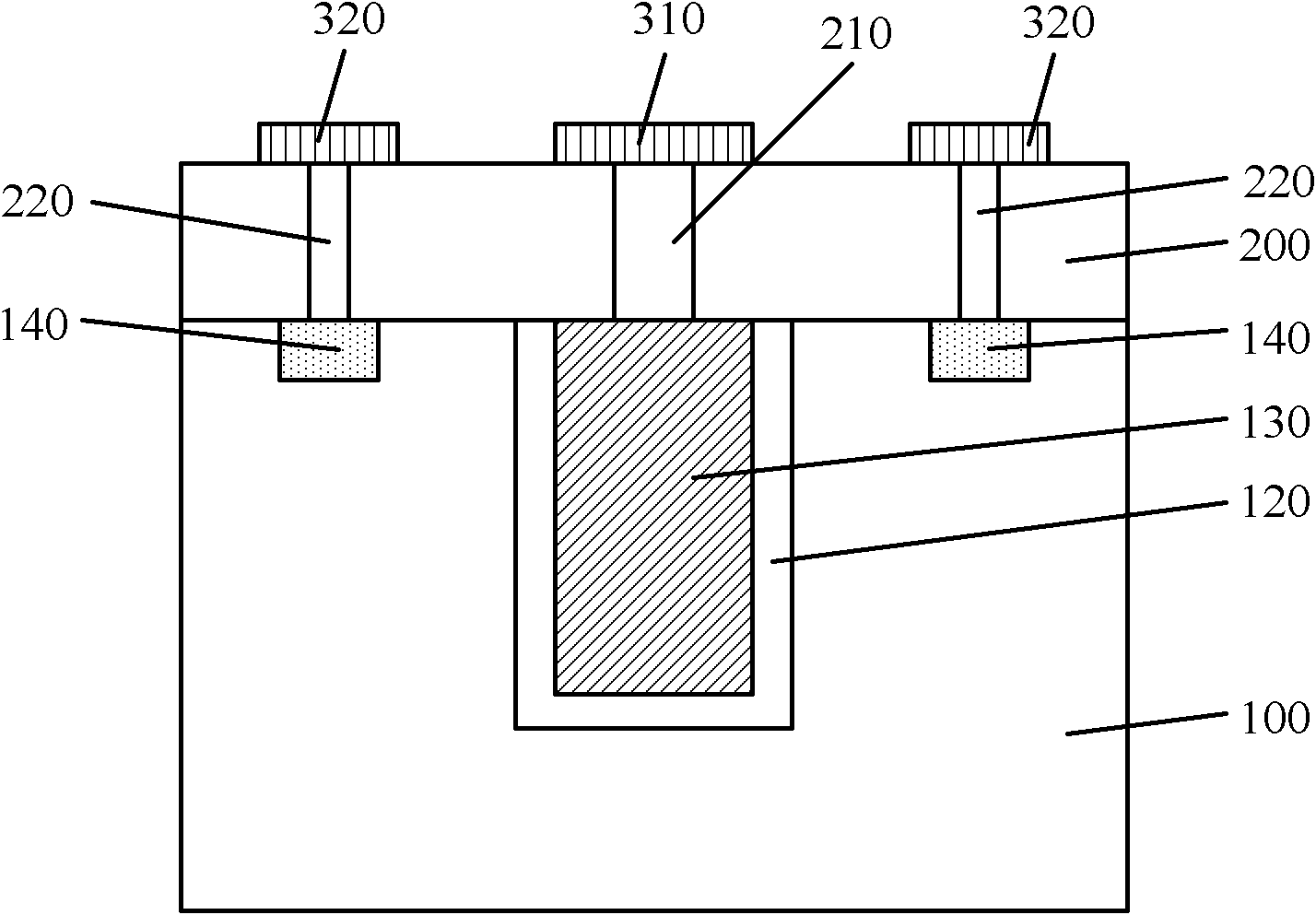

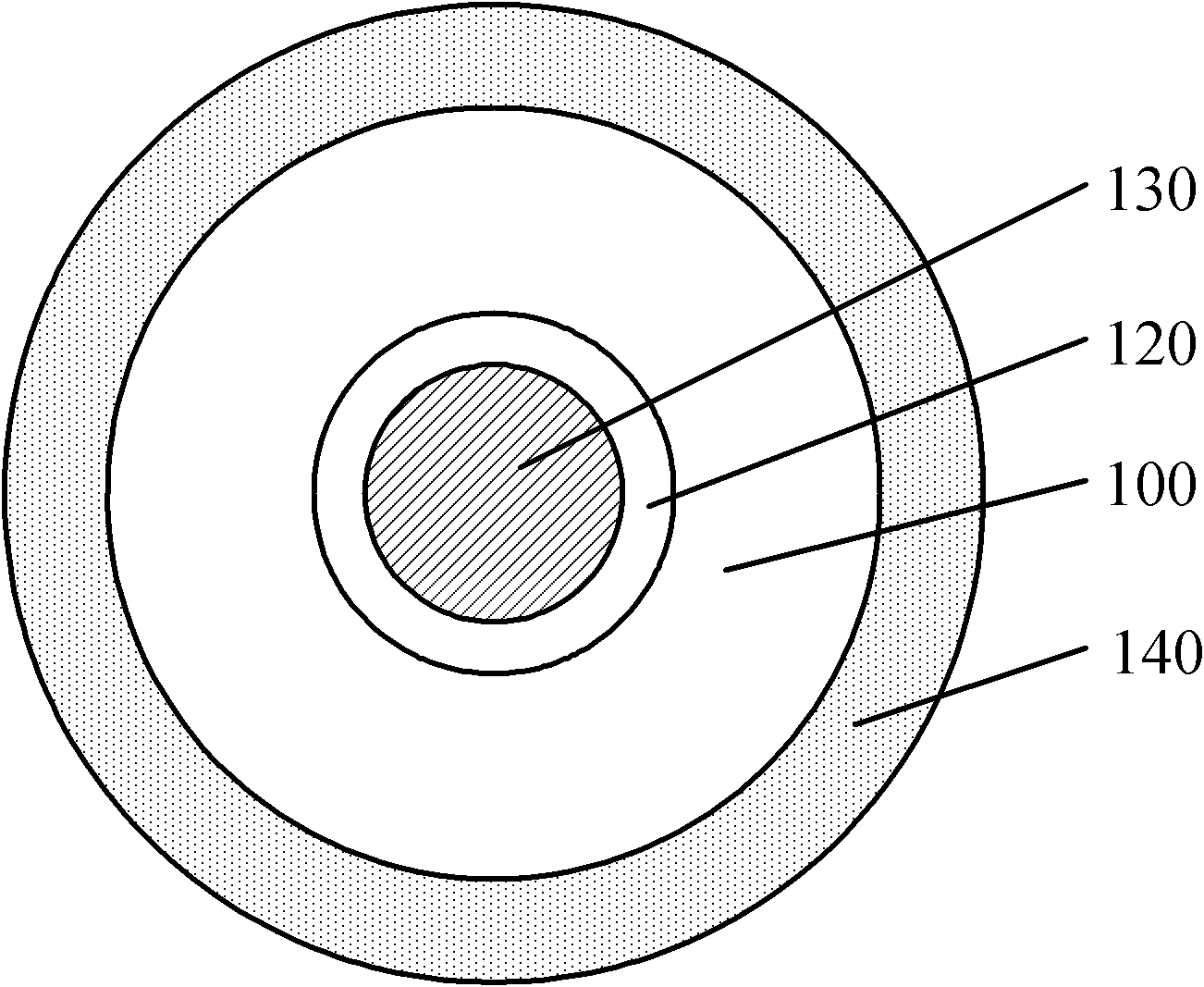

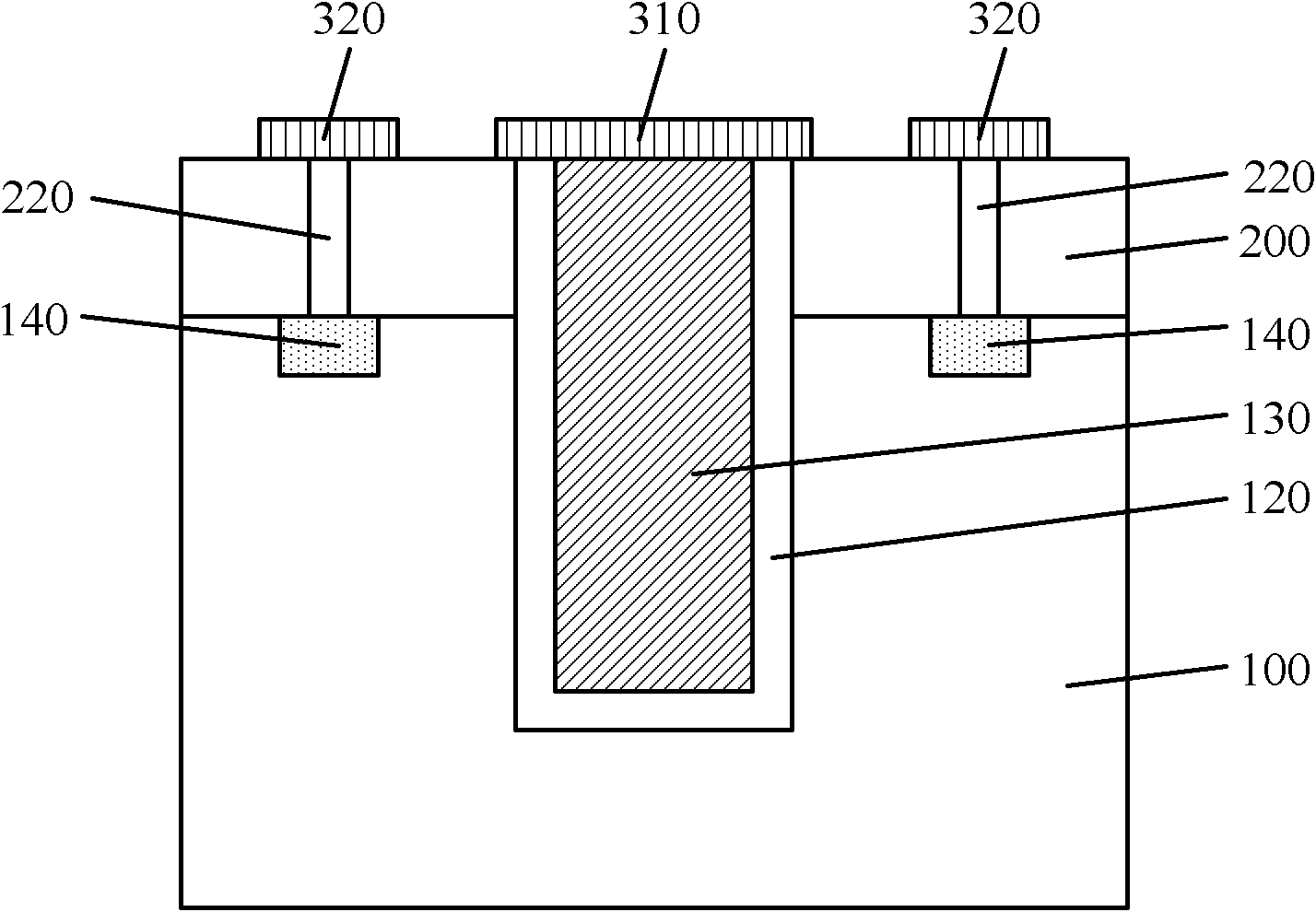

[0037] Since the depth of TSVs usually ranges from hundreds of nanometers to thousands of nanometers, and the diameter of TSVs is very small, it is difficult to etch silicon vias using conventional etching endpoint detection systems. The depth of the through-hole is precisely controlled, and if it is only controlled by the etching time, it is likely that the depth of the final formed through-silicon hole is very different from the standard value due to the difference in the wafer and the slight difference in the etching gas and power. . When the semiconductor substrate undergoes chemical mechanical polishing to expose the bottom of the through-silicon hole in the subsequent process, the through-silicon hole whose depth is greatly different from the standard value may not be exposed, making the electrical connection between different chips invalid. Therefore, in the existing technology, after the etching of the TSV is completed, the depth of the TSV needs to be detected, and un...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More