Fin type field effect transistor and manufacture method thereof

A technology of fin field effect and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems affecting the electrical performance of fin field effect transistors, and achieve the goal of avoiding parasitic capacitance and good electrical performance Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

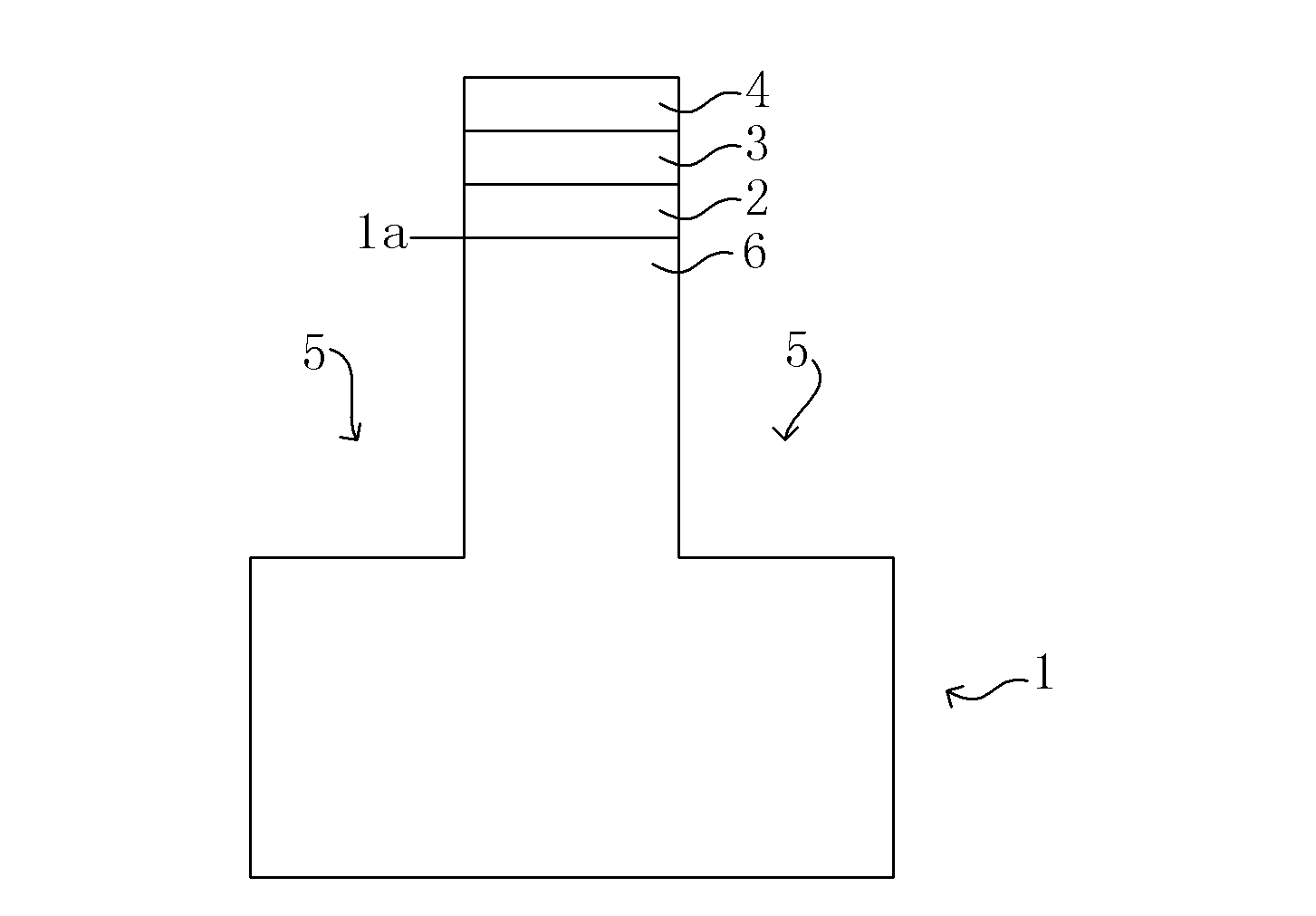

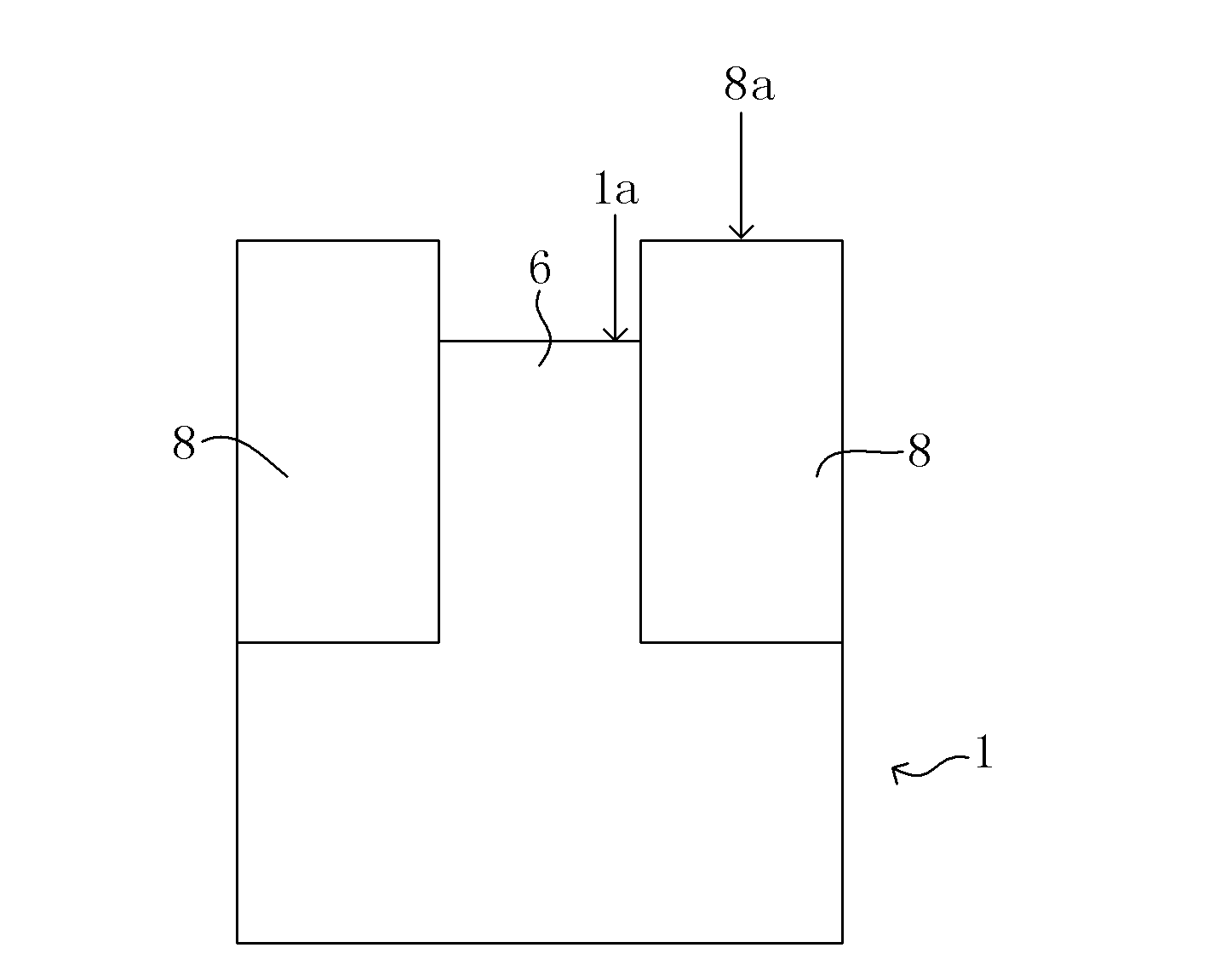

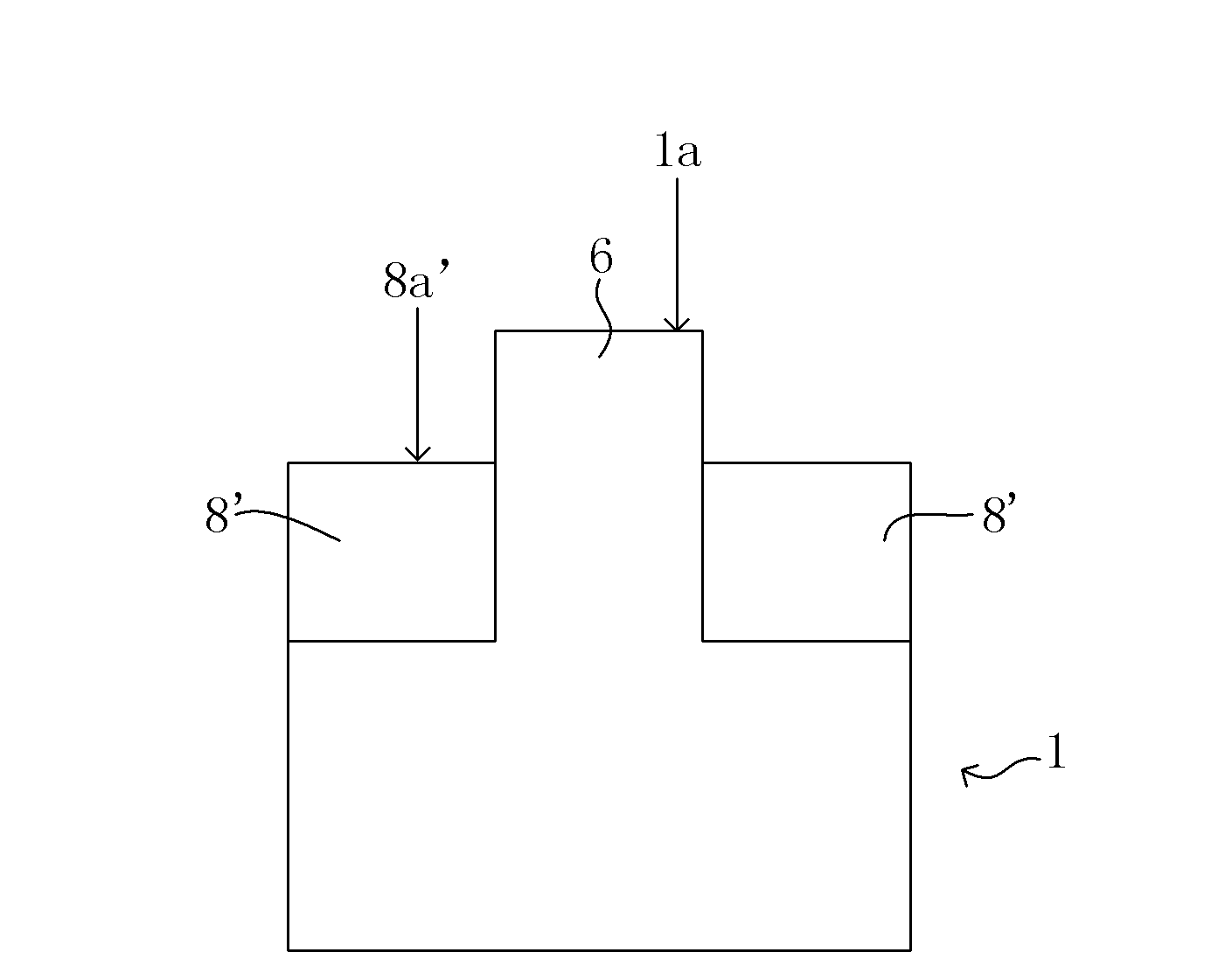

[0054] As mentioned in the background, there is a large parasitic capacitance between the metal gate and the source / drain of the fin field effect transistor in the prior art, which seriously affects the electrical performance of the fin field effect transistor. The inventor knows through analysis that the reason for this phenomenon is: as Figure 2D As shown, when using the gate-last process to form the metal gate 15 of the fin field effect transistor, although a higher-quality high-K gate dielectric layer 14 can be formed, while depositing the high-K gate dielectric layer 14, it will cause metal grid 15 both side walls ( Figure 2D Middle, left, and right vertical sidewalls) are attached with a high-K gate dielectric layer 14, which is a material with a large dielectric constant. In this fin field effect transistor structure, the metal gate 15, the source The / drain 16 and the high-K gate dielectric layer 14 generate parasitic capacitance with a large capacitance.

[0055] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More