High-performance low leakage power consumption master-slave type D flip-flop

A technology with leakage power and high performance, applied in the field of high-performance and low-leakage power master-slave D flip-flops, which can solve the problems of increasing the dynamic power consumption of flip-flops, increasing the silicon area of flip-flops, and increasing manufacturing costs. , to achieve the effect of saving leakage power consumption, simple timing switching, and simple circuit structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

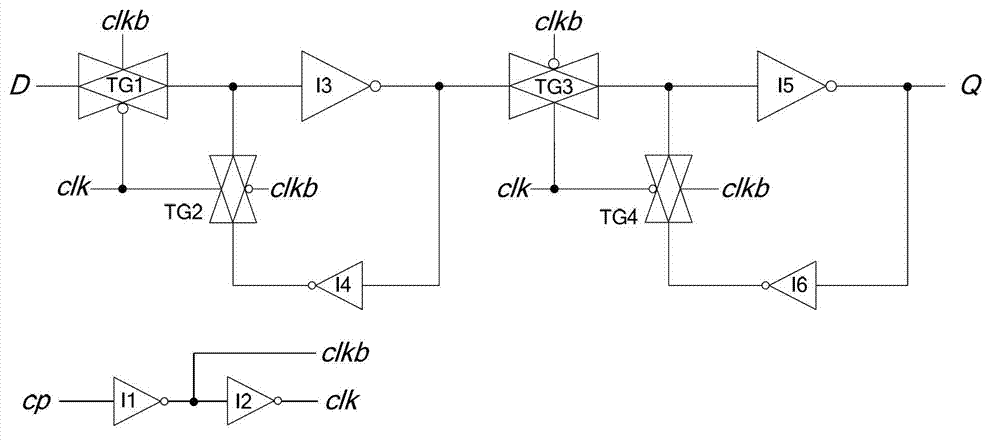

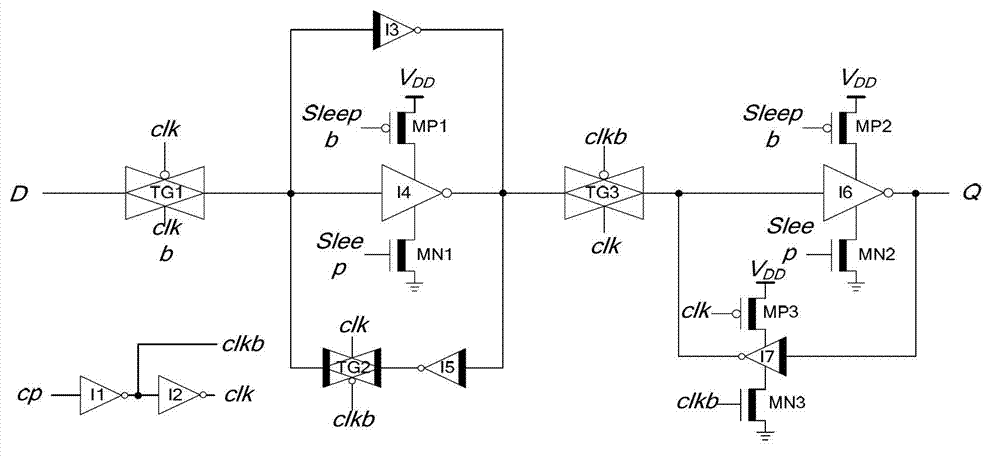

[0025]A high-performance low-leakage power consumption master-slave D flip-flop, including a clock signal inverter circuit, a master latch circuit, a slave latch circuit, an NMOS tube power control switch, a PMOS tube power control switch, and a holding inversion Device I5, the clock signal inverter circuit includes a first inverter I1 and a second inverter I2 for inverting the input clock signal, the output terminal of the first inverter I1 is connected with the second inverter The input terminal of I2 is connected, the main latch circuit includes the first transmission gate TG1, the second transmission gate TG2, the third inverter I3 and the fourth inverter I4, the output terminal of the first transmission gate TG1 is connected with the fourth inverter The input terminal of the phaser I4 is connected, the non-inverting control terminal of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More