Imaging array of pixel units based on composite dielectric grid structure and exposure operation method of imaging array

A pixel unit and composite medium technology, applied in the direction of electrical components, image communication, color TV components, etc., can solve the problems that the pixel size is difficult to further reduce, the yield and cost are not ideal, and the sensitivity and resolution are small. Achieve the effects of preventing crosstalk, increasing the density of imaging devices, and improving resolution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The structure of the detector of the present invention and its specific detection method will be described below with reference to the accompanying drawings.

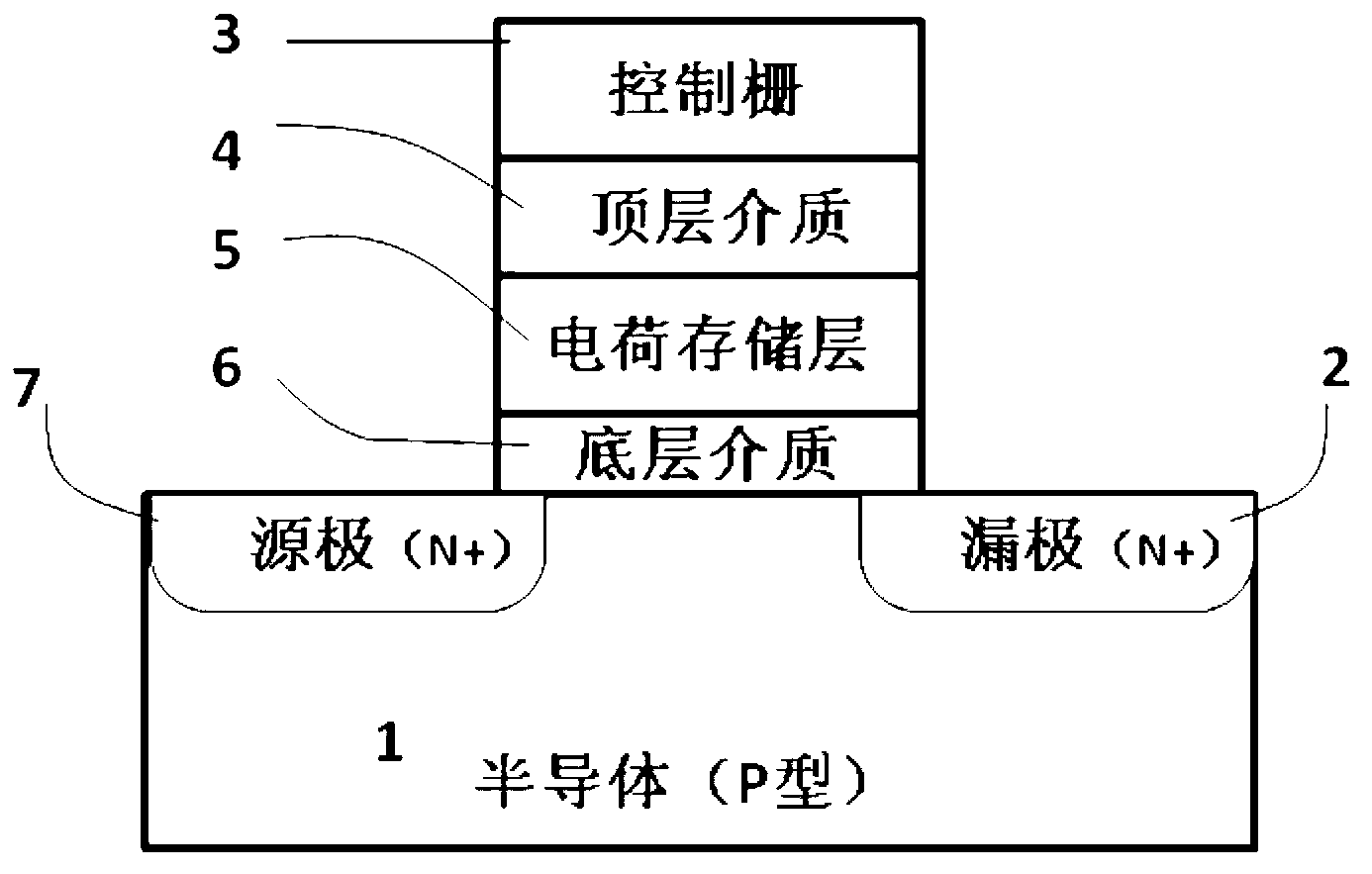

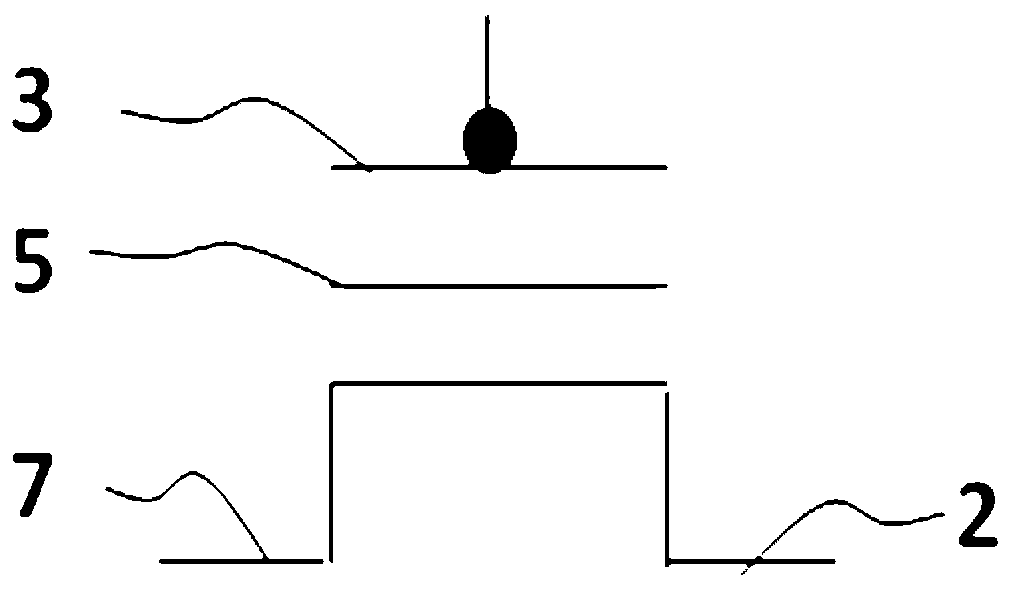

[0021] The present invention is based on the basic structure of the pixel involved in the imaging array of the composite dielectric grid structure pixel unit and its exposure operation method, such as Figure 1a Shown is the pixel structure (refer to WO2010 / 094233, the thickness of the dielectric material can be referred to), including a P-type semiconductor substrate (1), an N-type drain region (2), and an N-type source region (7). From top to bottom, there are a control gate (3), a top dielectric (4), a charge storage layer (5), and a bottom dielectric (6). Figure 1b It is a representation diagram of a pixel structure circuit, (3) a gate, (5) a charge storage layer, (2) and (7) are N-type injection regions with a symmetrical structure.

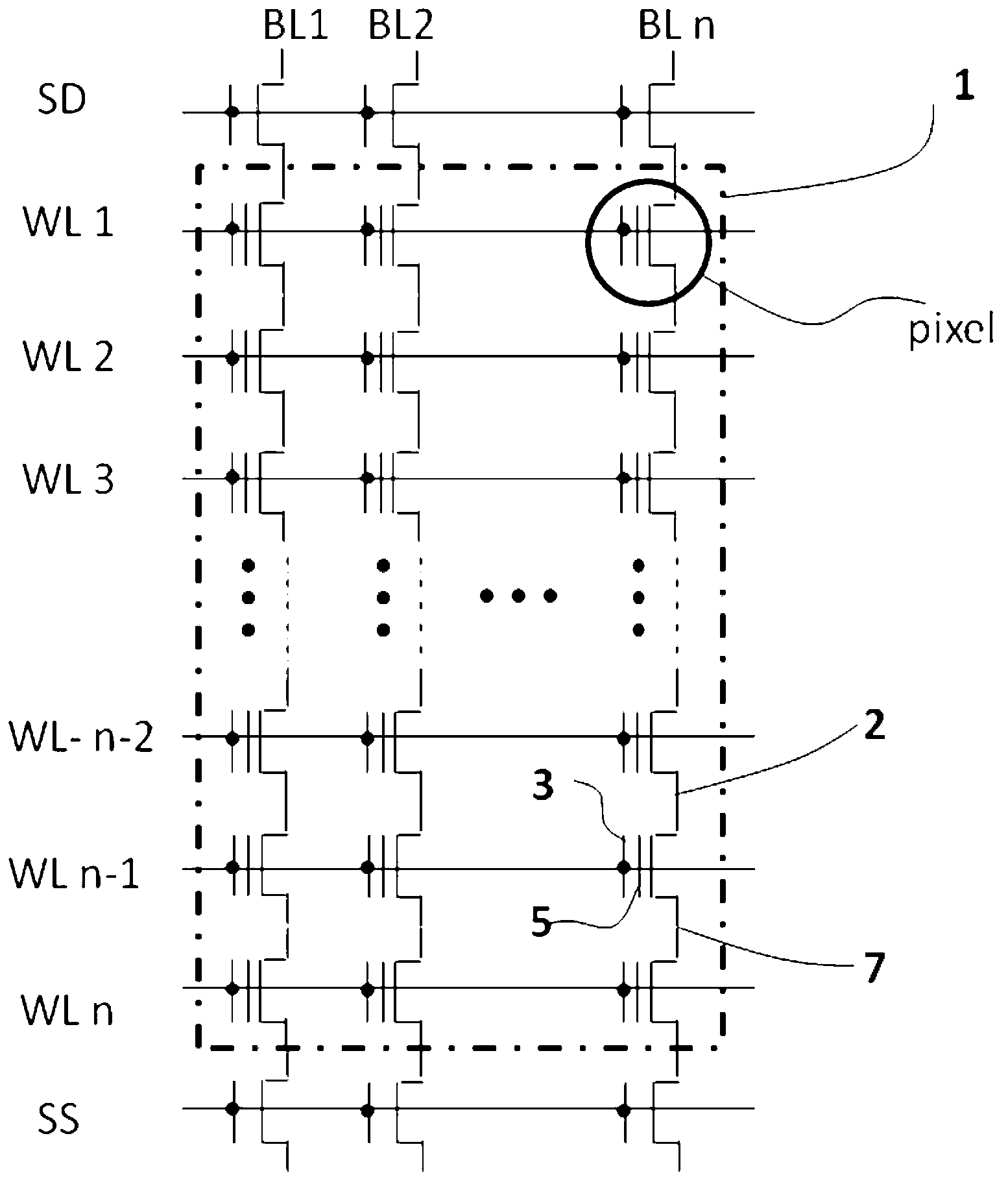

[0022] The basic structure of the imaging array based on the compound die...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More