Hollow channel isolation region preparation method

A shallow trench isolation and manufacturing method technology, which is applied in the field of shallow trench isolation, can solve problems affecting device characteristics, etching residues, increasing the difficulty of etching polysilicon gates and silicon nitride sidewalls, etc. Achieve the effect of solving edge corners or sags, improving appearance, and facilitating subsequent processes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

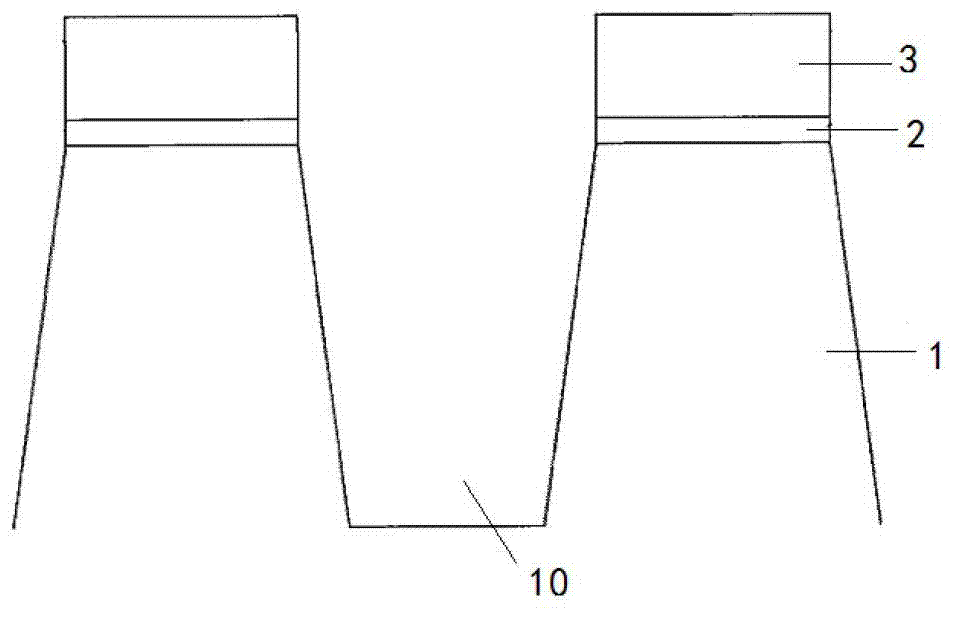

[0028] see Figure 1 to Figure 6 , the manufacturing method of the shallow trench isolation region of the present embodiment includes the following steps:

[0029] Step S01, providing a silicon substrate 1, and sequentially depositing SiO with a thickness of 15 nanometers on the silicon substrate 1 2 Layer 2 and SiN layer 3 with a thickness of 80 nanometers, and shallow trenches 10 are etched by STI manufacturing process;

[0030] Step S02, on the SiO on both sides of the shallow trench 10 2 Layer 2 cuts are etched, and the etching width is 14 nanometers, forming a groove 21;

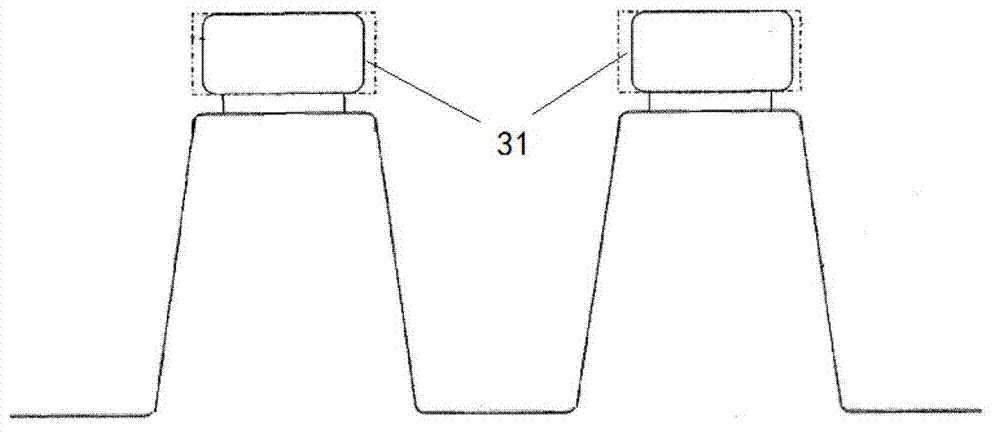

[0031] Step S03, perform the first etching back on the SiN layer 3 on both sides of the shallow trench 10, remove the first part of the SiN layer 31, the width of the etching back is 8 nanometers, and expose the bottom of the SiN layer 3 from the projection direction from top to bottom Part of the silicon substrate 1 below the groove 21;

[0032] Step S04, growing a layer of SiO on the surface of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More