Double-sided microchannel liquid-cooled power semiconductor whole-wafer flat-panel crimp package structure

A power semiconductor and micro-channel technology, applied in semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., can solve the problems of increased heat generation failure rate, large volume, and reduced contact area, and achieve long-term improvement. Reliability, high integratable power, avoidance of contact gap effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

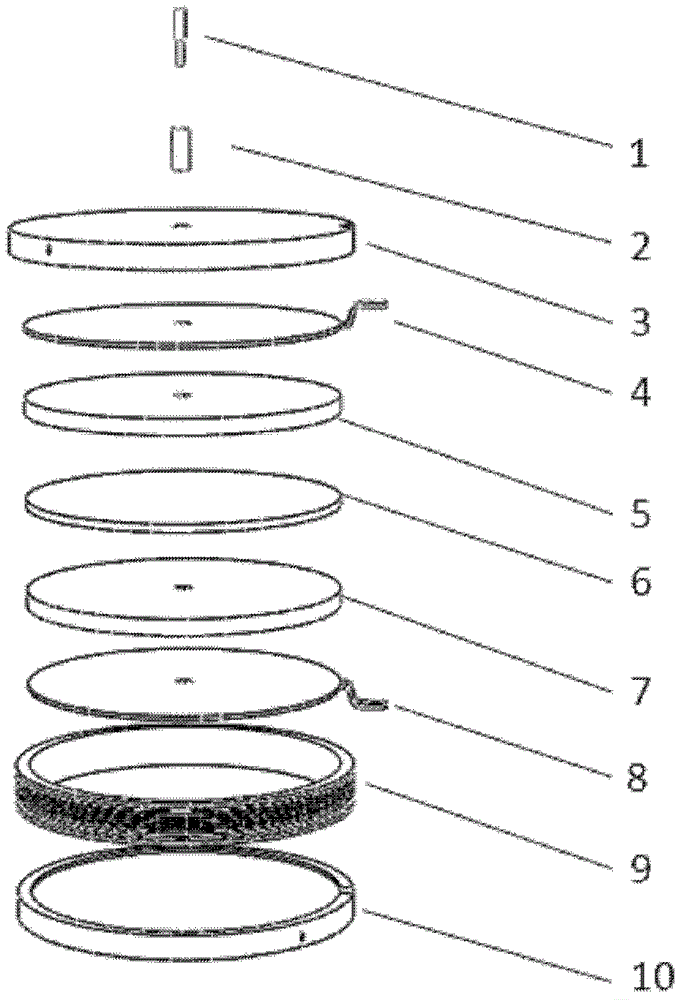

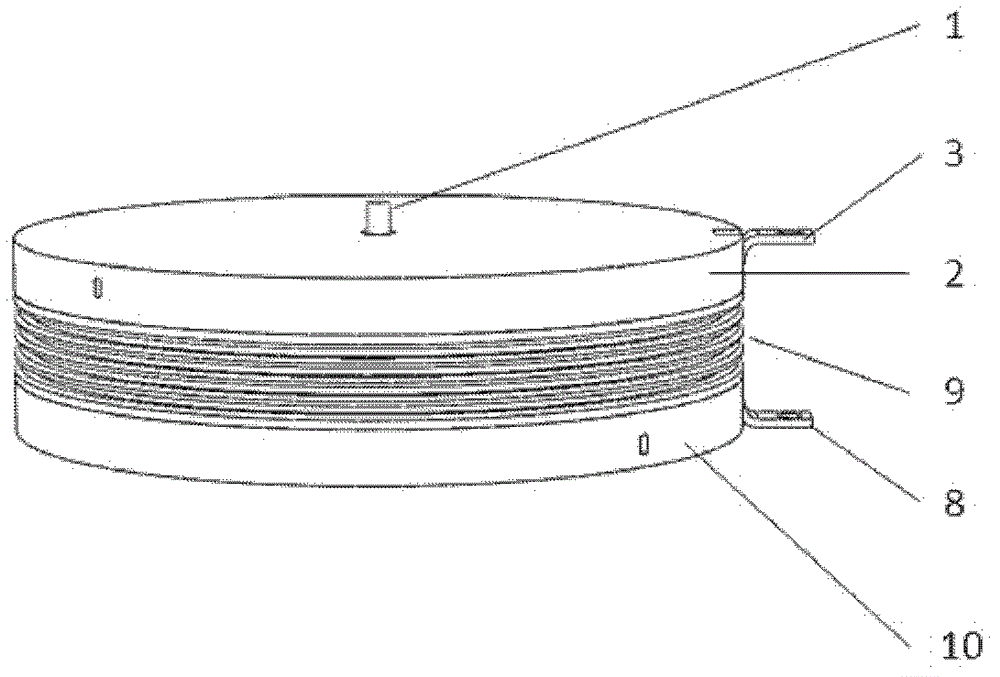

[0024] Embodiments of the present invention are further described below in conjunction with the accompanying drawings:

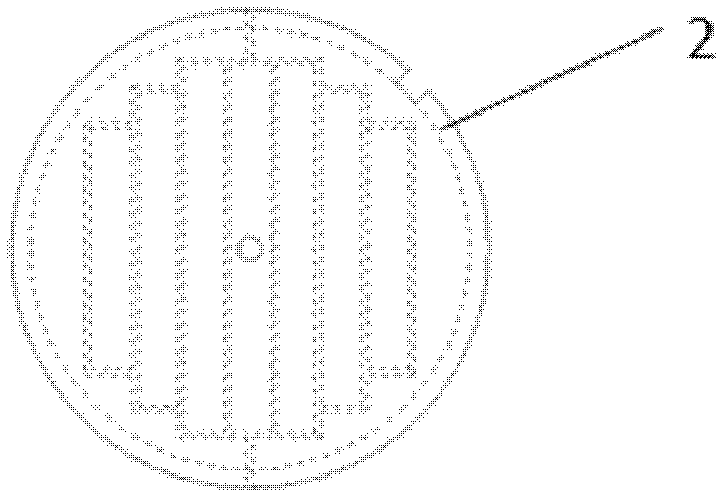

[0025] Known power semiconductor wafers usually contain tens to hundreds of identical semiconductor chips, and each chip is composed of thousands of identical units connected in parallel, and the emitter, gate and collector of each unit are connected through Metal or polysilicon films are connected together respectively. However, in the actual manufacturing process, it is difficult to ensure that every tiny unit on a complete wafer is completely qualified, and if unqualified units continue to be used, the entire wafer will fail. Therefore, if there are a small number of unqualified units when manufacturing wafers, they can be isolated during the manufacturing process, and the failure area is marked on the surface of the wafer, and then a polymer insulation pattern is prepared on the corresponding part of the graphite sheet to disconnect the failure area , w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More