1T1R and 1R resistive random access memory integrated structure and implement method thereof

A resistive memory, 1.1T1R technology, applied in the field of microelectronics, can solve the problem of high processing cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

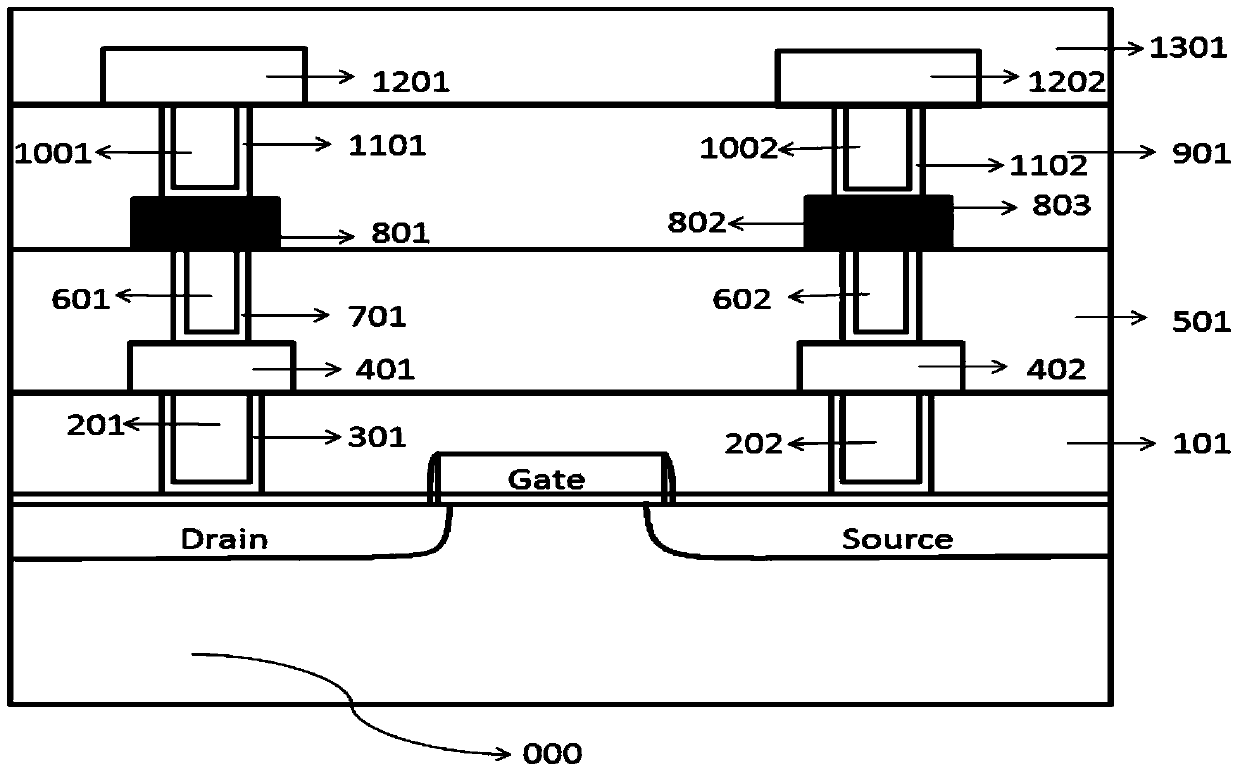

[0049] Embodiment 1 of the present invention provides an integrated structure of 1T1R and 1R resistive memory, and the composition structure diagram is as follows figure 1 As shown, it specifically includes: substrate transistor 000, first layer metal pre-dielectric 101, first layer plugs 201 and 202, first layer metal 401 and 402, second layer interlayer dielectric 501, second layer plugs 601 and 602 , MIM structure layers 801, 802 and 803, a third layer of interlayer dielectric 901, a third layer of plugs 1001 and 1002, a second layer of metal 1201 and 1202, and a passivation layer 1301.

[0050] In the integrated structure of 1T1R and 1R resistive memory, a resistive memory with a MIM structure layer is fabricated on the drain and source of the substrate transistor respectively, thereby realizing the integration of 1T1R and 1R. The integration of the 1T1R structure and the 1R structure facilitates the comparison of the characteristics of the RRAM in the two structures, and ...

Embodiment 2

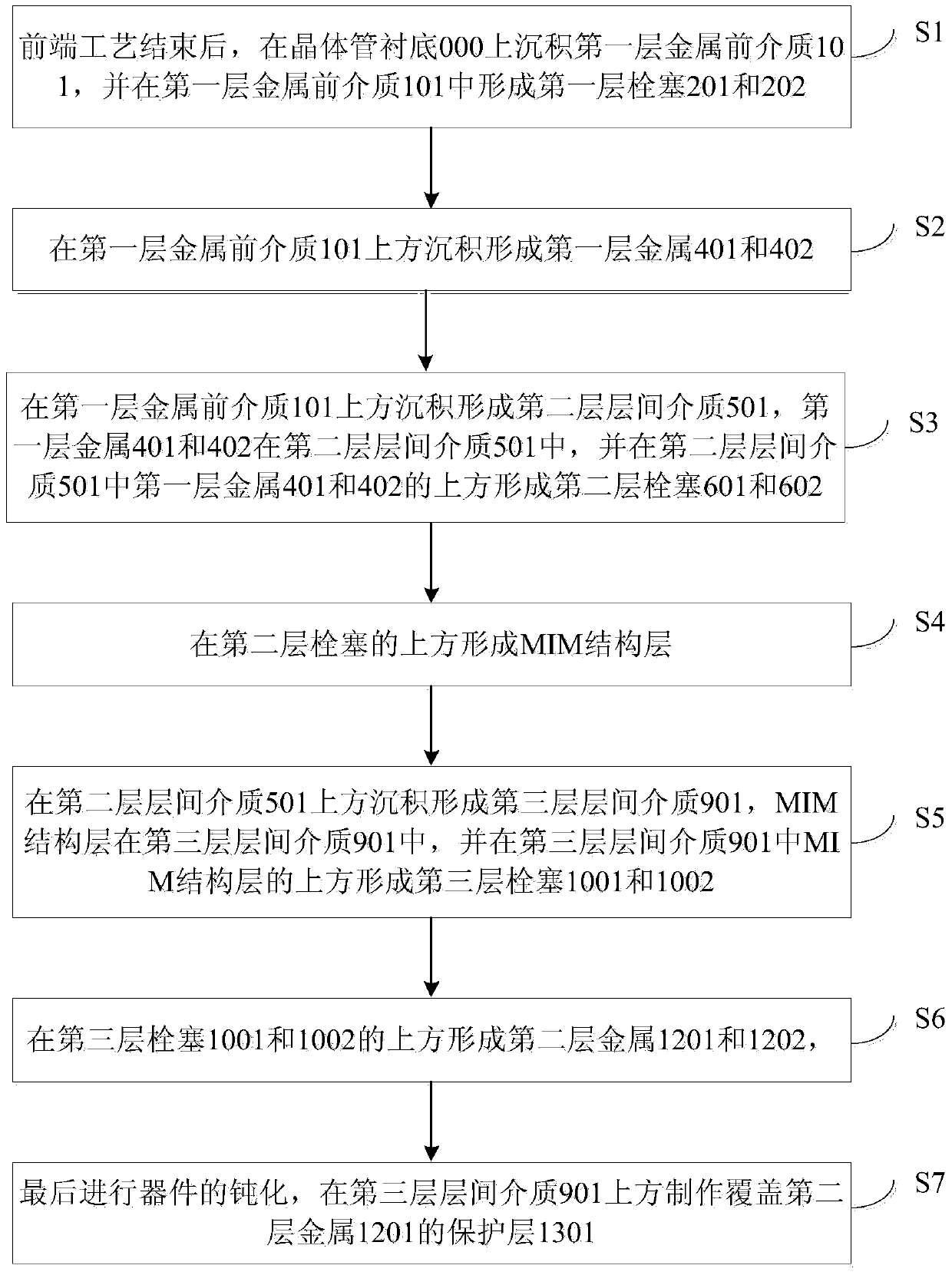

[0057] Embodiment 2 of the present invention provides a method for realizing the integrated structure of the 1T1R and 1R resistive variable memory, including: fabricating the resistive variable memory at the source and drain of the substrate transistor at the same time, and realizing the connection between the substrate transistor and the drain through the drain and source A series connection of resistive memory.

[0058] The steps of fabricating the resistive variable memory at the source and drain of the substrate transistor are as follows: figure 2 As shown, it specifically includes the following steps:

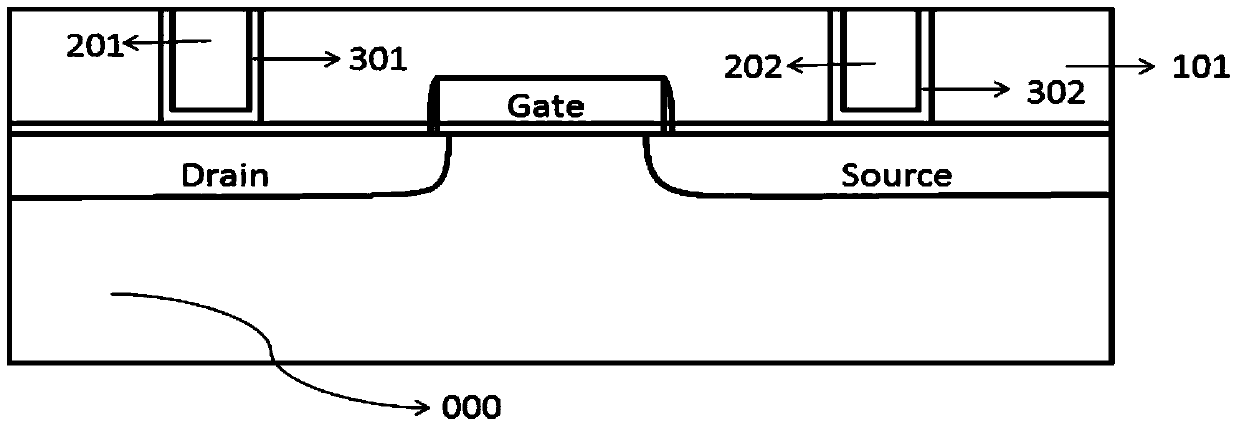

[0059] Step S1, after the front-end process is completed, the first layer of pre-metal dielectric 101 is deposited on the substrate transistor 000, and the first layer of plugs 201 and 202 are formed in the first layer of pre-metal dielectric 101. The first layer of plugs 201 and 202 are respectively Formed on the drain Drain and the source Source of the substrate transi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More