Method of forming FinFET gate medium layer and method of forming FinFET

A gate dielectric layer and transition layer technology, applied in electrical components, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of surface roughness and lattice mismatch of semiconductor fins, and avoid charge trapping, roughness, etc. The effect of reducing the temperature and improving the performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] In order to describe the principles and features of the present invention in conjunction with the accompanying drawings, the examples given are only used to explain the present invention, not to limit the scope of the present invention.

[0033] Such as figure 2 A method of forming a FinFET gate dielectric layer of the present invention shown, comprising:

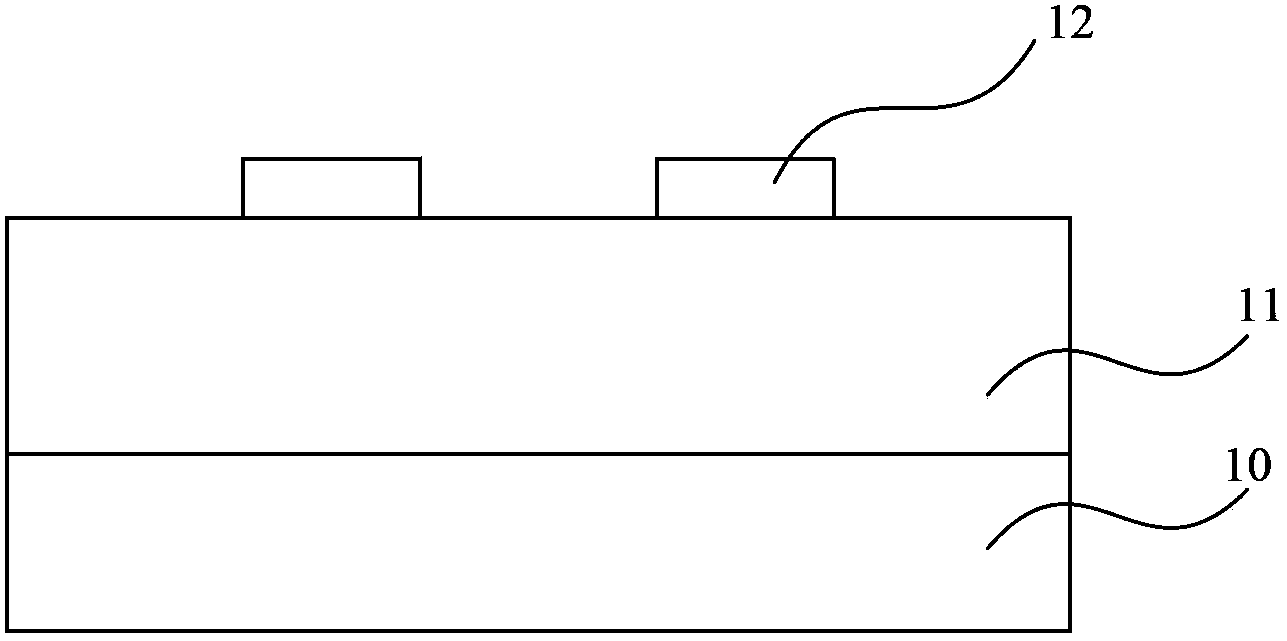

[0034] providing a semiconductor substrate formed with semiconductor fins;

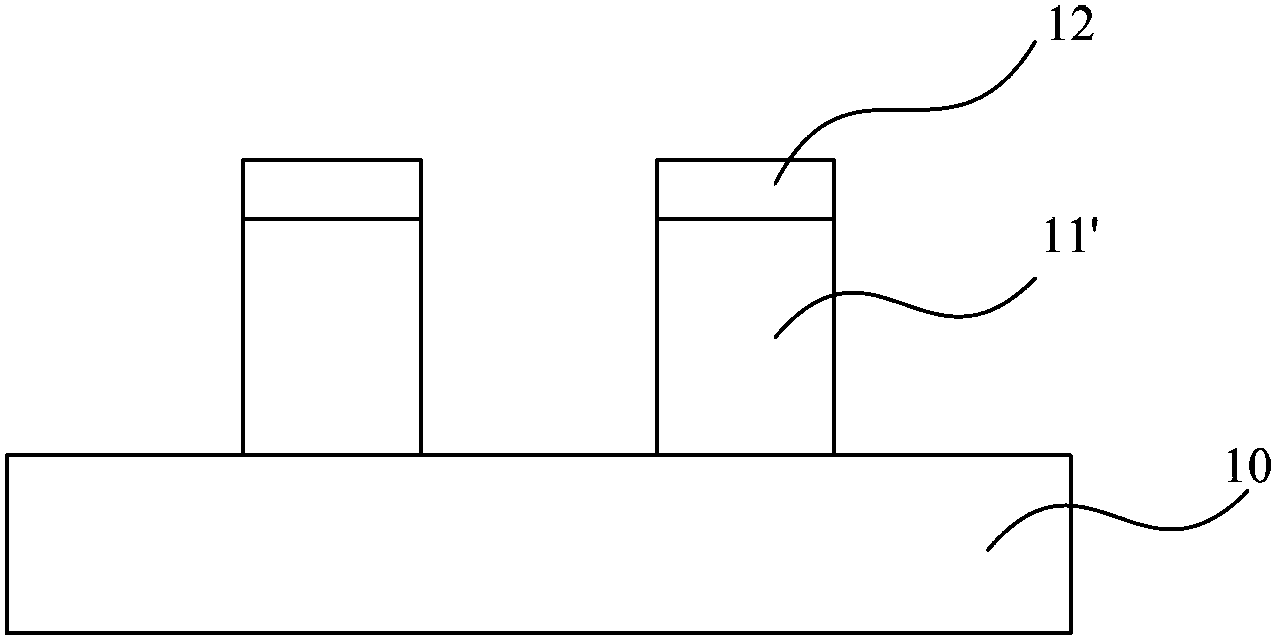

[0035] Epitaxially growing a single crystal silicon layer on the surface of the semiconductor fin, and annealing the semiconductor substrate in a mixed gas atmosphere of deuterium and an inert gas, so as to form a transition layer on the surface of the semiconductor fin;

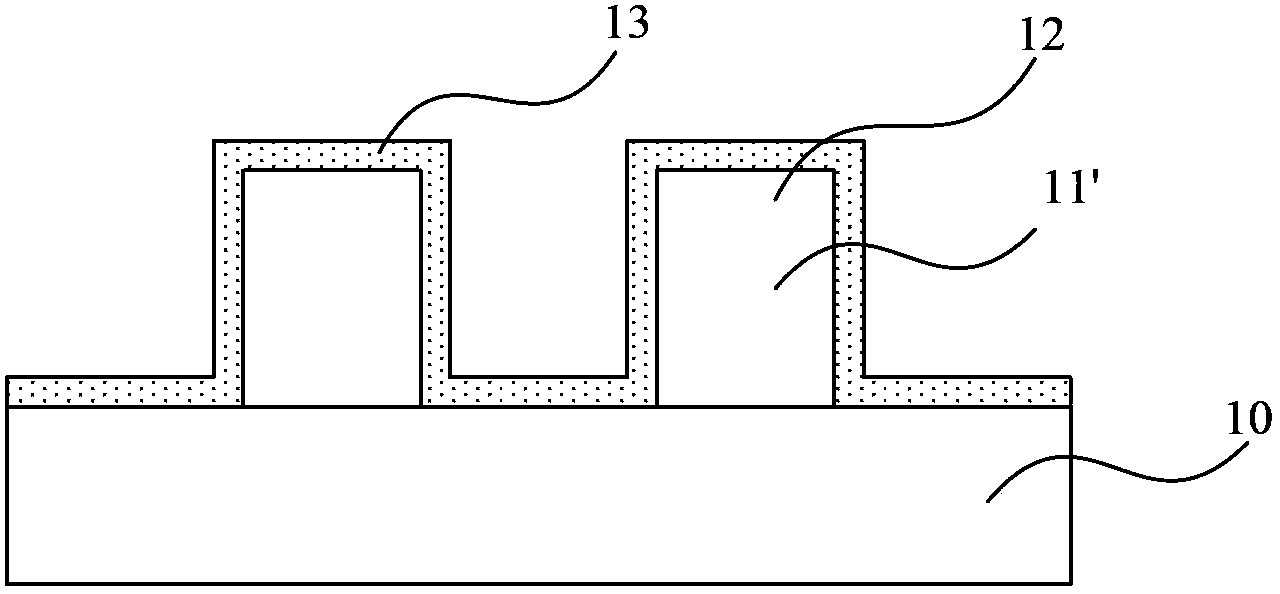

[0036] A gate dielectric layer is formed on the surface of the semiconductor substrate and the transition layer.

[0037] In order to specifically illustrate the mechanism of the present invention, as a typical embodiment of a method for forming a FinFET disclosed in th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More