Testing method and device of LVDS (low voltage differential signaling) interface of SOC (system on chip)

A technology of interface testing and chips, which is applied in the direction of frequency measurement devices, detecting faulty computer hardware, etc., can solve the problems of complex logic code and test vector writing, high test platform price, low test efficiency, etc., to reduce test cost, Inexpensive, easy-to-write effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

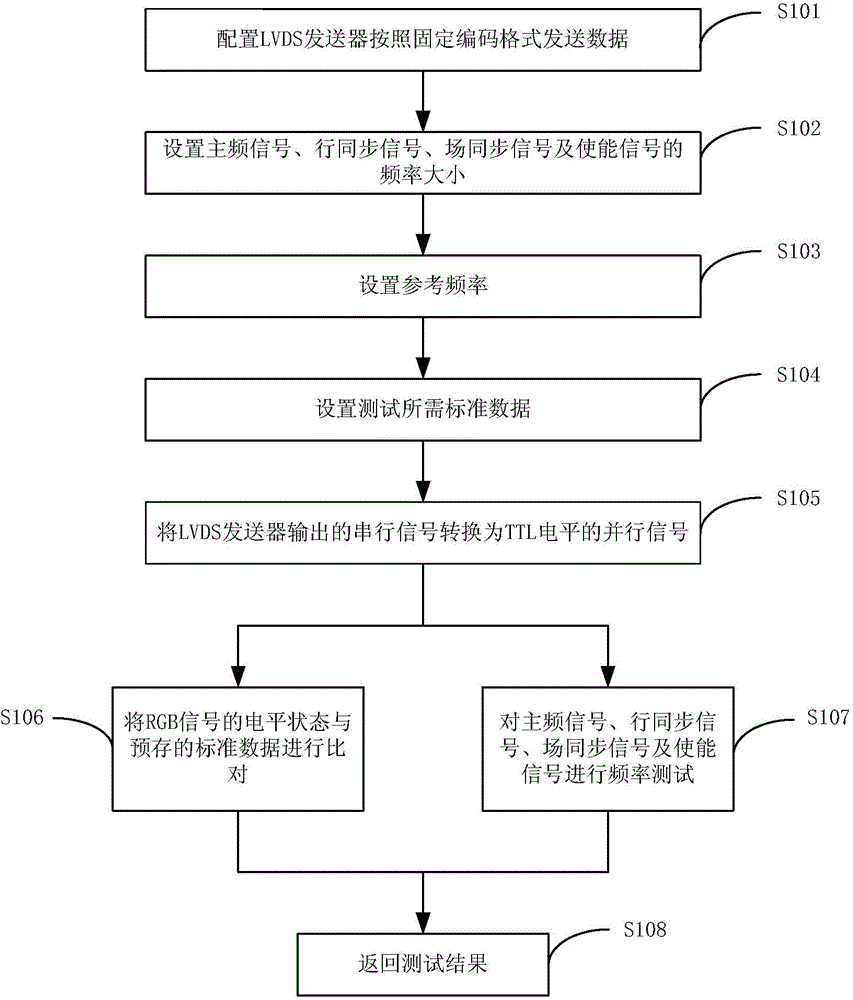

[0045] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

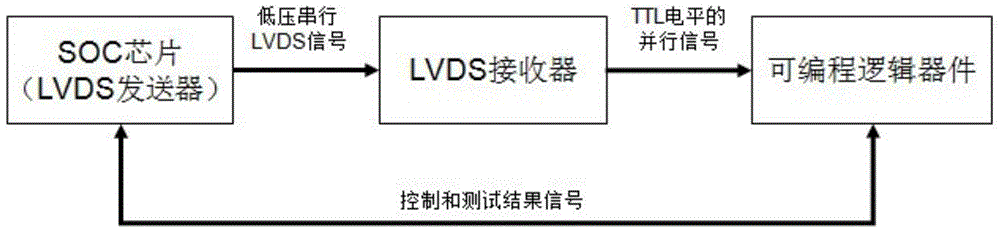

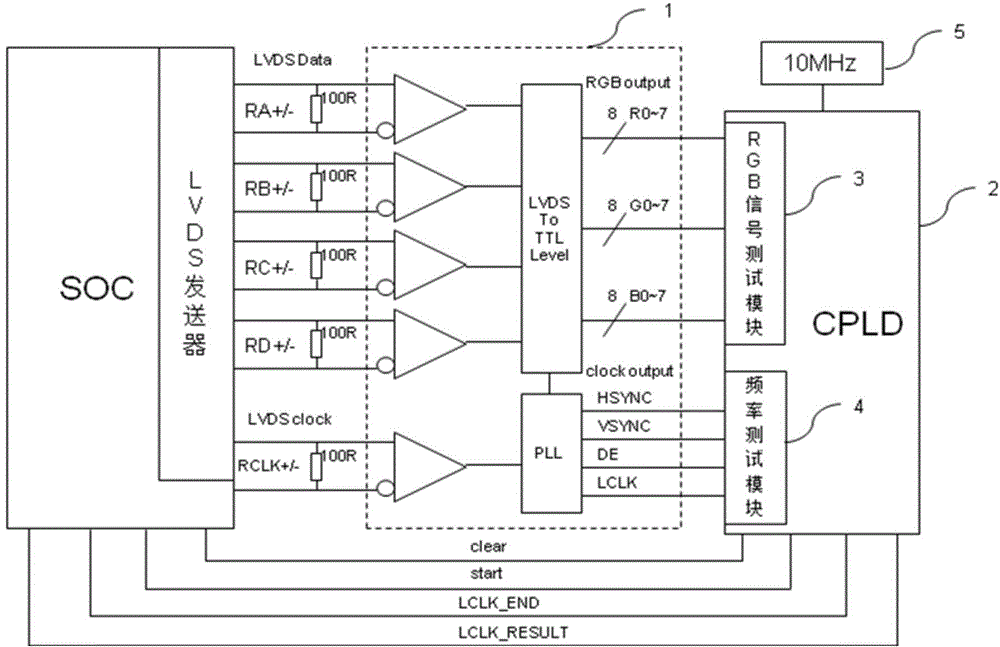

[0046] Such as figure 1 , figure 2 As shown, the SOC chip LVDS interface test device includes an LVDS receiver 1 and a programmable logic device 2, and the programmable logic device 2 can use CPLD (Complex Programmable Logic Device) or FPGA (Field-Programmable Gate Array). The LVDS receiver 1 converts the LVDS serial signal output by the LVDS transmitter integrated in the SOC chip into a TTL level parallel signal, and then tests the TTL level parallel signal through the programmable logic device 2. After the test is completed, the The SOC chip returns the test result.

[0047] The parallel signal of TTL level includes 24bit RGB signal and 4 channels of frequency signal, of which 24bit RGB signal includes R0~7, G0~7, B0~7, and 4 channels of frequency signal include main frequency signal LCLK, line synchronization signal HSYNC, field synchroni...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More