Formation method of electrical interconnection structure

It is a technology of electrical interconnection and conductive structure, which is applied in the manufacture of circuits, electrical components, semiconductors/solid-state devices, etc. It can solve problems such as poor stability and poor copper interconnection structure morphology, achieve stable performance, avoid damage, and simplify The effect of craft

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0042] Such as Figure 4 to Figure 8 Shown is a schematic cross-sectional structure diagram of the method for forming the electrical interconnection structure described in the first embodiment of the present invention.

[0043] Please refer to Figure 4 , provide a semiconductor substrate 300, the surface of the semiconductor substrate 300 has a dielectric layer 301, the dielectric layer 301 has a first opening 302 through its thickness.

[0044] The semiconductor substrate 300 is used to provide a working platform for subsequent processes; the semiconductor substrate 300 is a silicon substrate, a silicon-germanium substrate, a silicon carbide substrate, a silicon-on-insulator (SOI) substrate, a germanium-on-insulator (GOI) substrate, or a silicon-on-insulator (GOI) substrate. ) substrate, glass substrate or III-V compound substrate (such as silicon nitride or gallium arsenide, etc.).

[0045] There is a conductive layer 310 in the semiconductor substrate 300, the surface of...

no. 2 example

[0067] Such as Figure 9 to Figure 12 Shown is a schematic cross-sectional structure diagram of the method for forming the electrical interconnection structure described in the second embodiment of the present invention.

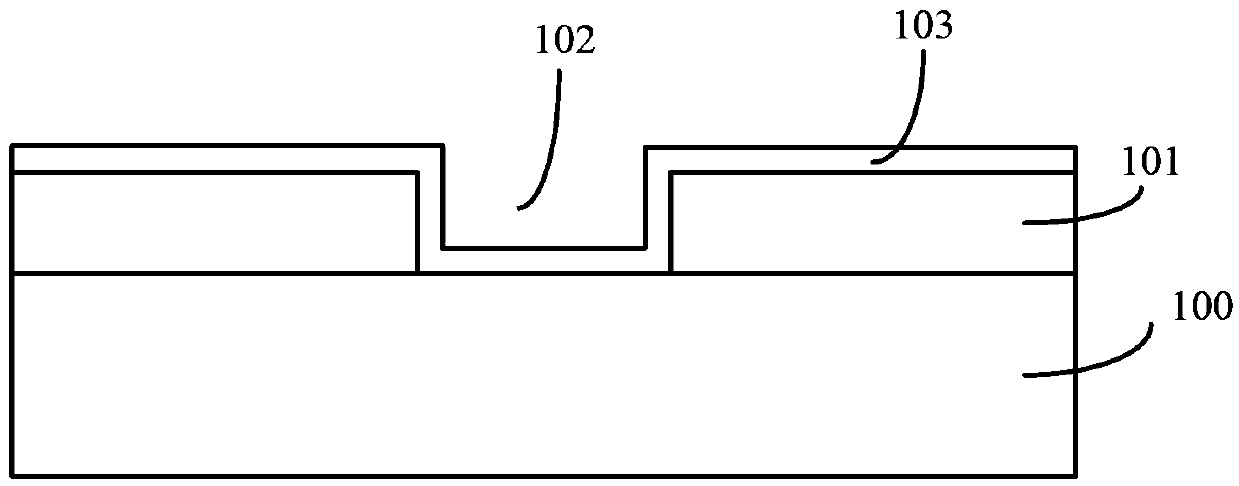

[0068] Please refer to Figure 9 , provide a semiconductor substrate 200, the surface of the semiconductor substrate 200 has a dielectric layer 201, the dielectric layer 201 has a first opening 202 through its thickness; on the surface of the dielectric layer 201 and the first opening 202 The sidewalls and bottom surface form the seed layer 203 .

[0069] The semiconductor substrate 200 , the dielectric layer 201 , the first opening 202 , the conductive layer 210 and the seed layer 203 are as described in the first embodiment, and will not be repeated here.

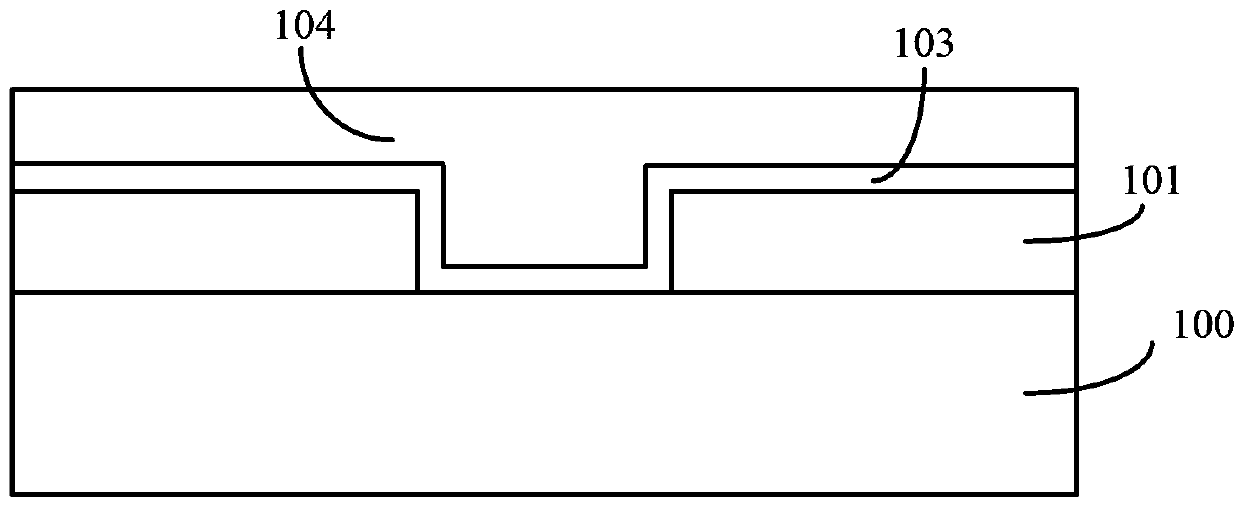

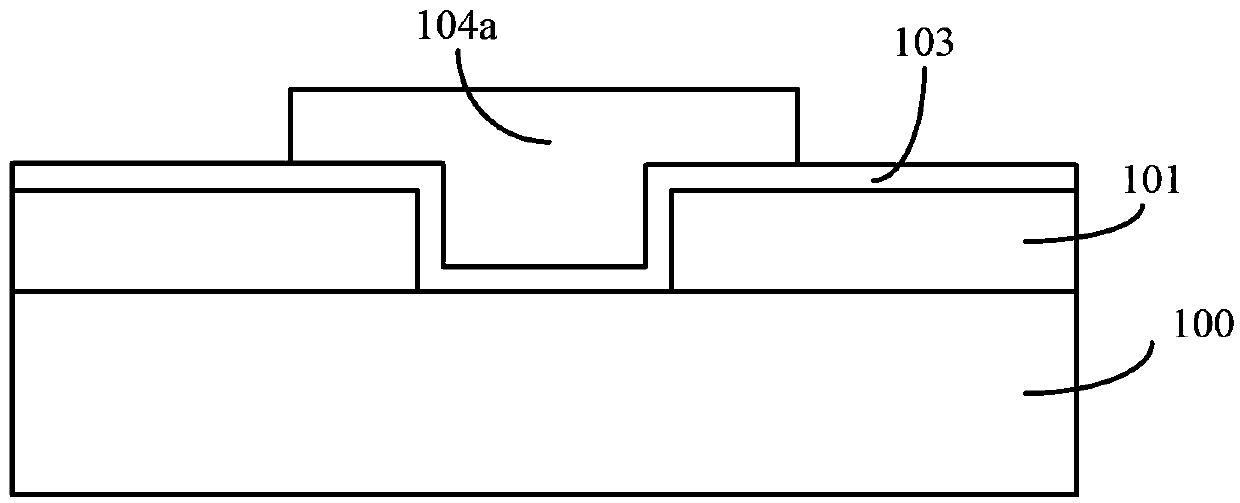

[0070] Please refer to Figure 10 , forming a first photoresist layer 204 on the surface of the seed layer 203, the material of the first photoresist layer 204 is a non-conductive photoresist, and th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More