Method for manufacturing double-layer polysilicon bipolar transistor

A bipolar transistor and manufacturing method technology, applied in transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problem of increasing the base-emitter distance, reducing the emitter current conduction area, reducing the current amplification factor, etc. The problem is to reduce the high-temperature process time, reduce the doping and up-expansion of the buried layer, and increase the current amplification factor.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

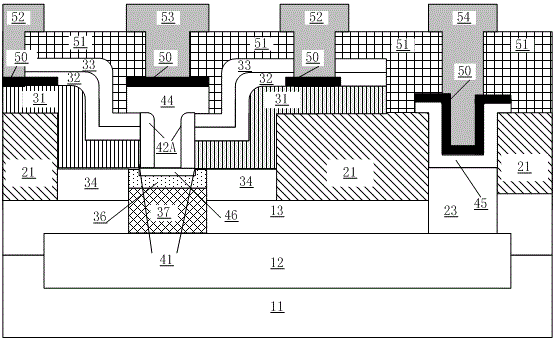

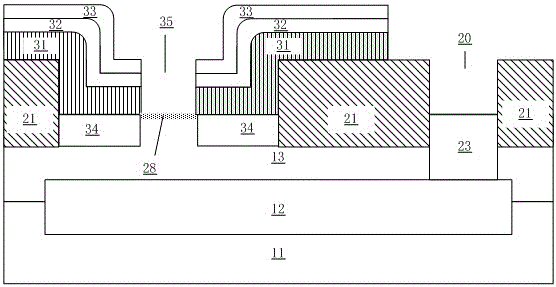

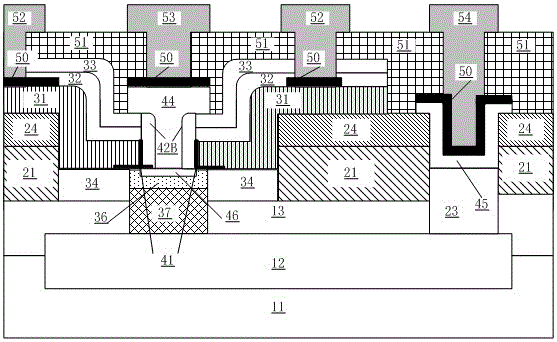

[0067] 1) Select the silicon substrate material 11, its doping is P-type, and the resistivity is 30Ω. cm; Sb atoms are selectively implanted on the substrate to form an N+ buried layer 12, followed by N-type silicon epitaxy 13, with a resistivity of 8Ω. cm, and the thickness of the epitaxial layer is 1.5 μm. ( Figure 2.2 )

[0068] 2) Oxidation to form thin SiO 2 Layer 14, 300Å thick, followed by deposition of Si 3 N4 15, thickness 1000Å, photolithography and dry etching of Si 3 N 4 , forming a local oxidation window, high temperature oxidation after degumming, to obtain LOCOS 21 with a thickness of 5000Å, an oxidation temperature of 1050 ° C, and a time of 45 minutes. After oxidation, the Si 3 N 4 . ( Figure 2.3 , Figure 2.4 )

[0069] 3) Lithograph the collector region 22, and implant phosphorus (P) atoms into the collector region with a dose of 5×10 15 / cm 2 , the energy is 150KeV, forming a low-resistance channel 23 . ( Figure 2.5 )

[0070] 4) CVD depo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com