Hardware Trojan horse test system

A test system and hardware Trojan technology, applied in the direction of digital circuit testing, electronic circuit testing, measuring electricity, etc., can solve the problems affecting the coordination and simplicity of automatic testing, reducing the testing accuracy of Trojan horses, and increasing system costs, so as to improve data Processing ability and real-time work, improve the level of automated testing, improve the effect of logic testing accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, and do not limit the protection scope of the present invention.

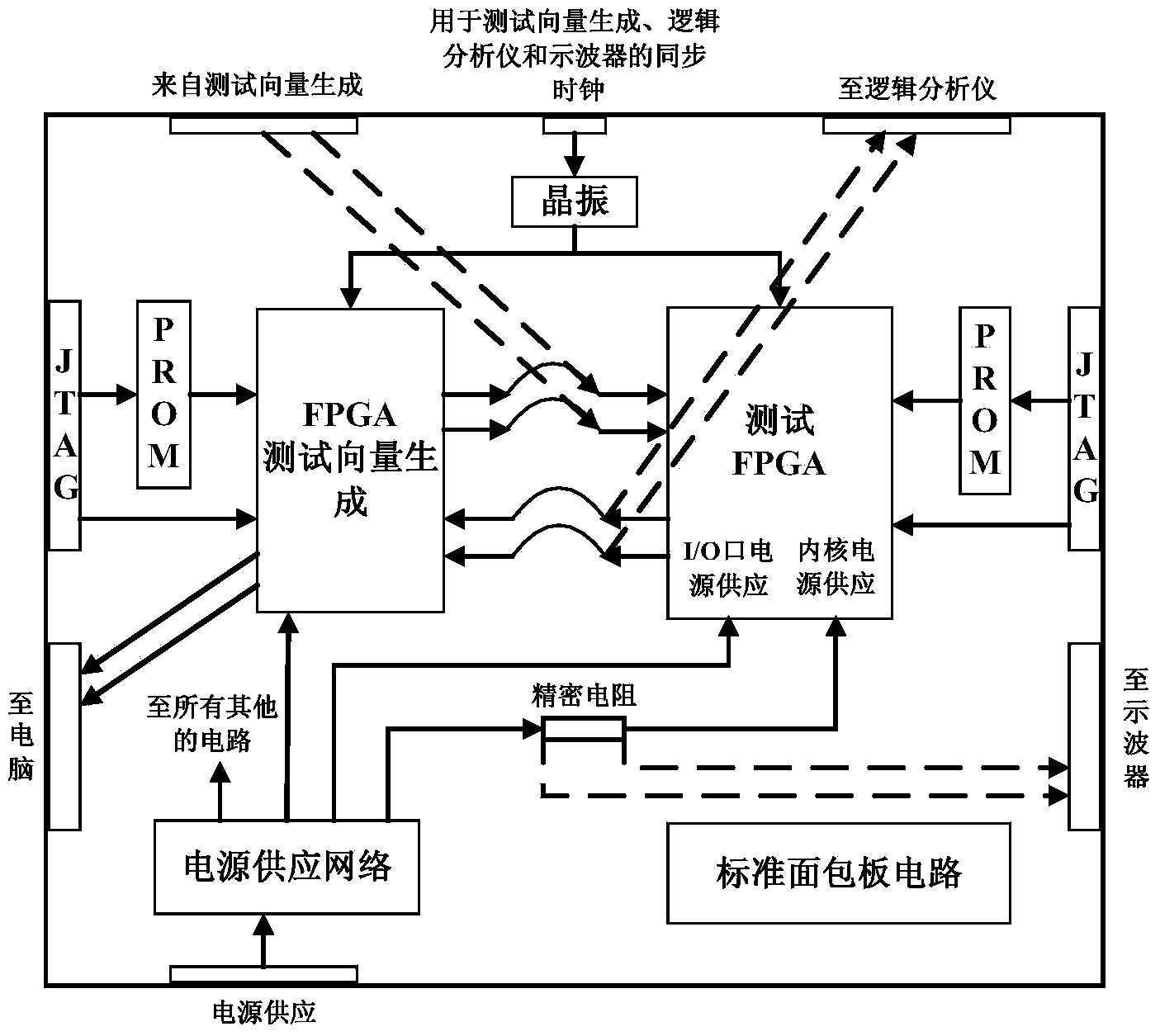

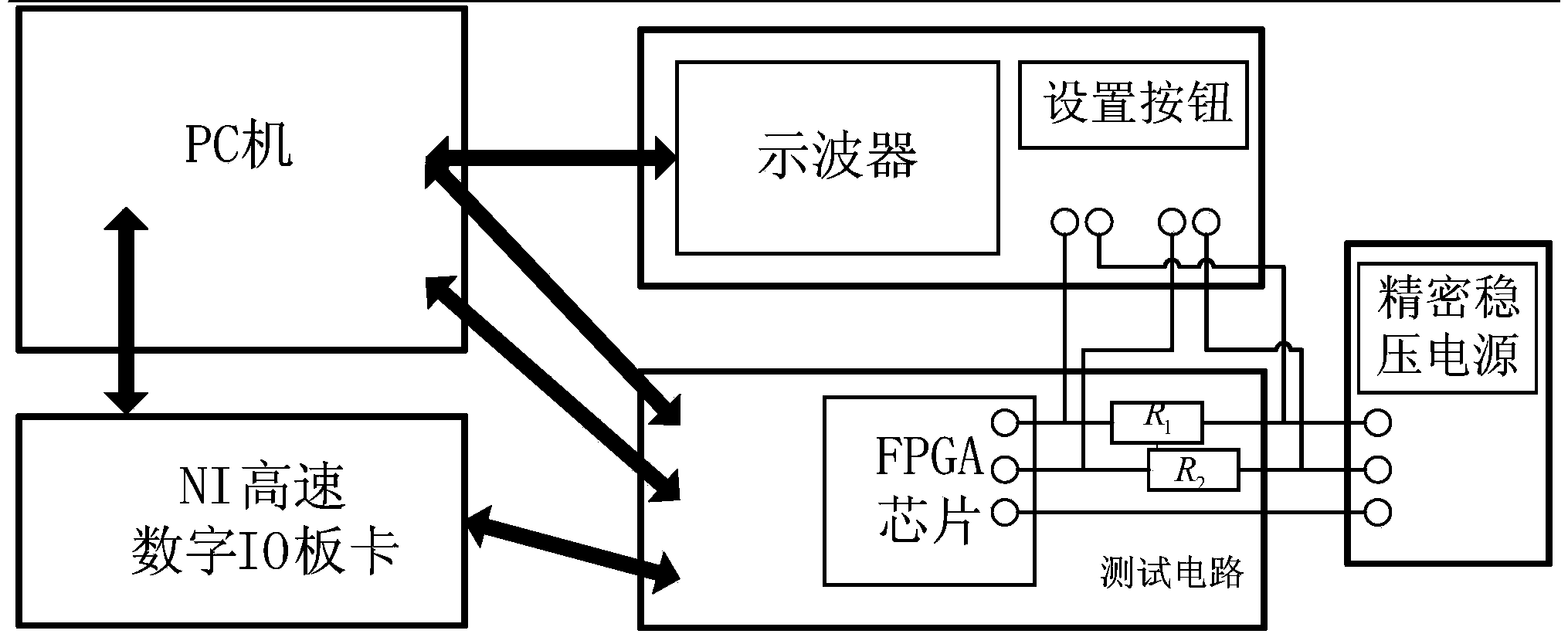

[0039] A hardware Trojan test system, such as image 3 shown, including:

[0040] PC, used to generate test vectors, program the FPGA chip in the test circuit; control the NI high-speed digital IO board, oscilloscope and the FPGA chip, and receive the response signal and the response signal returned by the NI high-speed digital IO board The acquisition signal sent by the oscilloscope is used for data processing; the PC is used as the upper computer to control the timing of the NI high-speed digital IO board, oscilloscope and FPGA chip to ensure the synchronous coordinat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More