Low-thickness and low-cost chip size package with cavity

A chip-size packaging, low-thickness technology, applied in the direction of electric solid devices, semiconductor devices, microstructure devices, etc., can solve the problems of easy generation of fragments, splinters, accelerated device failure, high cost, etc., to reduce peeling stress, improve Reliability and yield improvement effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The present invention will be described in more detail below with reference to accompanying drawing:

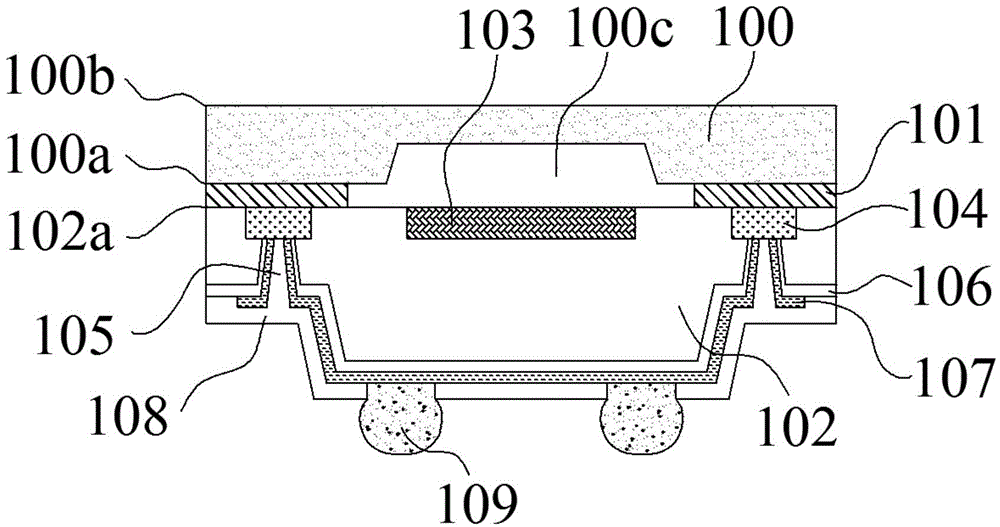

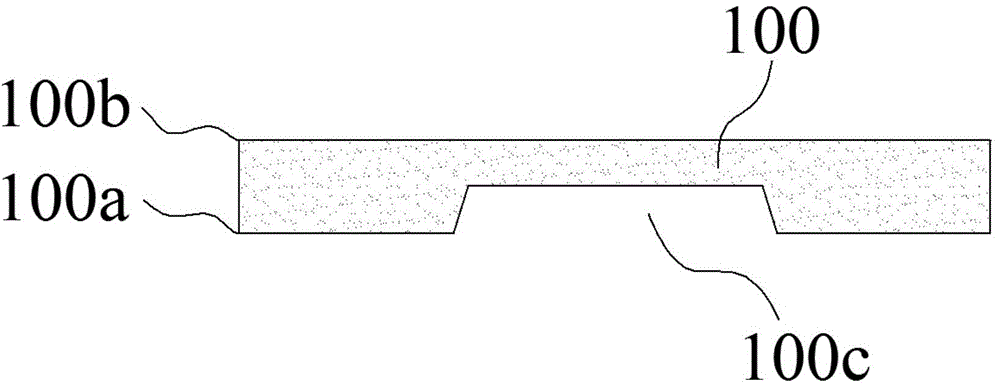

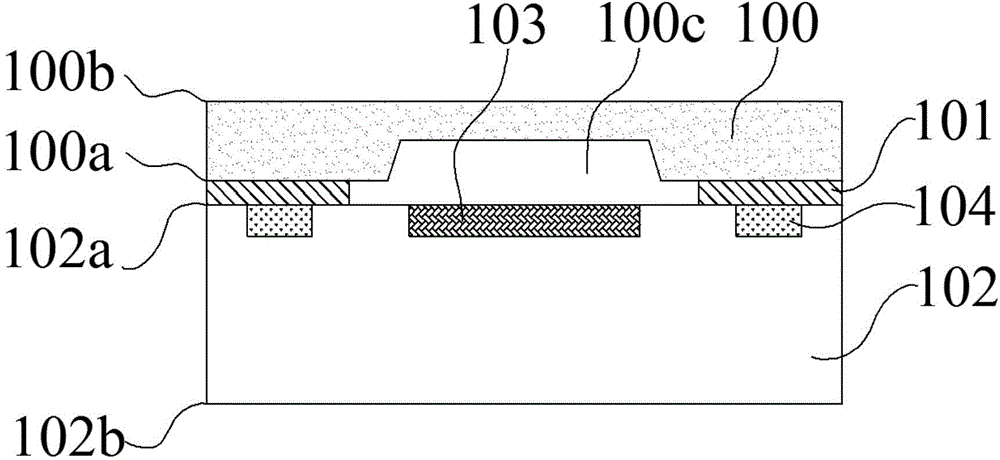

[0039] by figure 1 As shown, a cavity-containing low-thickness low-cost chip size package according to an embodiment of the present invention has a structure comprising:

[0040] 1. Cover plate 100, a cavity structure 100c is made on the cover plate front side 100a; 2. Wafer 102, which includes a wafer front side 102a and a wafer back side 102b; 3. Functional area 103 and pad 104, the functional area 103 and pads 104 are distributed on the front surface 102a of the wafer, wherein the pads 104 are distributed around the periphery of the function 103 and realize conduction; 4. The bonding glue 101 is located between the cover plate 100 and the wafer 102, and the 5. TSV 105, the TSV 105 exposes the pad 104, so that the conduction between the pad 104 and the subsequent redistribution layer is realized; 6. The redistribution circuit layer, the The redistribution circuit l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More