High-voltage fast turn-on thyristor and manufacturing method thereof

A thyristor, high-voltage technology, applied in the field of power semiconductor devices, can solve the problems of inability to maintain the technical level and the practicability of di/dt fast turn-on devices, so as to reduce device voltage drop, meet energy saving and consumption reduction, and improve uniformity. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

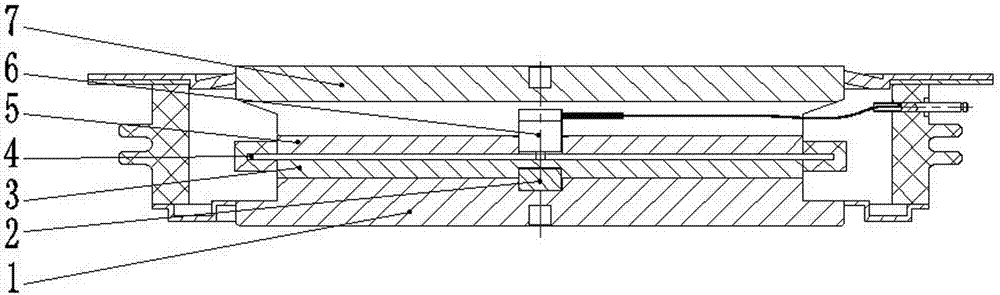

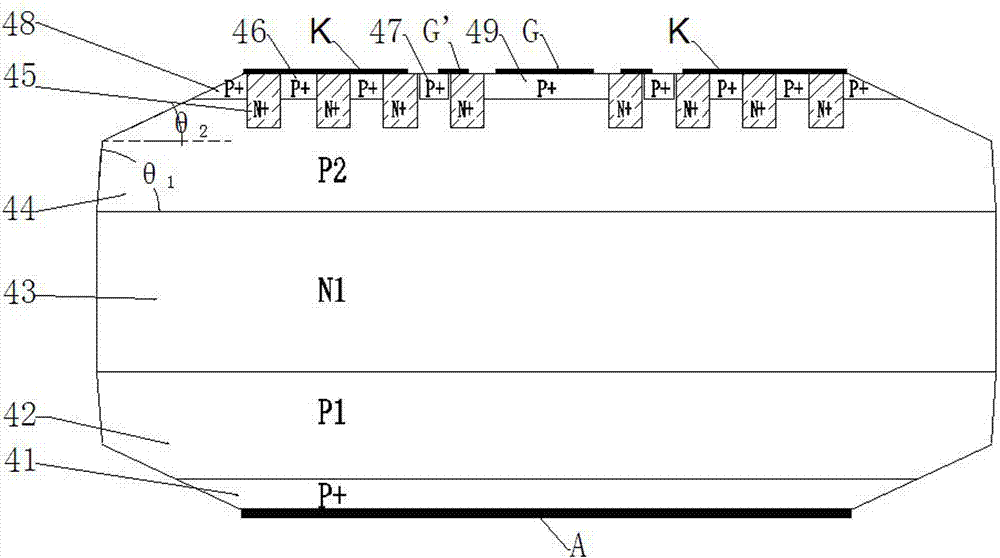

[0046] Example 1 as figure 1 , figure 2 , Figure 9 As shown, it is a high-voltage fast turn-on thyristor designed according to 5000V, and the chip size is 101.6mm. It is packaged by the lower sealing part 1 of the tube case, the lower gasket 3 , the semiconductor chip 4 , the upper gasket 5 , the gate assembly 6 and the upper sealing part 7 . A positioning column 2 is provided between the lower gasket 3 and the lower sealing part 1 of the tube case. The semiconductor chip 4 is a three-terminal PNPN four-layer structure, and the three terminals are respectively the anode A, the cathode K and the gate, and the gate includes the center gate G and the amplification gate G', and the PNPN four-layer structure is respectively the P1 anode region 42 , N1 long base region 43 , P2 short base region 44 and N+ cathode region 45 . An anode P+ layer 41 is added on the surface of the anode area of the chip P1, and a cathode P+ layer is provided on the cathode surface of the central g...

Embodiment 2

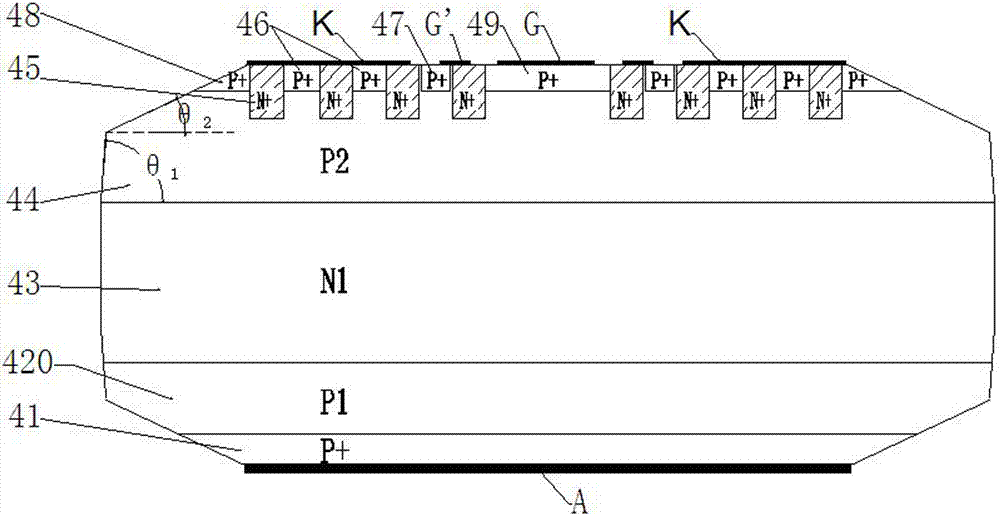

[0053] Example 2 as figure 1 , image 3 , Image 6 , Figure 9 As shown, the difference with embodiment 1 is that the chip adopts such as Image 6 process, the junction depth of the P1 anode region is 30∽110 μm, and the P1 anode region 420 is 30∽50 μm shallower than the P2 short base region 44 . This design reduces the thickness of the silicon wafer, which further reduces the voltage drop of the device. This product is suitable for fast turn-on devices with low reverse blocking voltage or no reverse blocking voltage.

Embodiment 3

[0054] Example 3 as Figure 4 As shown, the difference from Embodiment 1 and Embodiment 2 is that the mesa of the semiconductor chip is in the shape of a double positive angle mesa. The size of the positive angle θ11 is: 20º≤θ11≤80º. The product of this embodiment has the smallest cathode area loss, and is suitable for fast turn-on devices with the same diameter and larger current.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More