Schottky diode die and preparation method thereof, diode and photovoltaic module

A Schottky diode and Schottky potential technology, applied in the manufacturing of electrical components, semiconductor devices, semiconductor/solid-state devices, etc., can solve the problem of increased die and device thickness, poor conductivity of backfill polysilicon, and increased device series resistance, etc. question

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

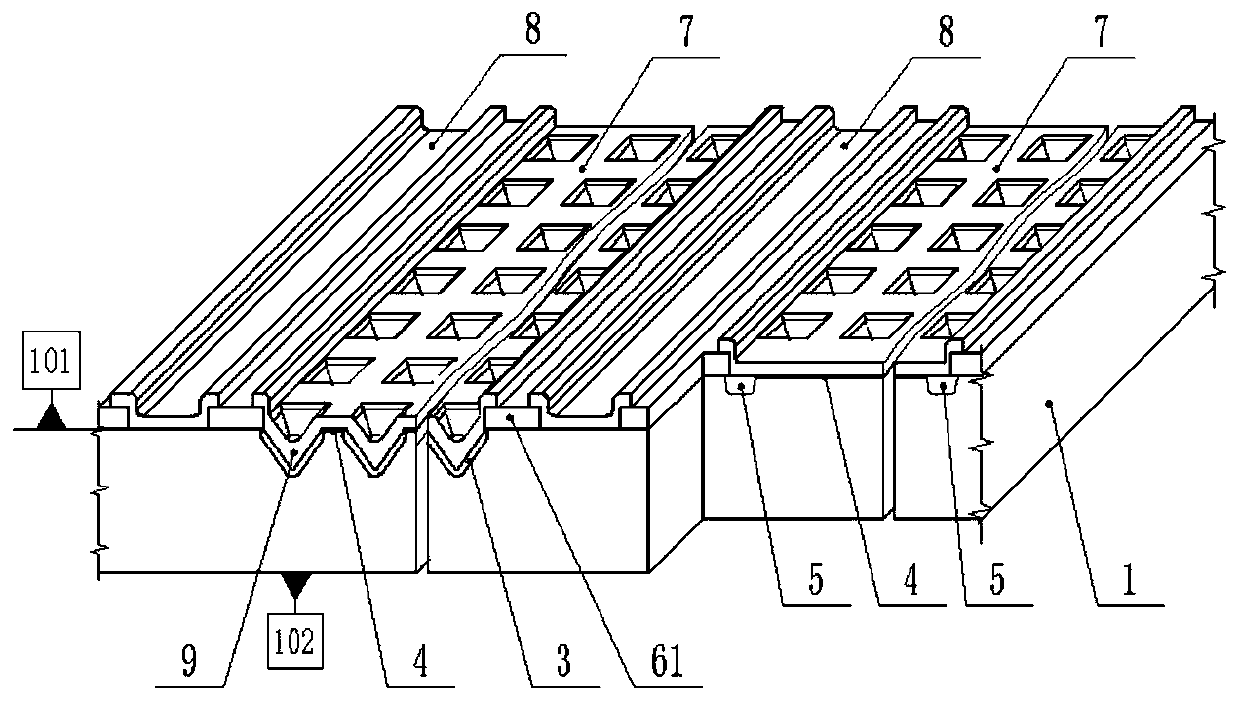

[0090] Please refer to figure 1 , is a schematic structural diagram of a Schottky diode die provided in the present disclosure. The Schottky diode die includes a single crystal silicon substrate 1, a Schottky barrier junction 4, a control PN junction 3, a protection PN junction 5, an isolation medium 61, a die positive electrode contact metal 7 and a die negative electrode In contact with the metal 8, a plurality of etch pits 9 are arranged on the first side 101 of the single crystal silicon substrate 1, and the plurality of etch pits 9 are regularly arranged on the first side 101 of the single crystal silicon substrate 1, and the control PN junction 3 is arranged on On the pit wall of the etching pit 9, the Schottky barrier junction 4 is arranged on the plane adjacent to the control PN junction 3 on the first side 101 of the single crystal silicon substrate 1, and the protection PN junction 5 is arranged on the Schottky barrier junction 4 The edge that is not adjacent to the...

Embodiment 2

[0111] Please refer to figure 1 , Figure 4 , Figure 5 to Figure 16 , Figure 4 A flow chart of the Schottky diode die manufacturing method provided by the present disclosure, Figure 5 to Figure 16 is a schematic diagram of each process step.

[0112] Step 101, using N-type (100) single crystal silicon substrate 1, such as Figure 5 ;

[0113] In step 102, an isolation dielectric process layer 6 is prepared on the first side 101 and the second side 102 of the single crystal silicon substrate 1 to obtain the following Image 6 The first middleware shown;

[0114] Step 103, on the isolation dielectric process layer 6, prepare the etching pit 9 / control the doping process window 31 of the PN junction 3, and obtain the following Figure 7 The second middleware shown in;

[0115] Step 104, through the etching pit 9 / controlling the doping process window 31 of the PN junction 3, using an alkaline anisotropic etching solution to prepare the etching pit 9 to obtain the followi...

Embodiment 3

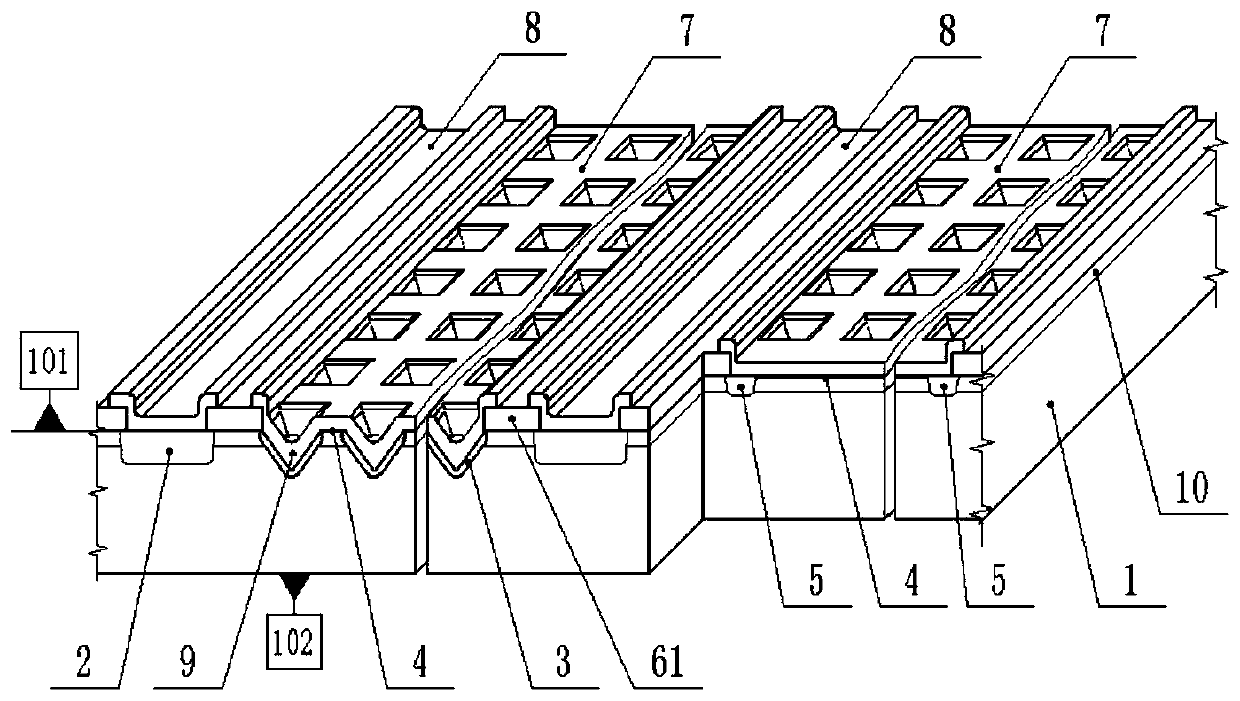

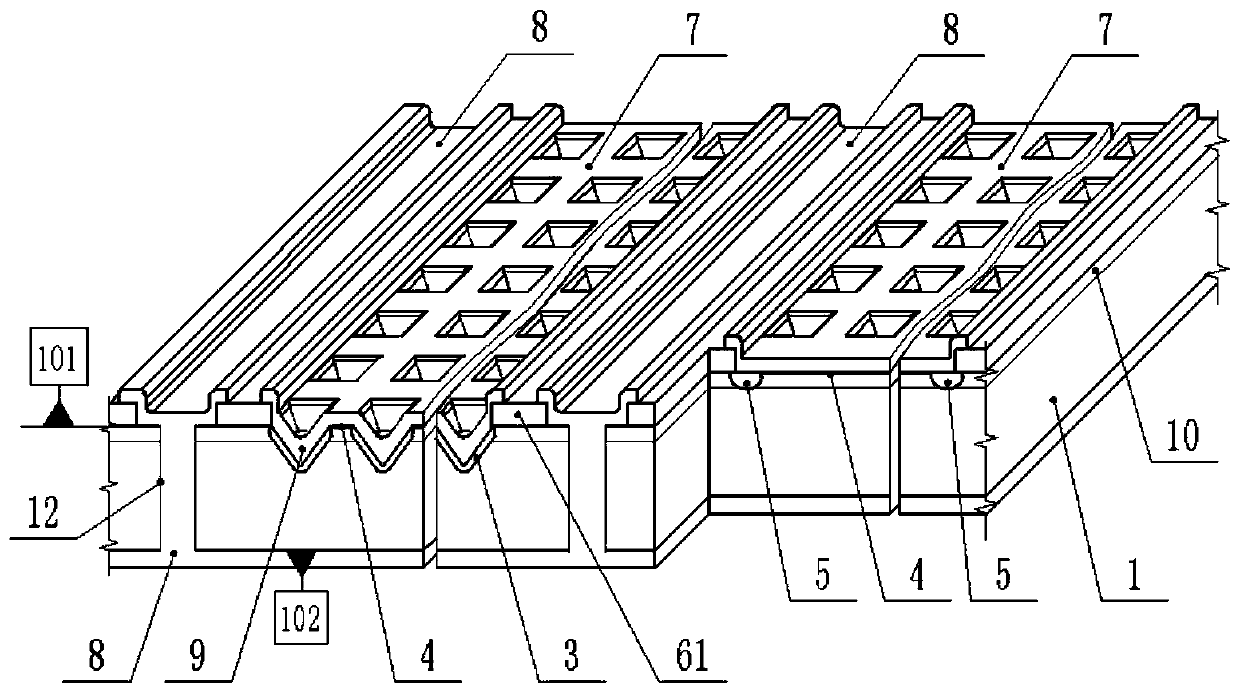

[0125] Please refer to figure 2 , Figure 17 , Figure 18 .

[0126] The difference between this embodiment and embodiment 2 is:

[0127] refer to Figure 17 , using N-type (100) silicon epitaxial wafers as monocrystalline silicon substrate 1, epitaxial layer 10 is N - Silicon, thickness 2μ~20μ;

[0128] In order to realize the ohmic contact between the die negative electrode contact metal 8 and the single crystal silicon substrate 1, before depositing the contact metal 13 in the process window 36 of the die negative electrode contact metal 8, it is necessary to pass through N + Silicon doping prepares heavily doped region 2 of the substrate. The process for preparing the heavily doped region 2 of the substrate is a conventional process in the prior art, so details are not repeated here.

[0129] In this embodiment, the Schottky barrier junction 4 is arranged in the epitaxial layer 10, the substrate heavily doped region 2 penetrates the epitaxial layer 10, and the etch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More