OLED display device array substrate and preparation method thereof

A technology for array substrates and display devices, which is applied in the manufacture of semiconductor/solid-state devices, semiconductor devices, and electric solid-state devices, etc., can solve the problems of complex preparation methods of array substrates for OLED display devices, and compensate for spatial inhomogeneity and instability. , the effect of high mobility and few preparation steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

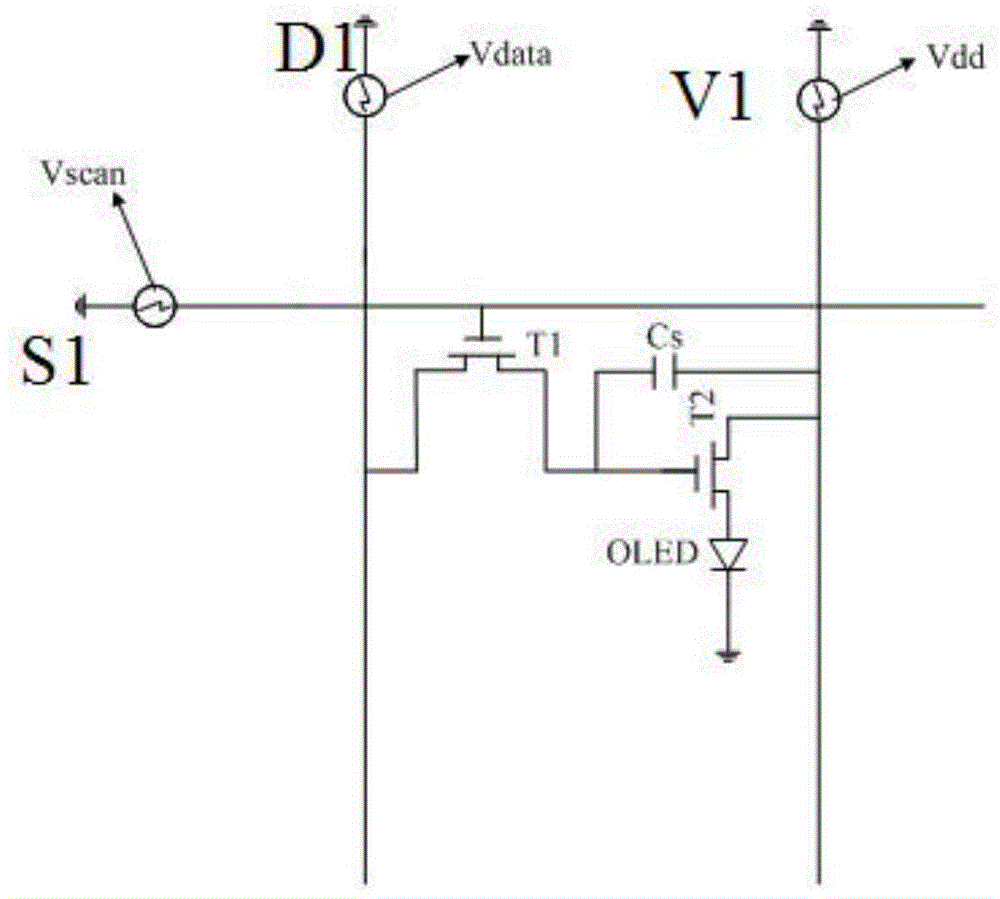

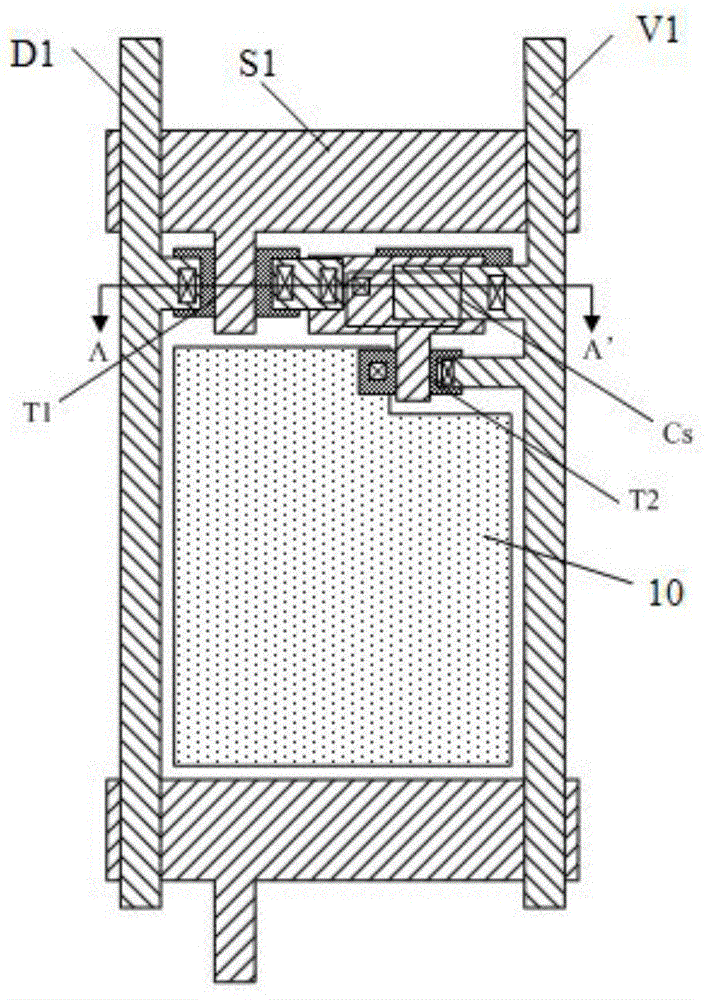

[0049] This embodiment provides a method for preparing an array substrate of an OLED display device and an array substrate prepared by the method. The pixel structure in the basic array is as attached image 3 As shown, the pixel structure includes: a scan line S1 , a data line D1 , a power line V1 , a storage capacitor Cs, a switch TFT T1 , a control TFT T2 and a pixel area 10 .

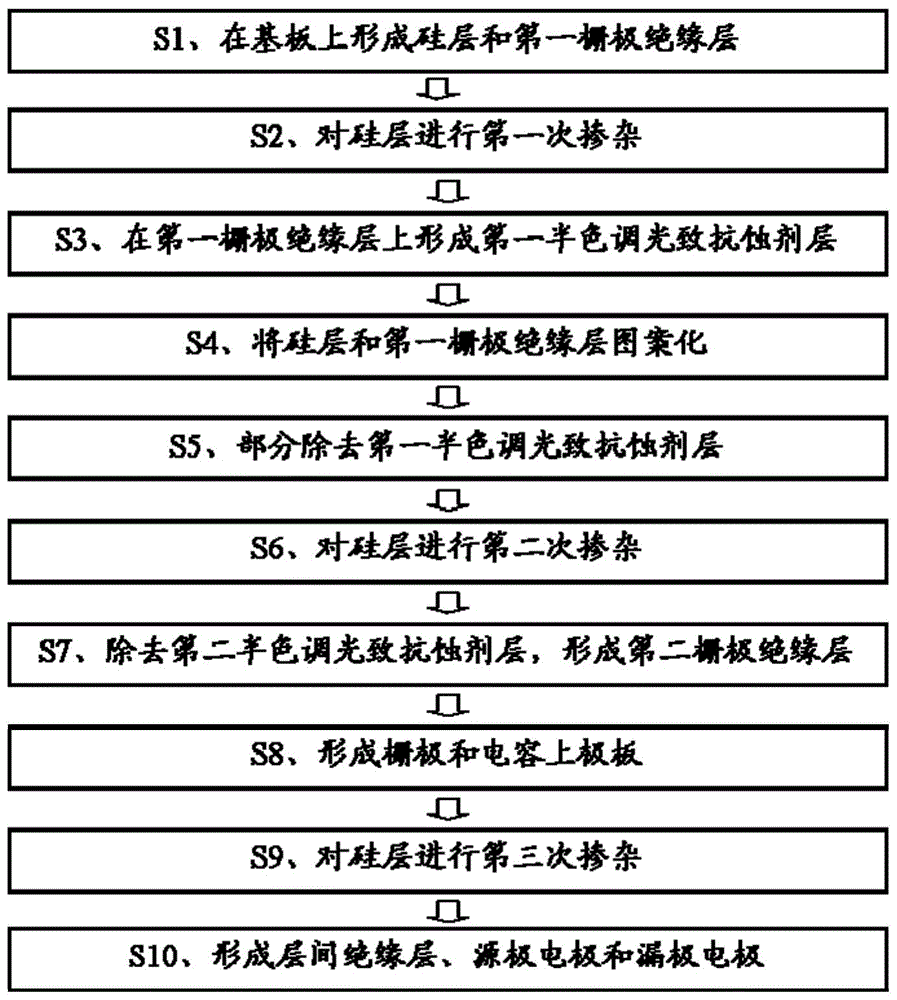

[0050] A flow chart of a method for preparing an OLED display device array substrate provided in this embodiment is shown in the attached figure 2 As shown, the cross-sectional view corresponding to the preparation of the array substrate of the OLED display device is as follows Figure 4 to Figure 12 shown.

[0051] A method for preparing an OLED display device array substrate provided in this embodiment includes the following steps:

[0052] S1, such as Figure 4 As shown, a buffer layer 2 , a semiconductor layer 3 and a first gate insulating layer 41 are sequentially formed on a substrate 1 i...

Embodiment 2

[0070] This embodiment provides a method for preparing an OLED display device array substrate and the array substrate prepared by this method. area 31 width (as Figure 13 shown). When viewed along the thickness direction of the substrate 1, the width L1 of the gate 61 is smaller than the width L2 of the first doped region 31. At this time, the semiconductor layer 3 is doped with P-type ions for the third time. 5×10 14 / cm 2 , to be less than the doping dose of the second doping process 5×10 15 / cm 2 ,, due to the self-alignment of the gate and the relationship that it acts as a mask, the semiconductor layer 3 in the capacitor region will not be doped, and the second doped region 32 in the transistor region is partially heavily doped, forming the third doped region The regions in 34 that have been doped three times at both ends are the source region and the drain region; the region adjacent to the source region and the drain region and that has been doped twice becomes th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More