Isolated LDMOS device and manufacturing method thereof

An isolation type and device technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of unfavorable industrial production control, increase the peripheral size of devices, and increase process costs, etc., so as to facilitate industrial production control, The effect of eliminating the existence of the interface and reducing the peripheral size of the device

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

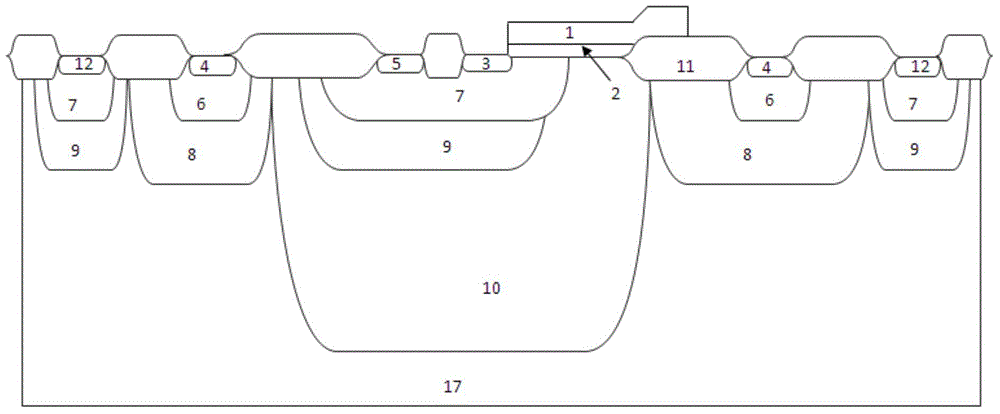

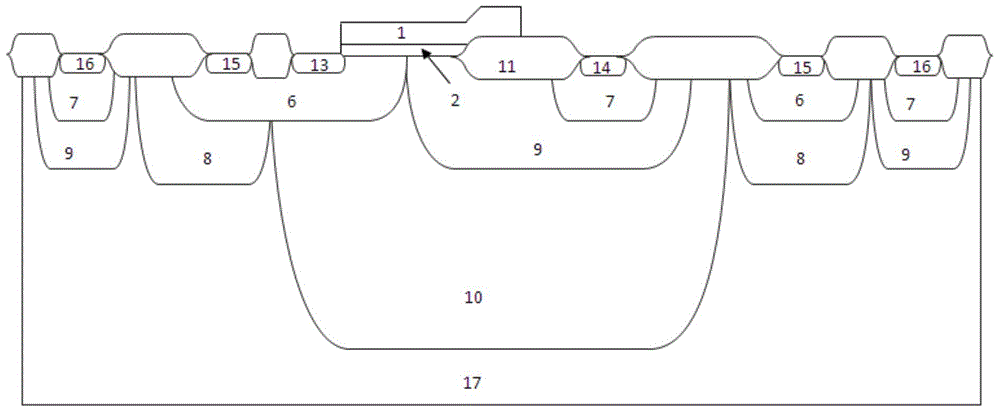

[0046] like Figure 4 Shown is the structural diagram of the isolated NLDMOS device of the embodiment of the present invention; as Figure 5 Shown is a structural diagram of an isolated PLDMOS device according to an embodiment of the present invention. The isolated LDMOS device in the embodiment of the present invention includes:

[0047] The deep N well 18 is formed in a P-type substrate such as a silicon substrate 17, and a plurality of field oxide layers 11 are formed on the surface of the P-type substrate 17, and the field oxide layers 11 are used to realize isolation between active regions, The field oxide layer 11 is shallow trench isolation field oxide (STI) or local field oxide (LOCOS).

[0048] The deep N well 18 is divided into an upper part and a lower part, the lower part is composed of a deep N well implanted region, the upper part is composed of a P-type implanted region superimposed on the deep N well implanted region, and the deep N well implanted region is c...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Horizontal size | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More