Forming method of silicon through hole

A through-silicon via, ring-shaped technology, used in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as large differences in thermal expansion coefficients, reduced reliability of through-silicon vias, and delamination of conductive layers and diffusion barrier layers. , to achieve the effect of improving reliability and reducing the possibility of delamination and cracking

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] Existing methods for forming TSVs generally include:

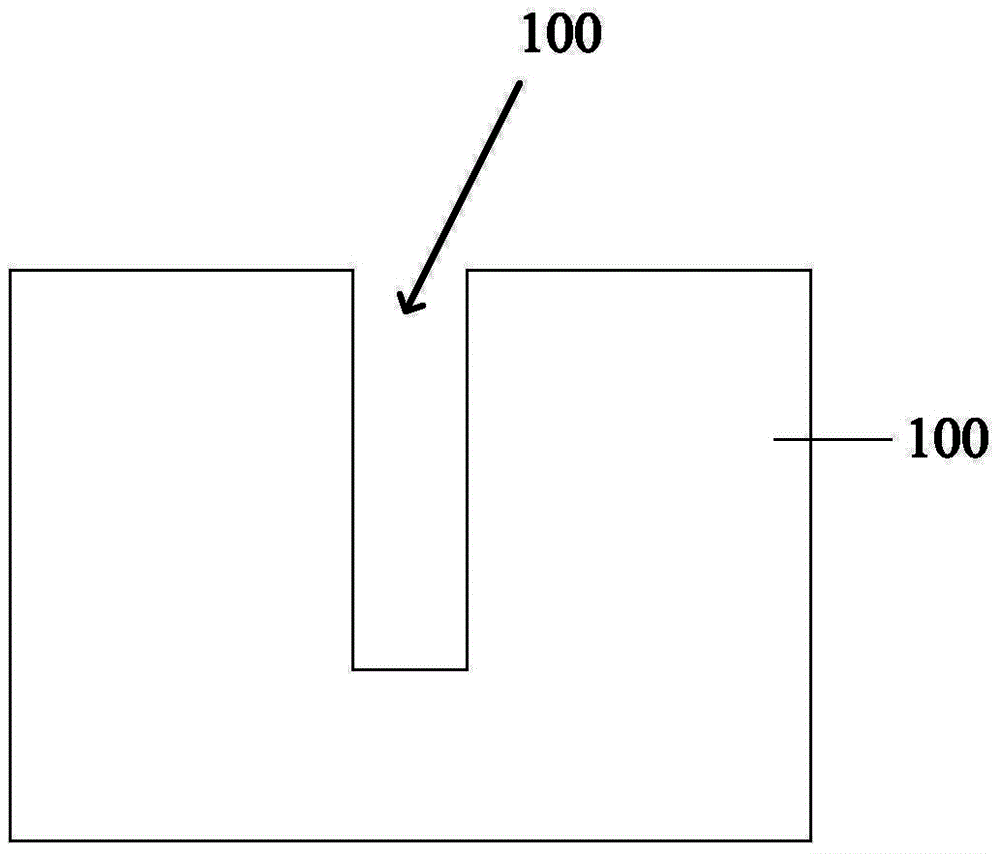

[0038] like figure 1 As shown, a semiconductor substrate 100 is provided, and a via hole 101 is formed on the semiconductor substrate 100;

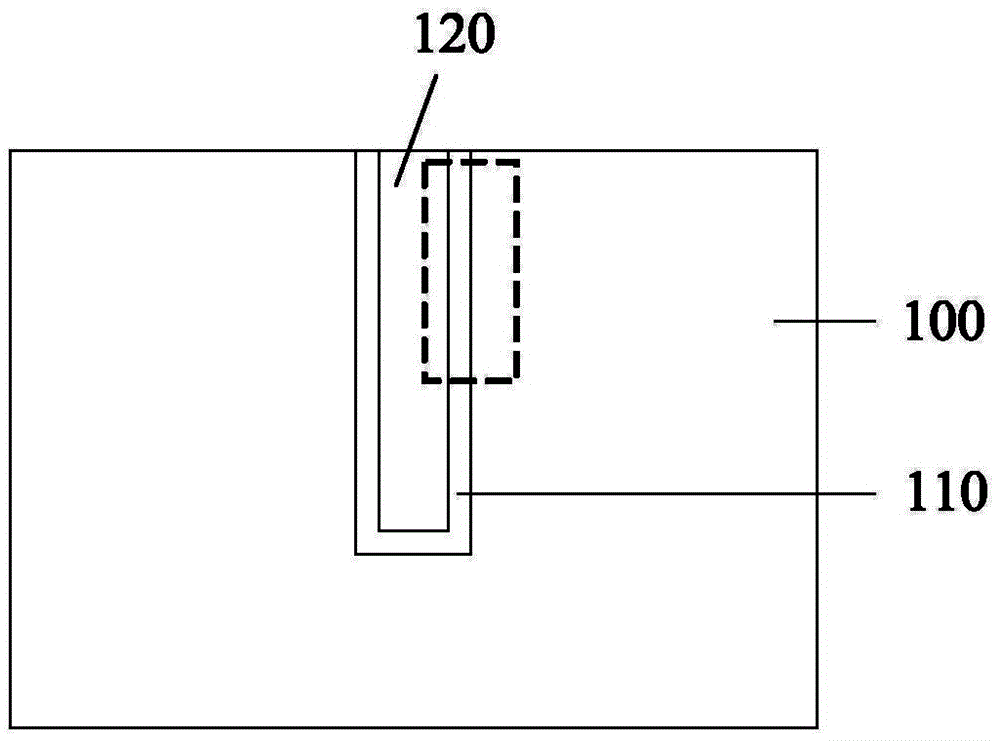

[0039] like figure 2 shown in figure 1 A diffusion barrier layer 110 is formed on the surface of the via hole 101 shown, and a metal layer 120 is continuously filled in the via hole 101. The material of the metal layer 120 may be copper, and then planarized to obtain a through silicon via.

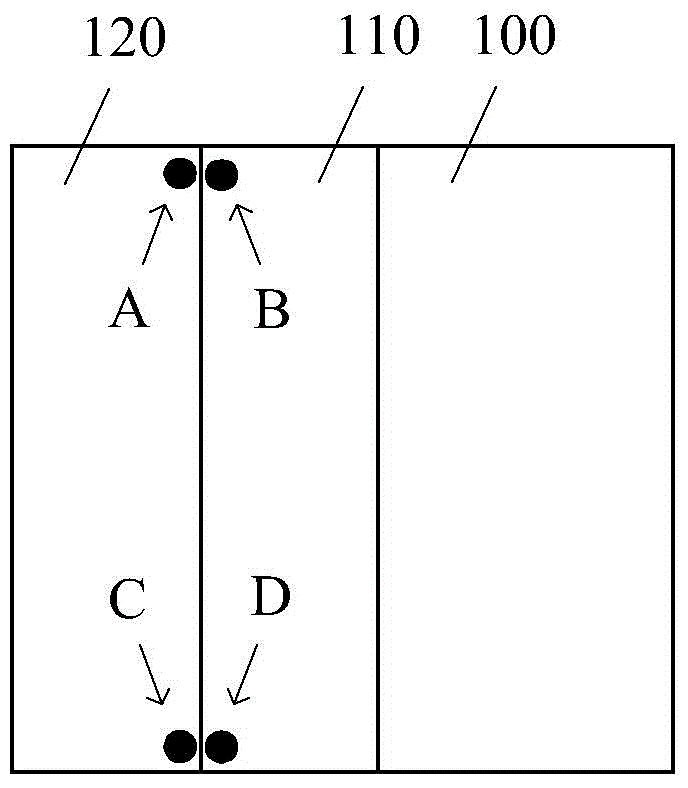

[0040] image 3 for figure 2 In the shown structure, it is an enlarged schematic view of the part surrounded by the dotted line box, and the part surrounded by the dotted line box includes a part of the metal layer 120 , a part of the diffusion barrier layer 110 and a part of the semiconductor substrate 100 arranged in sequence. exist image 3 Points A, B, C and D are selected from the shown TSVs. Point A and point B are located at the top of the TSV, and point A is located in th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More