Patents

Literature

222results about How to "Good for stress relief" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

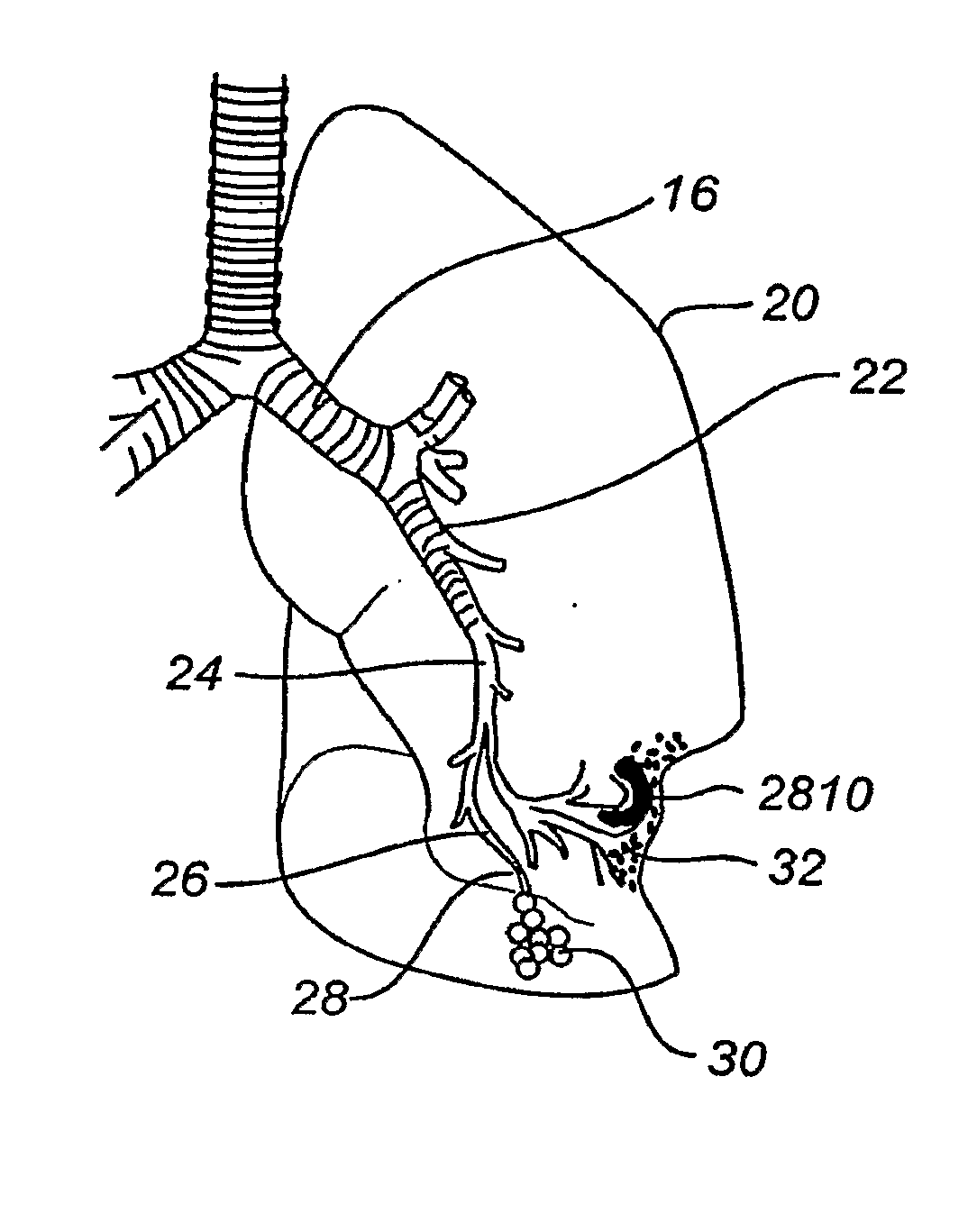

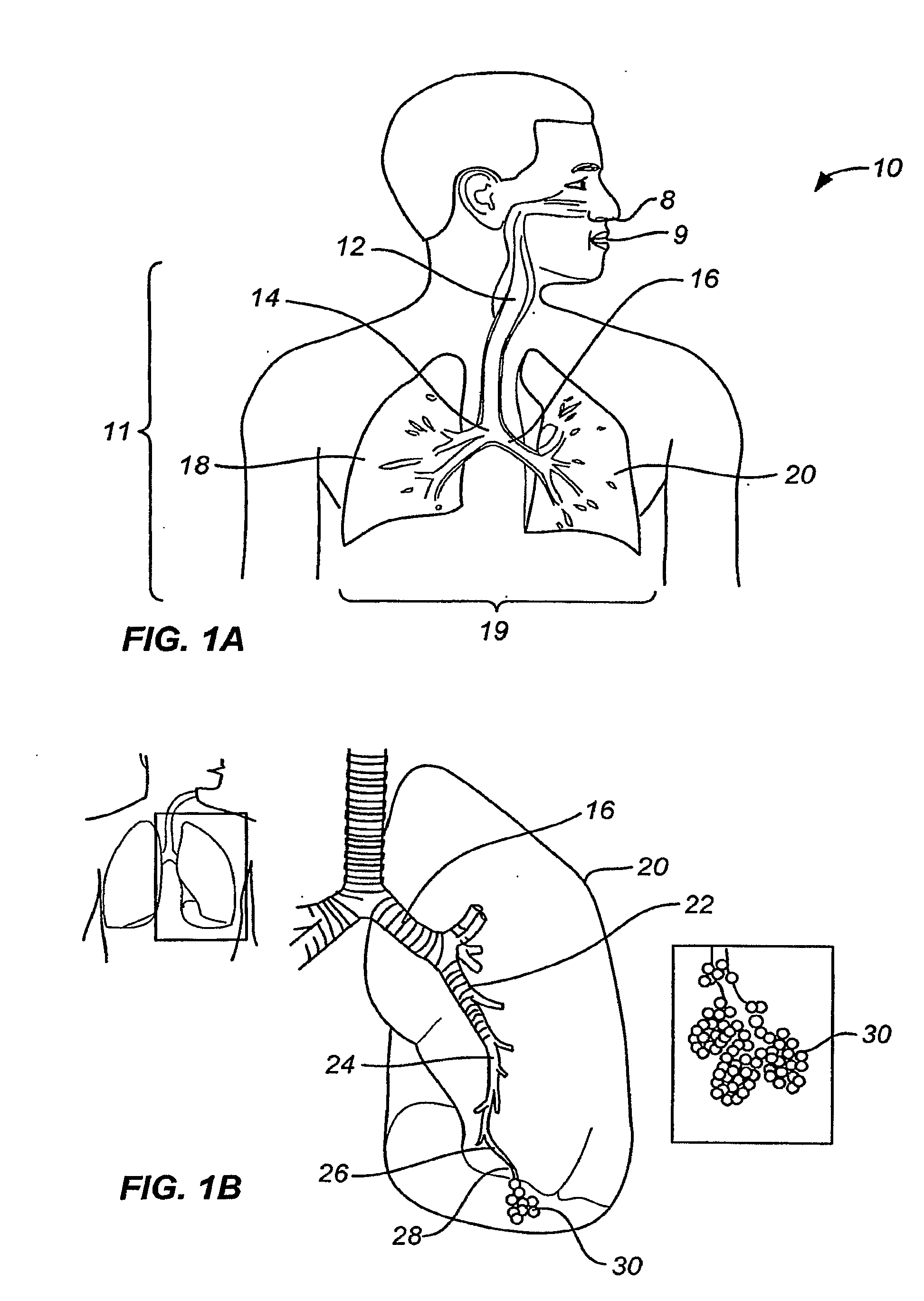

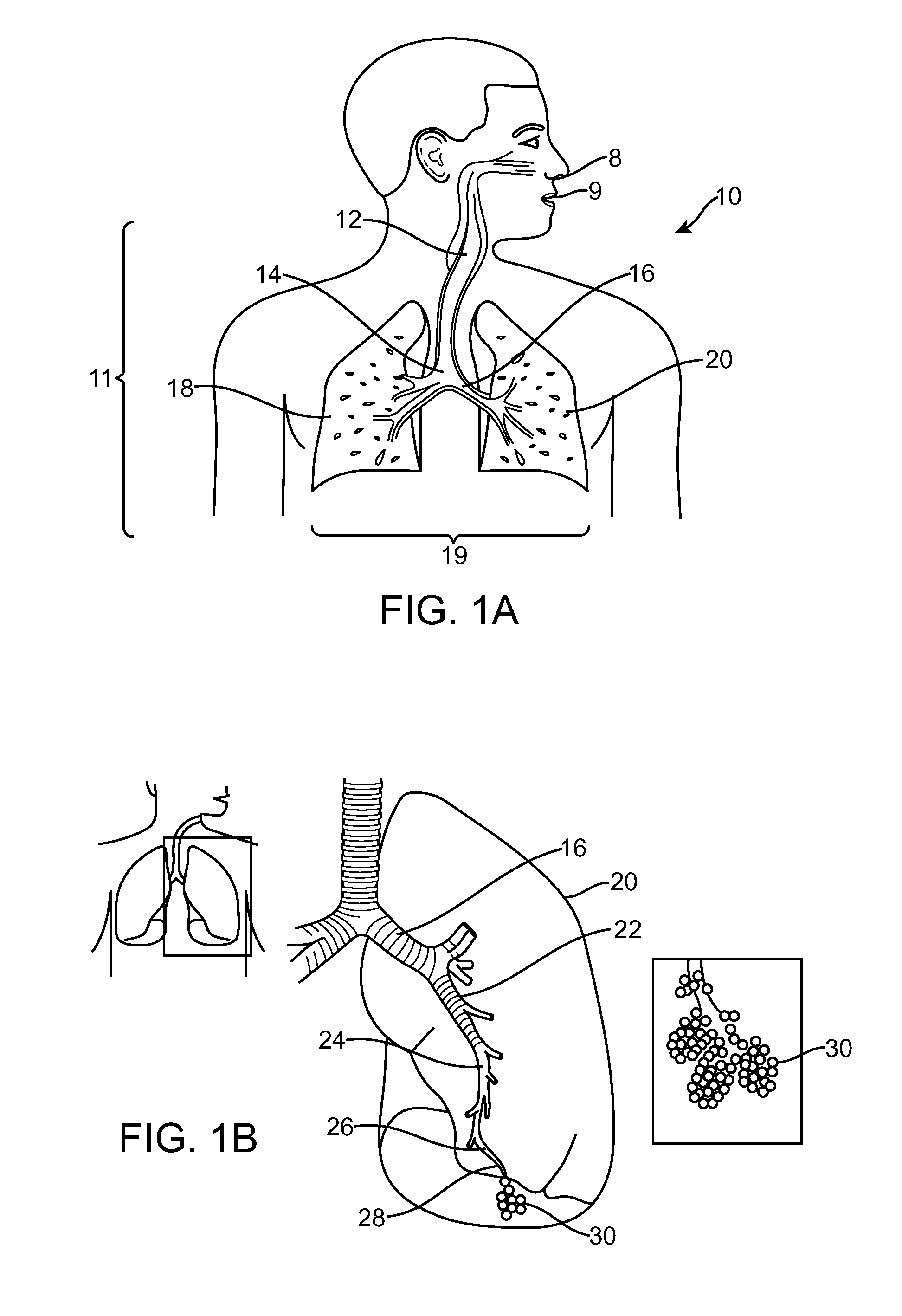

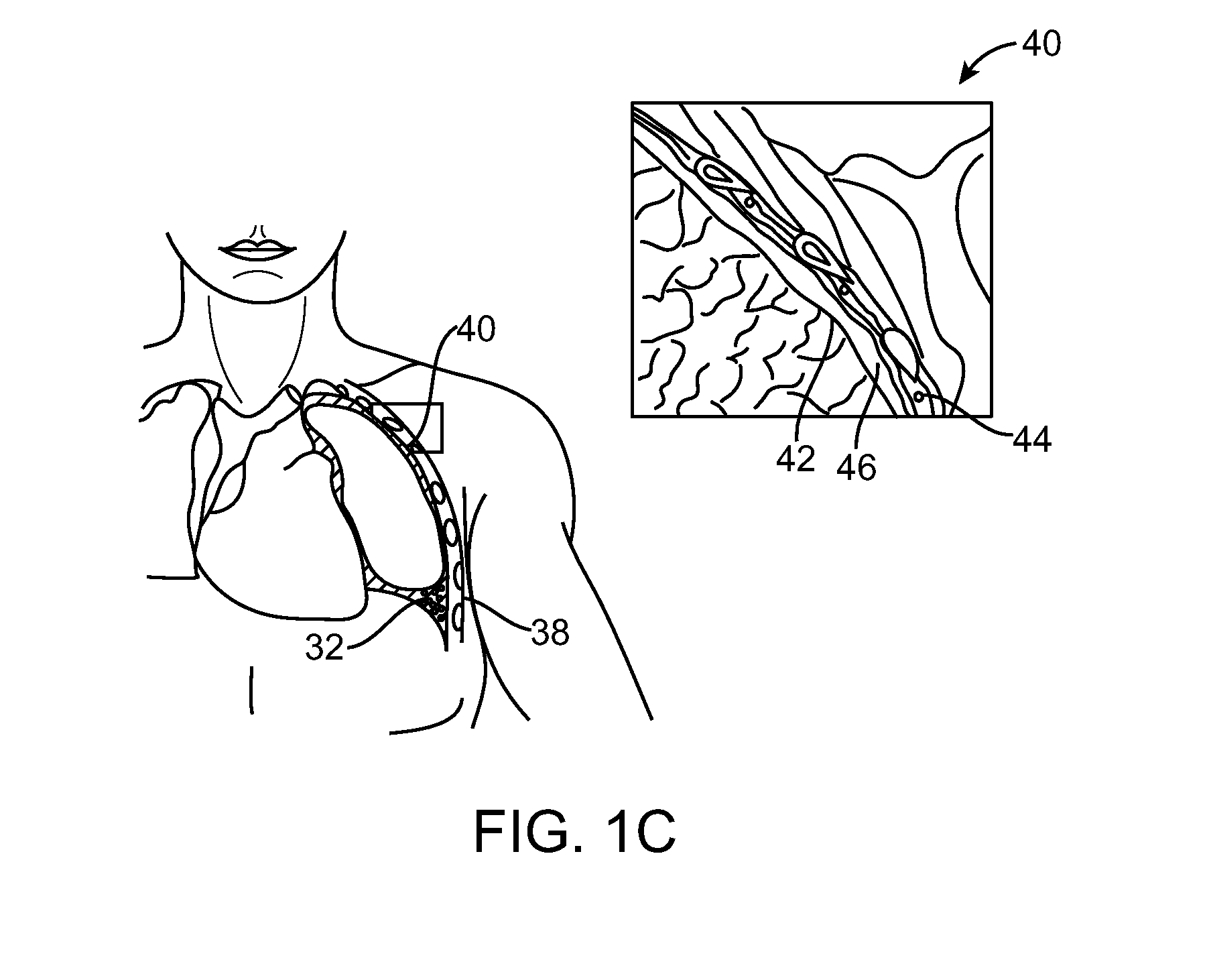

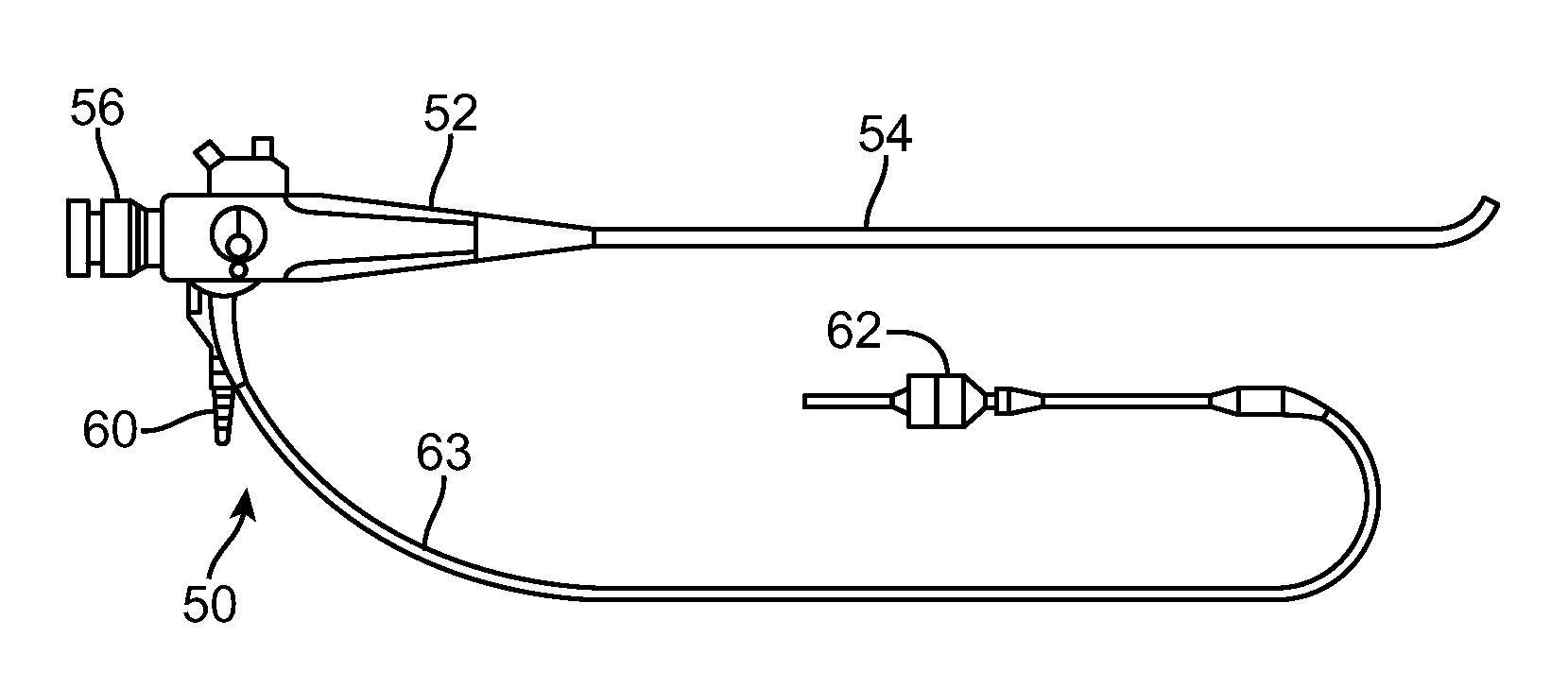

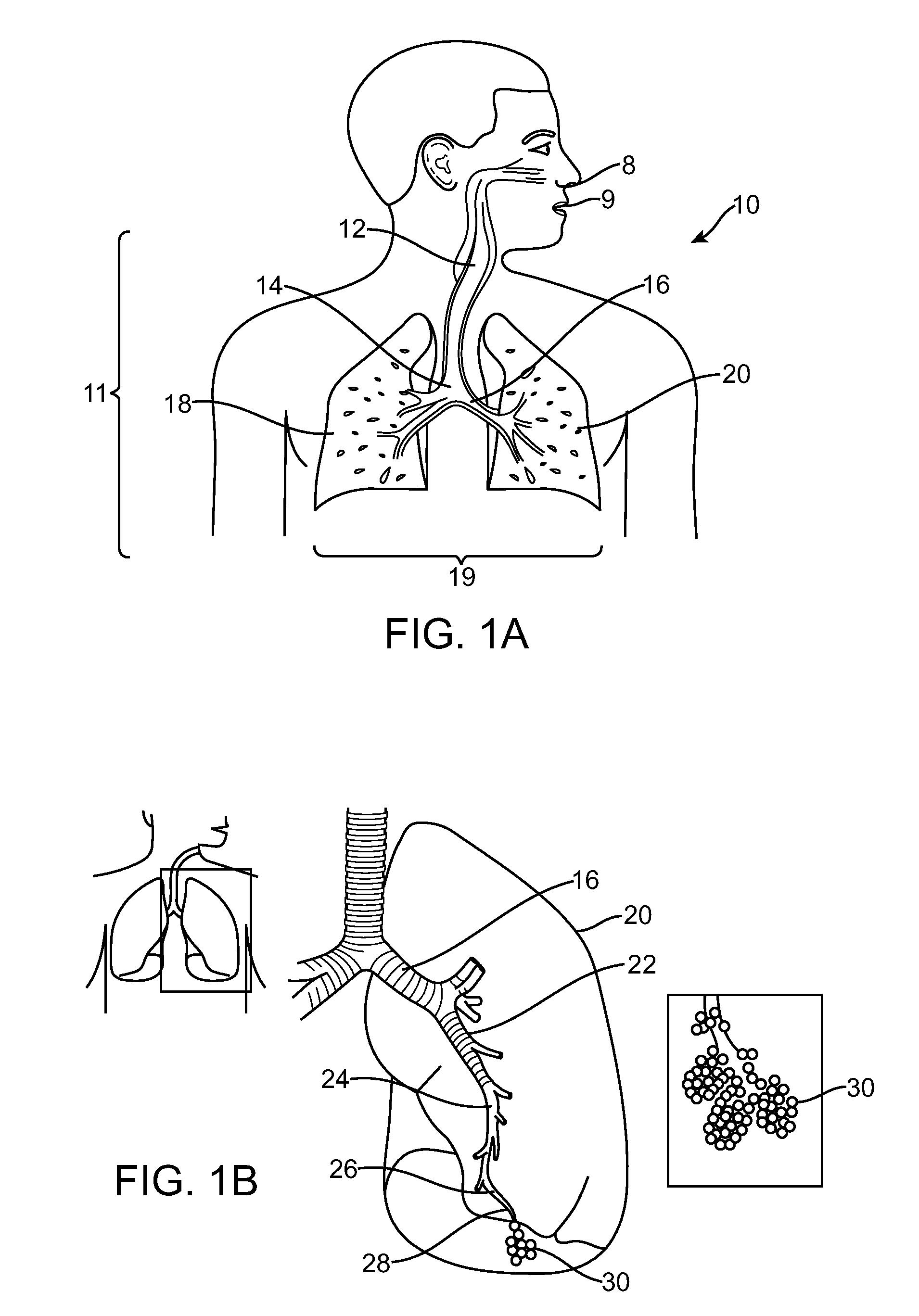

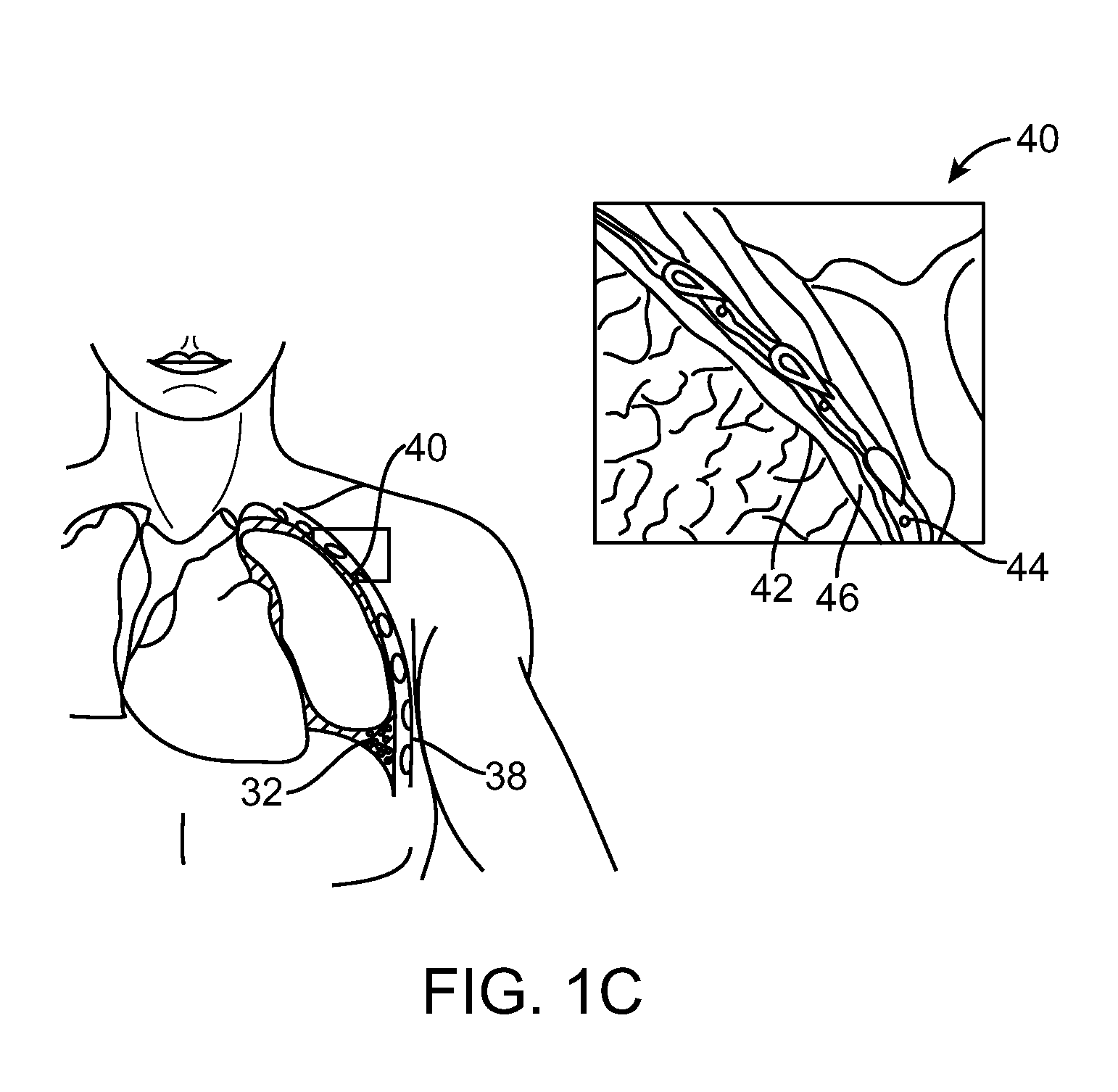

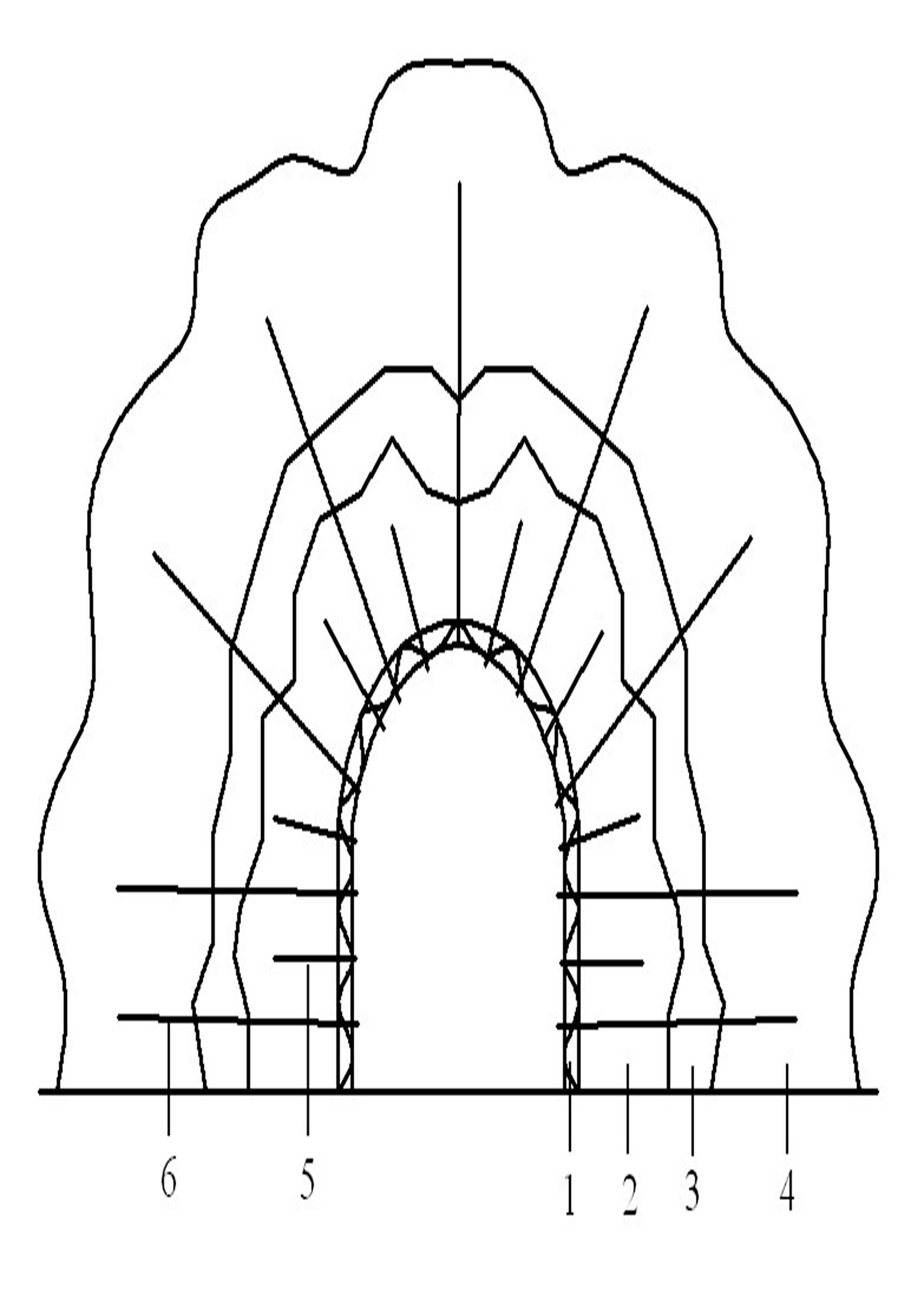

Minimally invasive lung volume reduction devices, methods, and systems

ActiveUS20090012626A1Good for stress reliefReduce the radius of curvatureBronchoscopesBronchiImplanted deviceIntensive care medicine

A lung volume reduction system is disclosed comprising an implantable device adapted to be delivered to a lung airway of a patient in a delivery configuration and to change to a deployed configuration to bend the lung airway. The invention also discloses a method of bending a lung airway of a patient comprising inserting a device into the airway in a delivery configuration and bending the device into a deployed configuration, thereby bending the airway.

Owner:EKOS CORP

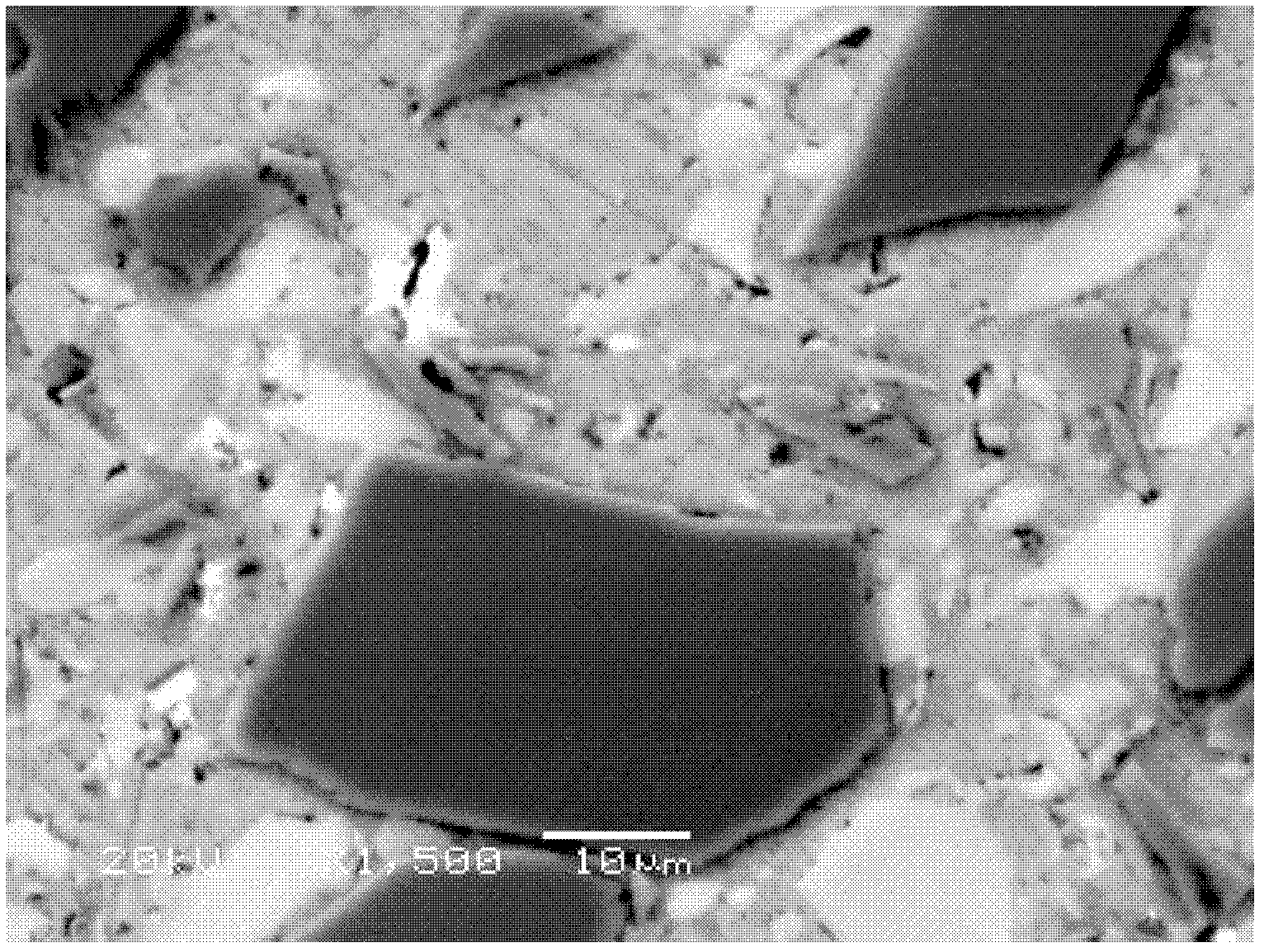

Process for preparing self-sealing silicon carbide ceramic based composite material

The invention relates to a method for manufacturing a self-healing silicon carbide ceramic matrix composite. The method comprises the following steps: preparing fiber preform; filtrating a pyrolytic carbon interface layer by chemical gas phase; carrying out thermal treatment on the interface layer; infiltrating silicon carbide and boron carbide substrate by chemical gas phase alternately; and depositing three silicon carbide coatings by the chemical gas phase. The method has strong designability, simple process and good repeatability. The ceramic matrix composite manufactured by the method has good high temperature resistance and oxidation resistance, has excellent mechanical performance and thermal performance, and can meet the use requirement of a sealing strip / an adjustment sheet, an interior cone and other components of a high thrust-weight ratio aeroengine.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

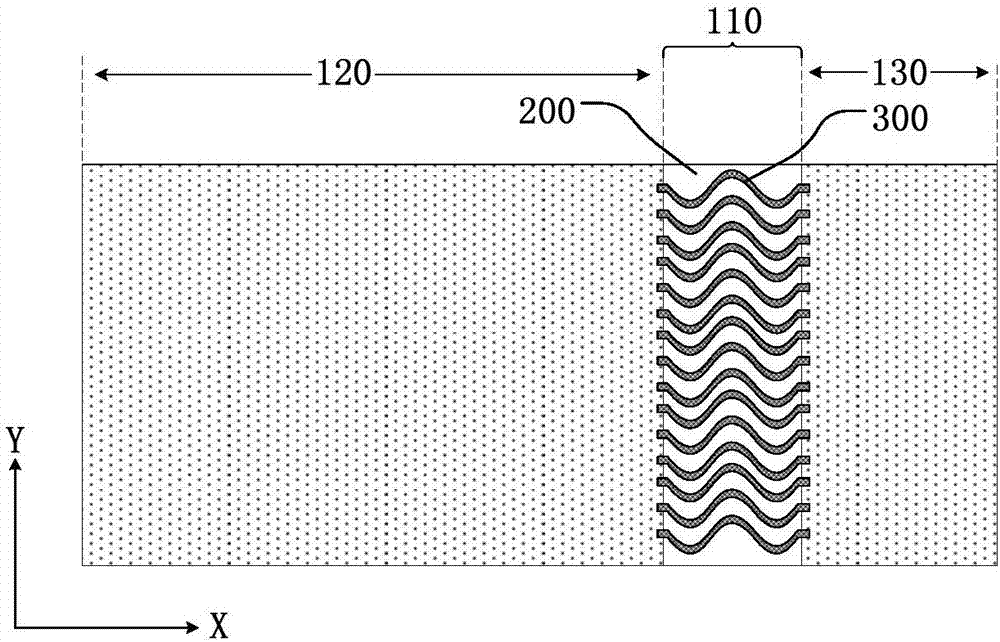

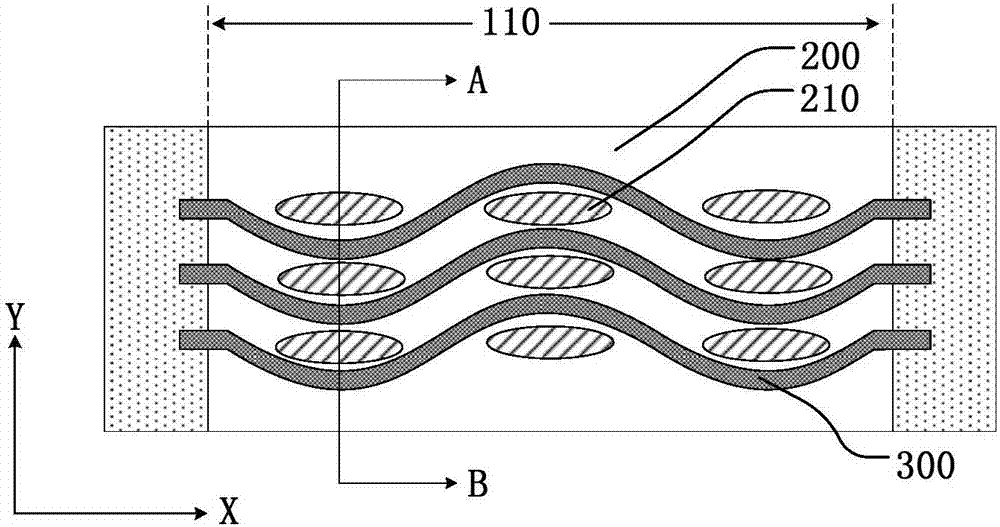

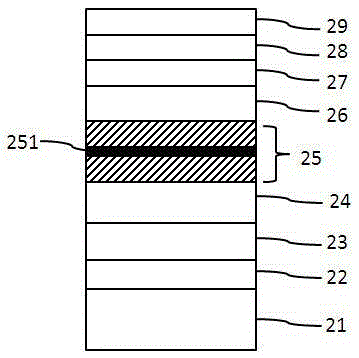

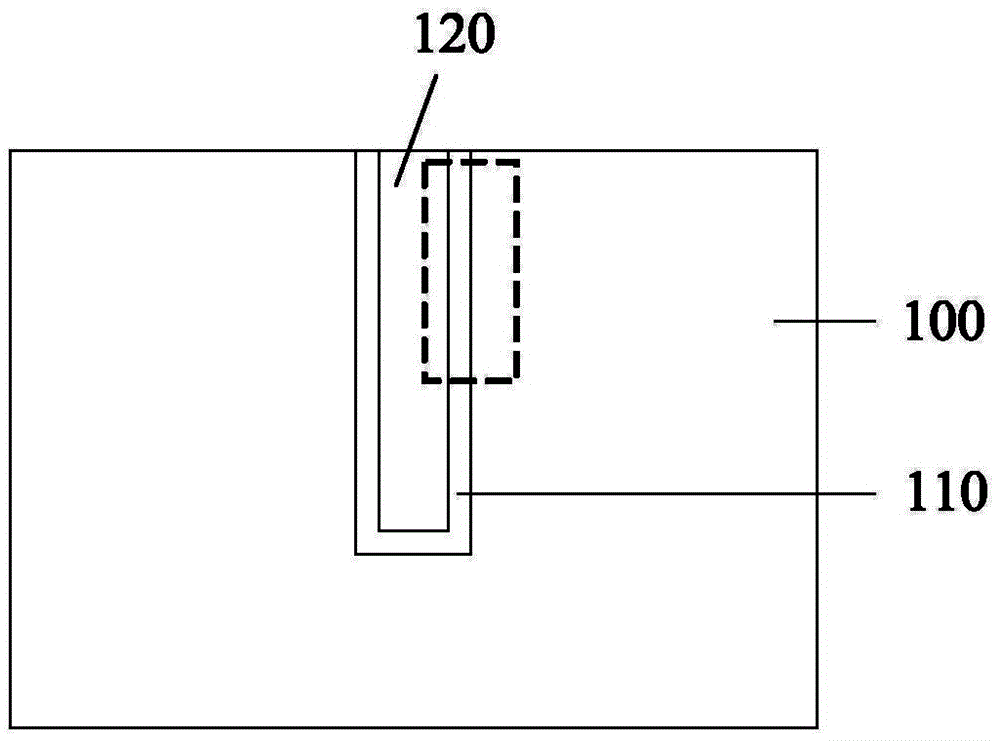

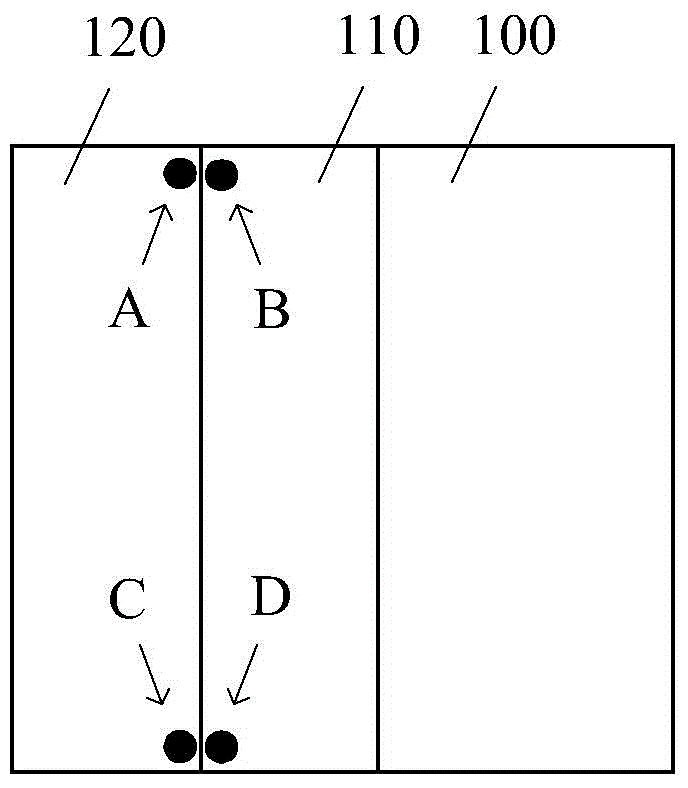

Baseplate and preparation method thereof, display panel and display device

ActiveCN107994036AImprove stress reliefAvoid breakingSolid-state devicesSemiconductor/solid-state device manufacturingSignal linesEngineering

Provided are a baseplate and a preparation method thereof, a display panel and a display device. The baseplate includes a substrate including a bendable region, an intermediate layer located on the substrate and in the bendable region, and at least one signal line located on one side of the intermediate layer far away from the intermediate layer, wherein an orthographic projection of the at leastone signal line on the substrate is located in an orthographic projection of the intermediate layer on the substrate, and at least part of the signal line is a curve, and at least one side of the partof the intermediate layer corresponding to the at least one signal line is provided with at least one groove. According to the technical scheme, through the groove located in the intermediate layer,the stress release capability of the intermediate layer is improved, and the signal line is prevented from breaking.

Owner:BOE TECH GRP CO LTD

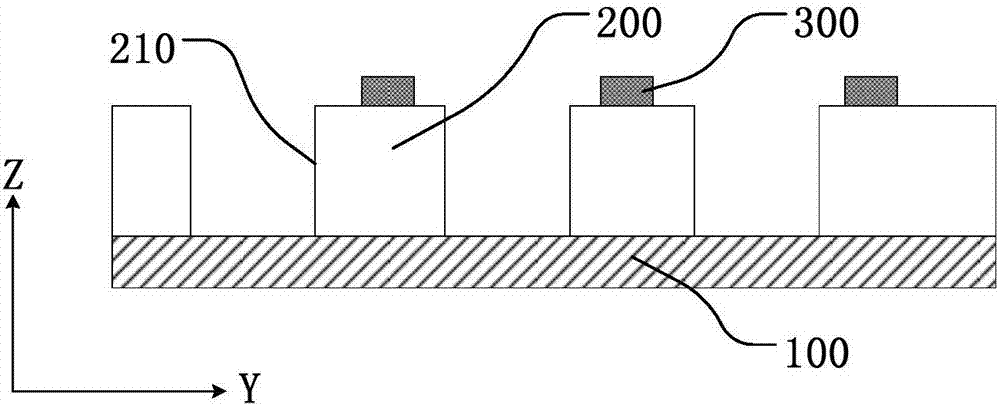

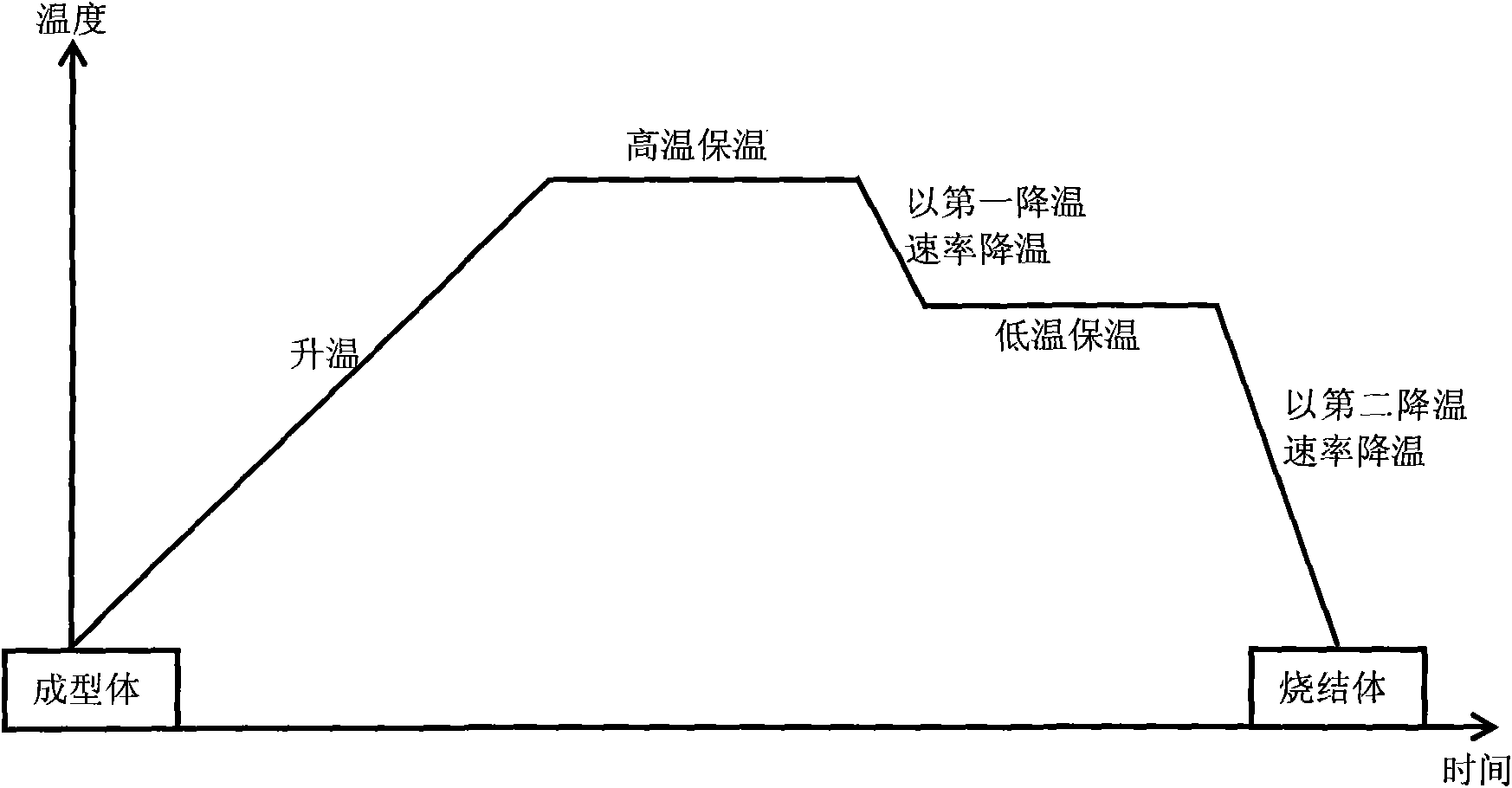

Recipe and preparation method of high-voltage gradient zinc oxide resistance card

The invention discloses a recipe and a preparation method of a high-voltage gradient zinc oxide resistance card. The recipe of the zinc oxide resistance card of the invention reasonably and preferably adopts the ingredients and the contents of the zinc oxide resistance card, the zinc oxide resistance card prepared by the recipe has the high-voltage gradient as high as 350 to 600v / mm, and at the same time, under the high-voltage gradient, the zinc oxide resistance card can maintain good nonlinear characteristic, electrical property and ageing-resistant characteristic to meet the miniaturization requirement of electronic components such as lightning protectors in practical application. In the preparation method of the zinc oxide resistance card of the invention, the accessory ingredients and trace ingredients in the zinc oxide resistance card have fine granularity, are matched, and are uniformly mixed, the impurity mixing quantity is reduced, at the same time, because the low-temperature heat-insulation process is added in the sintering process, the zinc oxide resistance card forms a stable crystal boundary structure which is favorable for improving the stability of the zinc oxide resistance card and the phase change of the bismuth oxide in the secondary heat treatment process, so the electrical property of the zinc oxide bismuth oxide can be improved.

Owner:NINGBO ZHENHAI GUOCHUANG HIGH VOLTAGE ELECTRIC APP

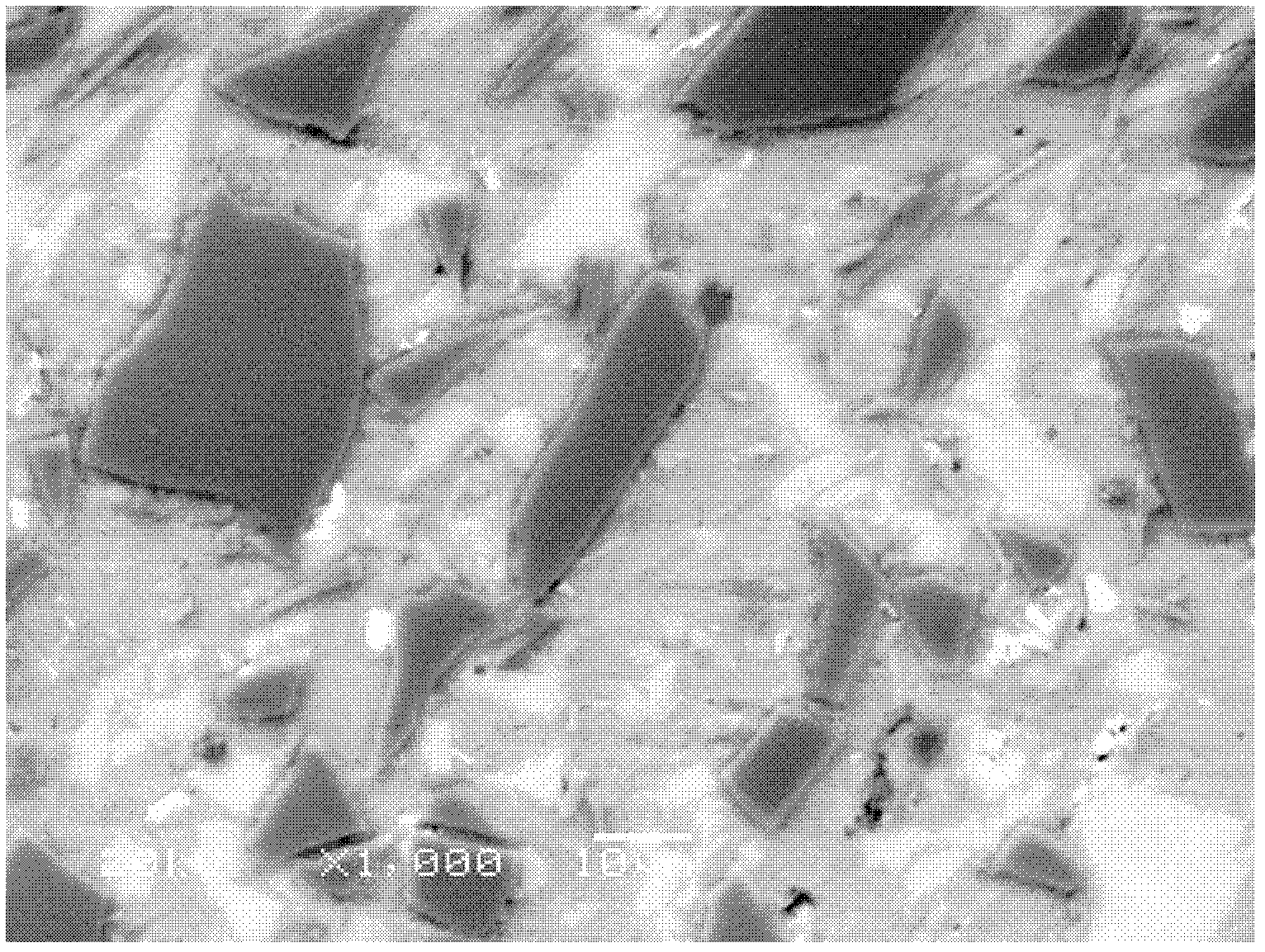

Silicon carbide reinforced aluminum-based composite material and preparation method thereof

The invention discloses a silicon carbide reinforced aluminum-based composite material and a preparation method thereof. The silicon carbide reinforced aluminum-based composite material is prepared from the following raw materials in percentage by volume: 20 to 25 percent of 325-mesh silicon carbide powder and the balance of 500-mesh Al-30Si alloy powder. According to the silicon carbide reinforced aluminum-based composite material, the silicon carbide powder and the Al-30Si alloy powder which have properly matched particle sizes are easily combined closely in the pressing and sintering process, defects such as air holes and cracks are avoided and the compactness of the composite material can be improved. In addition, by the preparation method of heating, pressurizing and keeping temperature stepwise according to set programs under the vacuum condition, slowly cooling together with a furnace to room temperature under the vacuum and high pressure conditions and removing the pressure, the metallurgical bonding of the reinforcement and the matrix is further improved, the defects such as air holes and cracks are avoided and the performance is high.

Owner:HENAN UNIV OF SCI & TECH

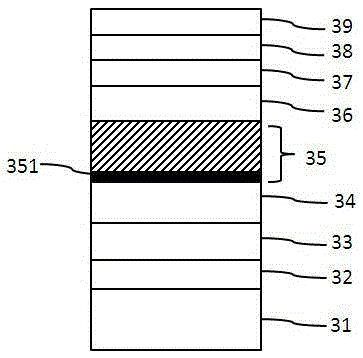

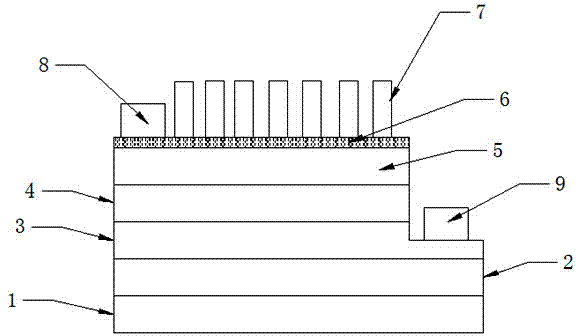

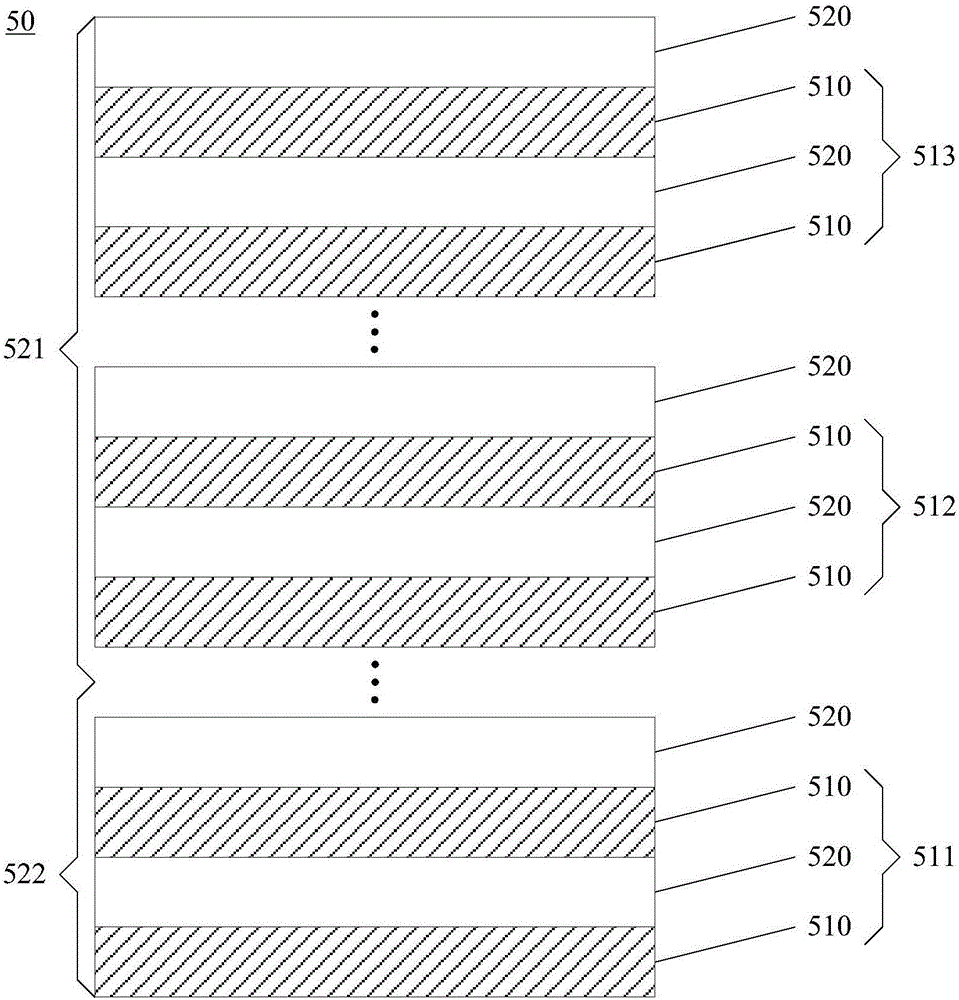

LED epitaxial structure and manufacturing method thereof

The invention provides an LED epitaxial structure and a manufacturing method thereof. The LED epitaxial structure comprises a substrate, a first conductive-type semiconductor layer, a stress release layer, a quantum well layer and a second conductive-type semiconductor layer sequentially from bottom to top. A low-temperature low-Al component AlxGa1-xN layer is inserted in the stress release layer, wherein x has a value range of 0.1% to 1%. Or the stress release layer is a superlattice layer formed by InGaN, GaN, and AlGaN. Thus, the stress release ability of the stress release layer is improved, voltage and Droop effects are improved, and the brightness is enhanced.

Owner:XIAMEN SANAN OPTOELECTRONICS TECH CO LTD

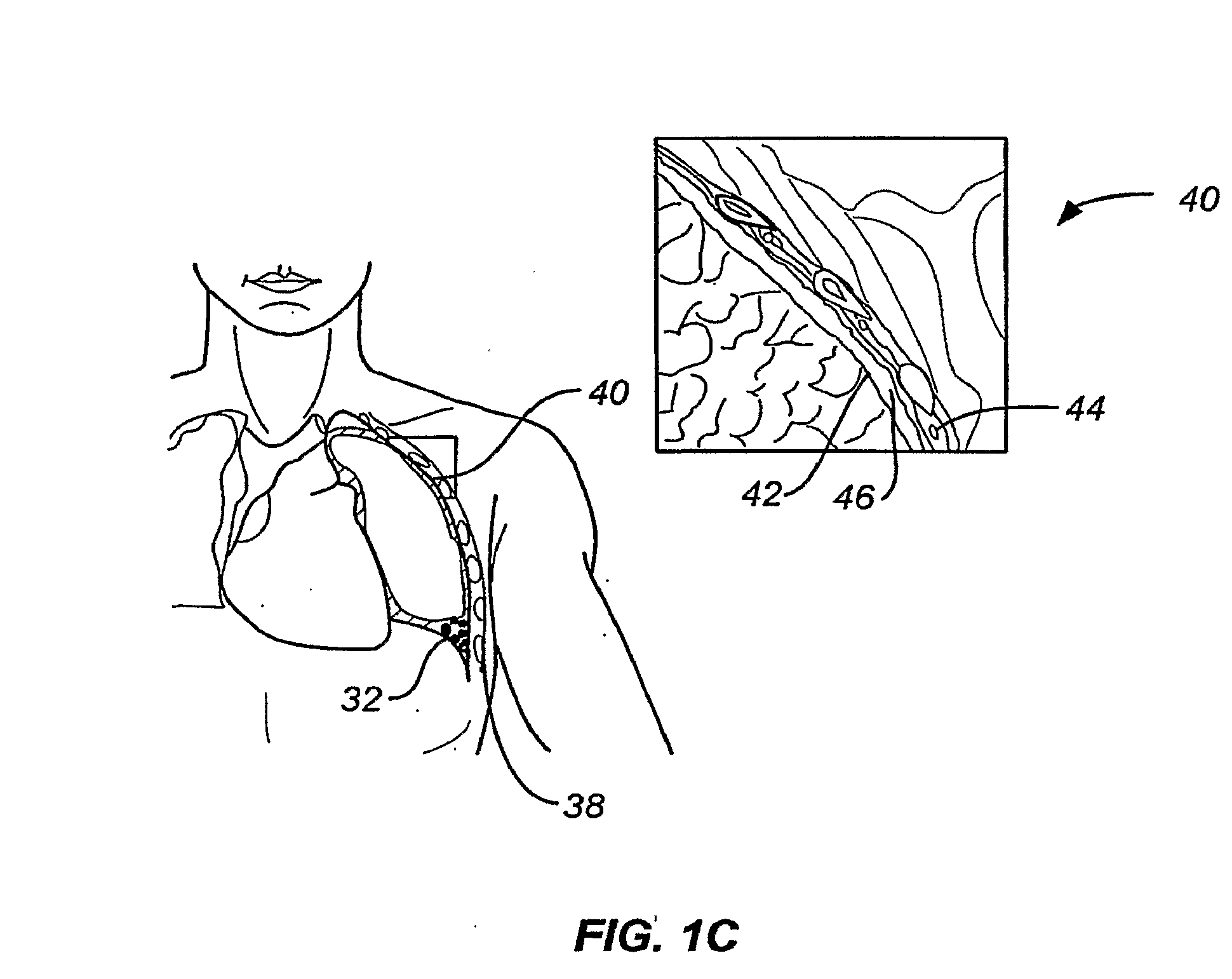

Lung Volume Reduction Devices, Methods, and Systems

InactiveUS20120172909A1Reduce radius of curvatureProvide strain reliefBronchoscopesTracheal tubesTherapeutic treatmentBiomedical engineering

The invention provides improved medical devices, therapeutic treatment systems, and treatment methods for treatment of the lung. A lung volume reduction system includes an implantable device having an elongate body that is sized and shaped for delivery via the airway system to a lung airway of a patient. The implant is inserted and positioned while the implant is in a delivery configuration, and is reconfigured to a deployed configuration so as to locally compress adjacent tissue of the lung, with portions of the elongate body generally moving laterally within the airway so as to laterally compress lung tissue. A plurality of such implants will often be used to treat a lung of a patient.

Owner:EKOS CORP

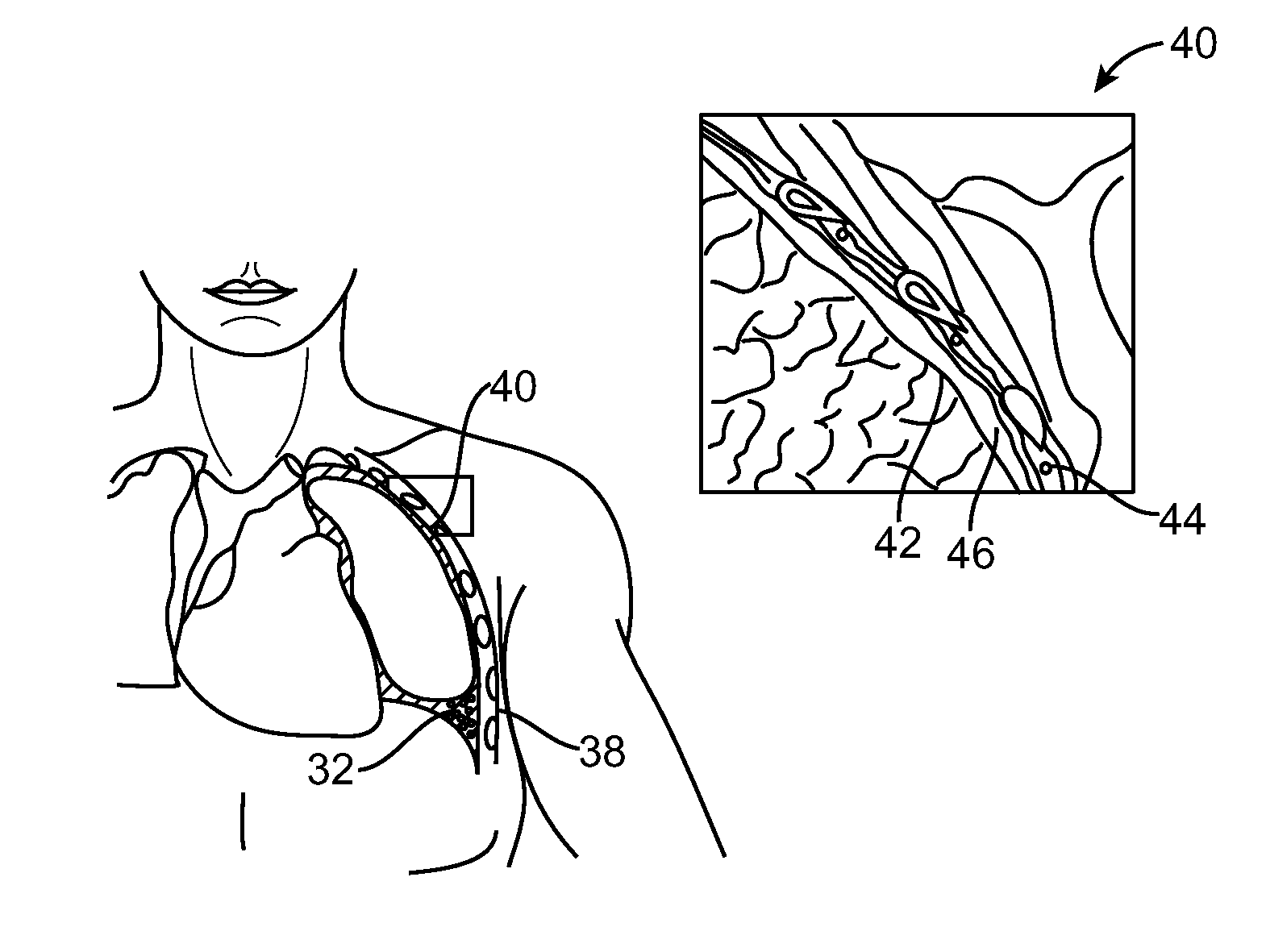

Lung Volume Reduction Devices, Methods, and Systems

InactiveUS20130096603A1Reduce tensionImprove lung functionTracheal tubesBronchoscopesTherapeutic treatmentLung tissue

The invention provides improved medical devices, therapeutic treatment systems, and treatment methods for treatment of the lung. A lung volume reduction system includes an implantable device having an elongate body that is sized and shaped for delivery via the airway system to a lung airway of a patient. The implant is inserted and positioned while the implant is in a delivery configuration, and is reconfigured to a deployed configuration so as to locally compress adjacent tissue of the lung, with portions of the elongate body generally moving laterally within the airway so as to laterally compress lung tissue. A plurality of such implants will often be used to treat a lung of a patient.

Owner:EKOS CORP

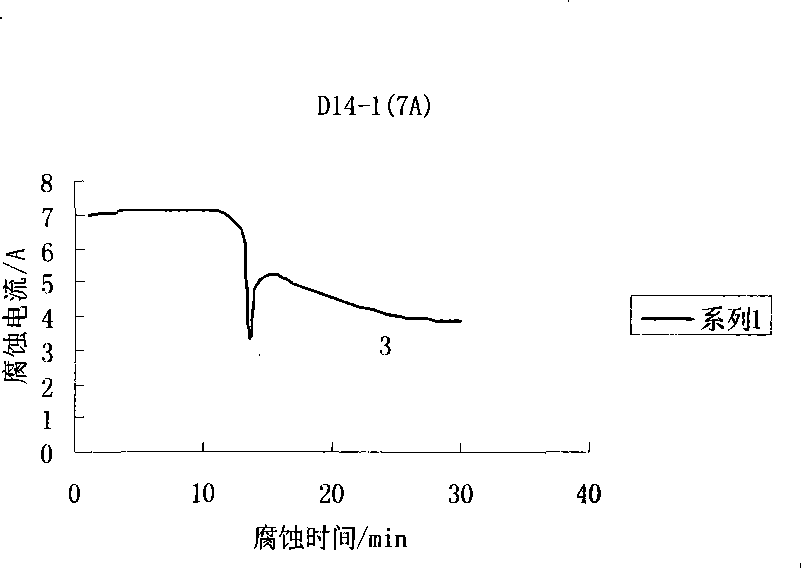

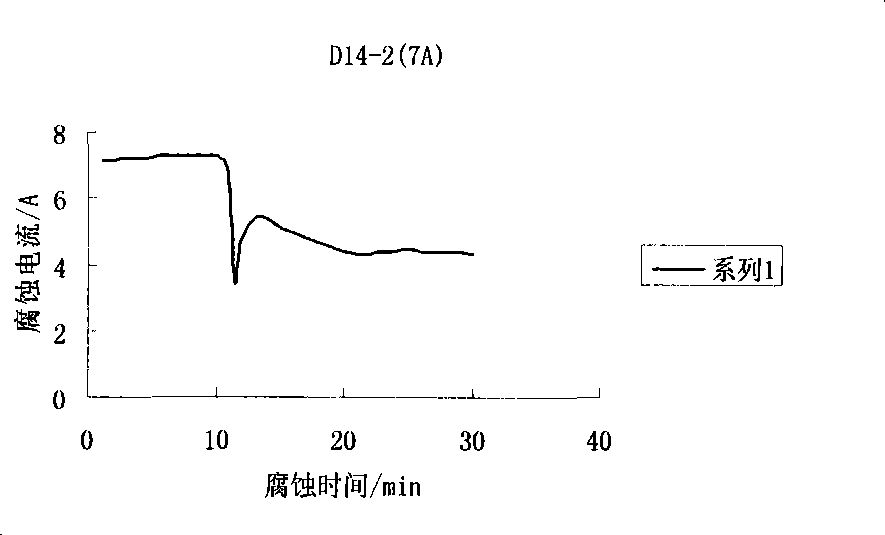

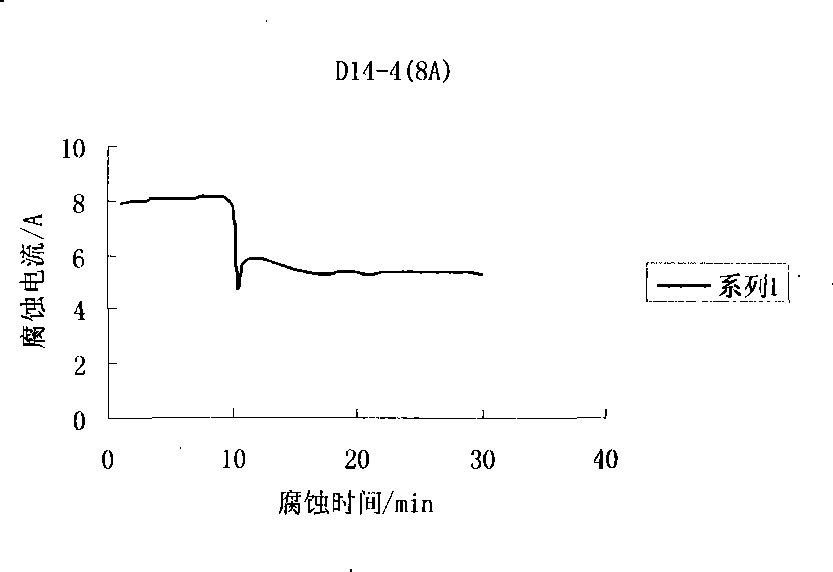

Method for detecting residual stress of steel by X-ray

InactiveCN101451965AVisually observe the internal stressEasy to measureMaterial analysis using radiation diffractionX-rayAqueous solution

The invention relates to a method of mensurating steel residual stress using X rays, comprising: (1) taking a galvanized sheet, polishing smooth surface layers; taking saturated NaCl aqueous solution as electrolyte, using measured components as anode corrosion ends, using galvanized sheet iron as a cathode, eroding by DC constant pressure, corrosion current being 7-8 A; (2) after corrosion cleavage, mensurating residual stress on vertical direction of welding using X rays, then correcting residual stress measurement value after cleavage using single side cleavage measurement stress value correction method, namely obtaining steel residual stress. According to the inventive method to measurate the steel residual stress, novel additional stress is not increased by electrolytic corrosion cleavage, also measurement result along heavy gauge workpieces is obtained, measurement result is simple, device cost is low.

Owner:CHONGQING UNIV

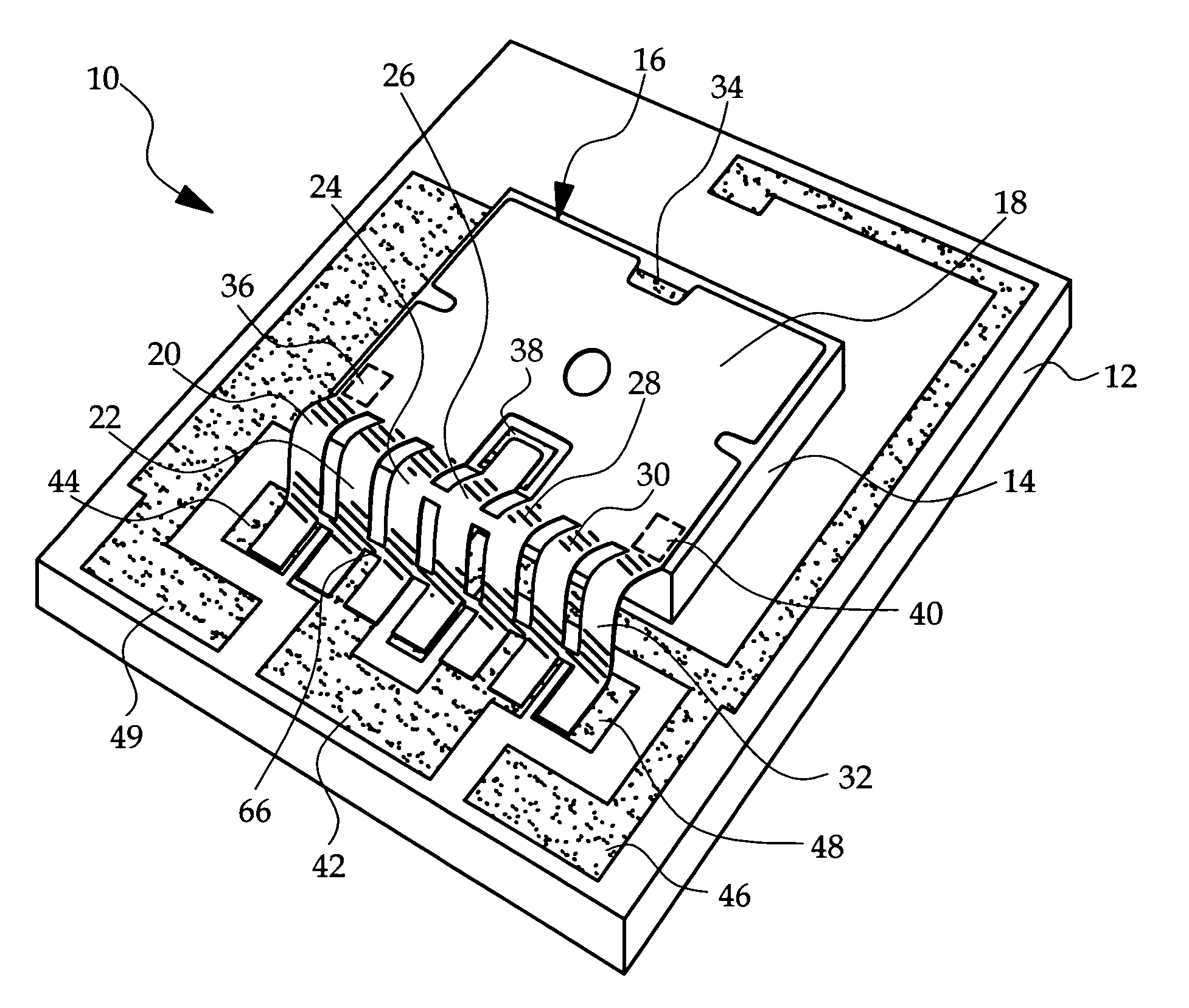

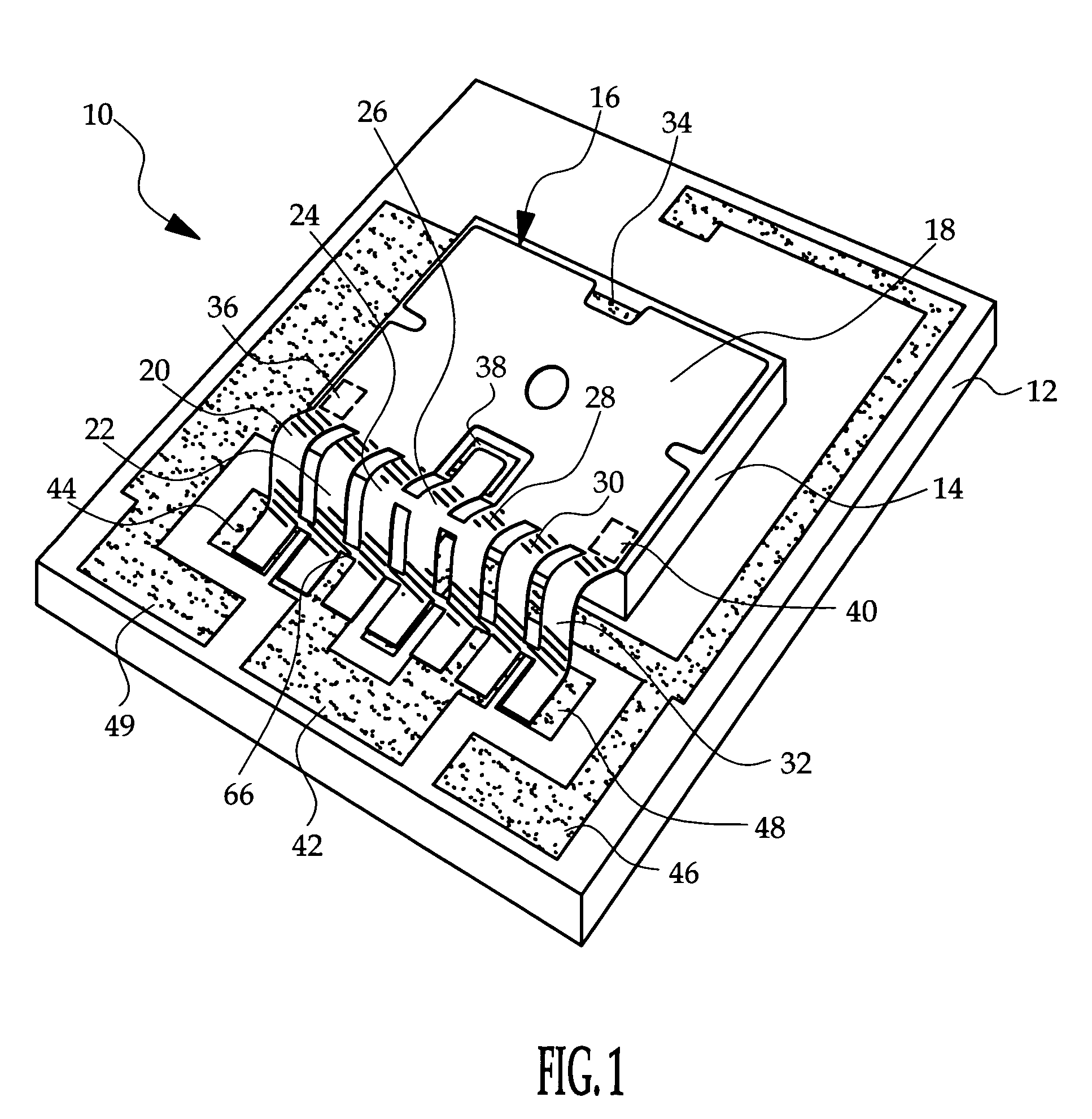

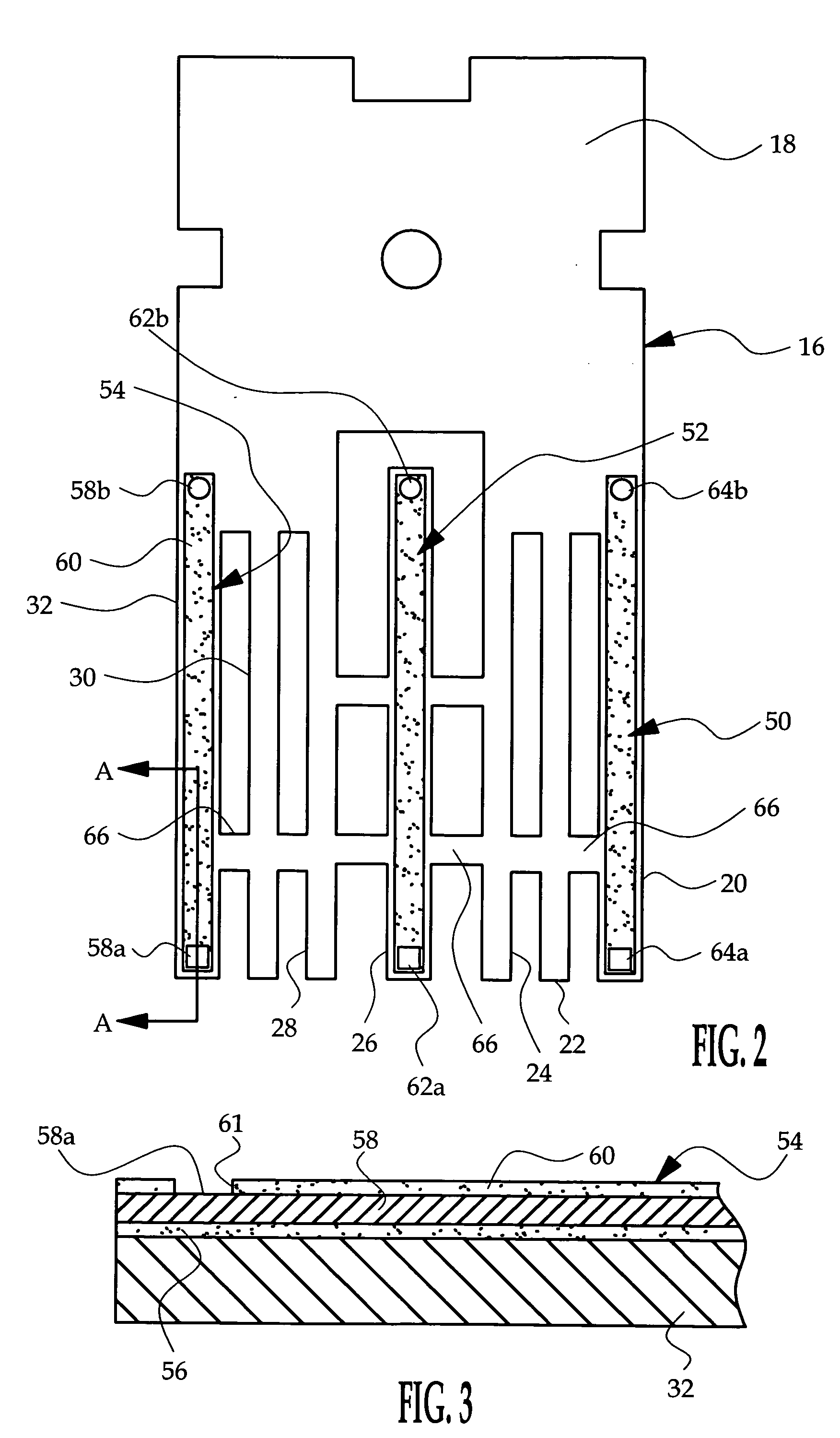

Multi-path bar bond connector for an integrated circuit assembly

InactiveUS20060038265A1Good for stress reliefEasy to adaptSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorSecondary circuit

A solderable bar bond connector establishes a primary interconnect between a substrate and a high current terminal of an IC chip mounted on the substrate, and one or more secondary interconnects between the substrate and low current terminals of the IC chip. The bar bond connector includes a plate portion soldered to the high current terminal of the IC chip and a plurality of leg elements extending from the plate portion to multiple bond sites on the substrate. The underside of at least one leg element is provided with a secondary circuit including a conductor that is electrically isolated from the respective leg element. The conductor of the secondary circuit is soldered to both the substrate and a low current terminal of the IC chip for establishing a secondary interconnect in addition to the primary interconnect established by the plate portion and the other leg elements.

Owner:RPX CORP

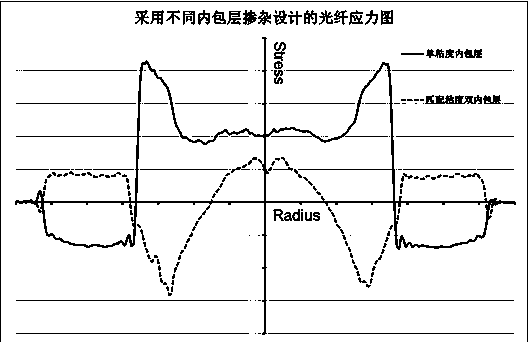

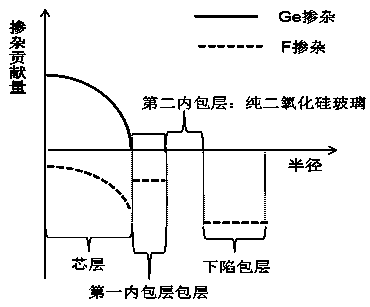

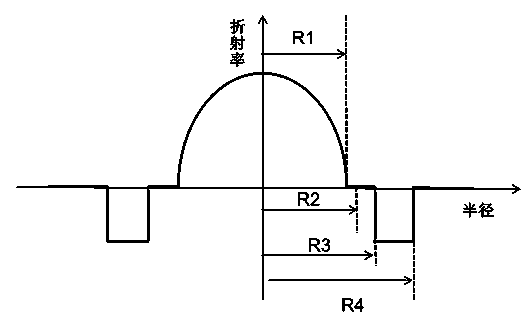

Bend-insensitive multimode fiber

InactiveCN104360435AReduced bend sensitivityGood for stress reliefOptical fibre with graded refractive index core/claddingOptical fibre with multilayer core/claddingRelative refractive indexDistributed index

The invention relates to a bend-insensitive multimode fiber comprising a core layer, inner sheath layers and an outer sheath layer. The bend-insensitive multimode fiber is characterized in that the radius R1 of the core layer is 23-26 micrometers, the refractivity section of the core layer is parabolic, the distribution index Alpha thereof is 1.9-2.2, a maximum relative refractive index difference Delta1 thereof is 0.9-1.2%, the first inner sheath layer, the second inner sheath layer and a recessed sheath layer are provided in order from inside to outside, the unilateral width of the first inner sheath layer is 1-3 micrometers, a relative refractive index difference Delta2 of the first inner sheath layer is -0.02-0.02%, the second inner sheath layer is an all-carbon dioxide layer 2-6 micrometers in unilateral width, the recessed sheath layer is an F-doped silica glass layer, and the recessed sheath layer is an all-silica glass layer. The double-inner-sheath structure of matching viscosity is used, the influence of drawing tension upon the core layer is reduced in terms of viscosity, and bend sensitiveness of the fiber is reduced; the width of the inner sheath layers and the size of the recessed sheath layer are reasonably optimized and designed, matching of the width and the size is achieved, and optimal width and size are acquired; meanwhile, excellent bend resistance and DMD (differential mode delay) performance are achieved.

Owner:YANGTZE OPTICAL FIBRE & CABLE CO LTD

Support method for high stress roadway coal-rock mass

InactiveCN102493821AImprove propertiesImprove self-supporting capacityUnderground chambersTunnel liningCoalEngineering

A support method for high stress roadway coal-rock mass includes constructing surface wall rocks into a tough transition seal layer after the roadway is excavated and formed, respectively intersecting and distributing a self-entrance type grouting long anchor rod and a short anchor rod into the roadway coal-rock mass, injecting rigid slurry materials and soft slurry materials in the wall rocks inlayering mode, constructing the rigid slurry-material-injected wall rock into a rigid support layer in situ, modifying the soft-slurry-injected wall rock into a soft decompression layer in situ, and forming a rigid and soft nesting transition layer at the mutual nesting position of the two layers. The support method for the high stress roadway coal-rock mass improves the capacity of deep rock mass of the roadway wall rocks for adapting to large deformation and self-bearing, improves a stress distribution state of the high stress roadway wall rocks, enables the high stress roadway to be formedat one step and supported at one step, ensures the stability of the roadway under the conditions of complex structures, high stress, large range loosening and crushing and large deformation.

Owner:TAIYUAN UNIV OF TECH

LED (Light Emitting Diode) chip for composite transparent conducting electrode and manufacturing method of LED chip

InactiveCN104505445AImproved ohmic contact characteristicsReduce processing difficultySemiconductor devicesThin membraneGraphite

The invention discloses an LED (Light Emitting Diode) chip for a composite transparent conducting electrode. The LED chip comprises a gallium nitride buffer layer, an N-GaN layer, a quantum well layer, a P-GaN layer and a composite transparent electrode layer which grow on a substrate in sequence. The LED chip is characterized in that an n-type electrode is manufactured on the N-GaN layer; a p-type electrode is manufactured on a graphene layer of the composite transparent electrode layer; the composite transparent electrode layer is formed by compounding a graphene laminar film and ZnO nanorods growing on the graphene laminar film. The invention also discloses a manufacturing method of the chip. The graphene laminar film / ZnO nanorod compounded transparent electrode layer formed by the manufacturing method has the advantages of capability of preventing cracking and good light transmittance performance and is easy to process, so that the contact performance, the current expansion performance and the transmissivity of the chip are greatly improved, and the production cost of the subsequent chip technology can be greatly reduced.

Owner:GUANGDONG DELI PHOTOELECTRIC

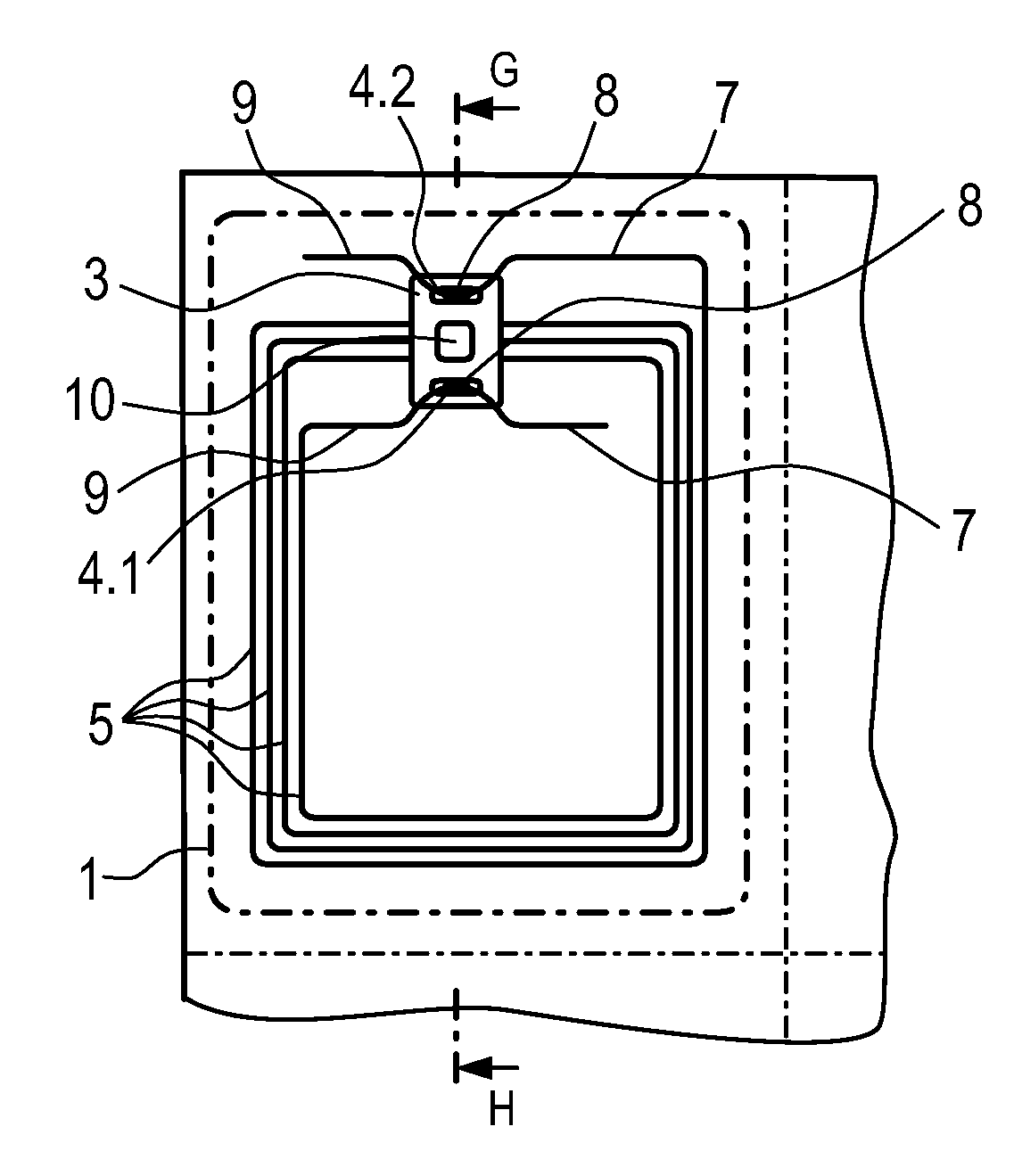

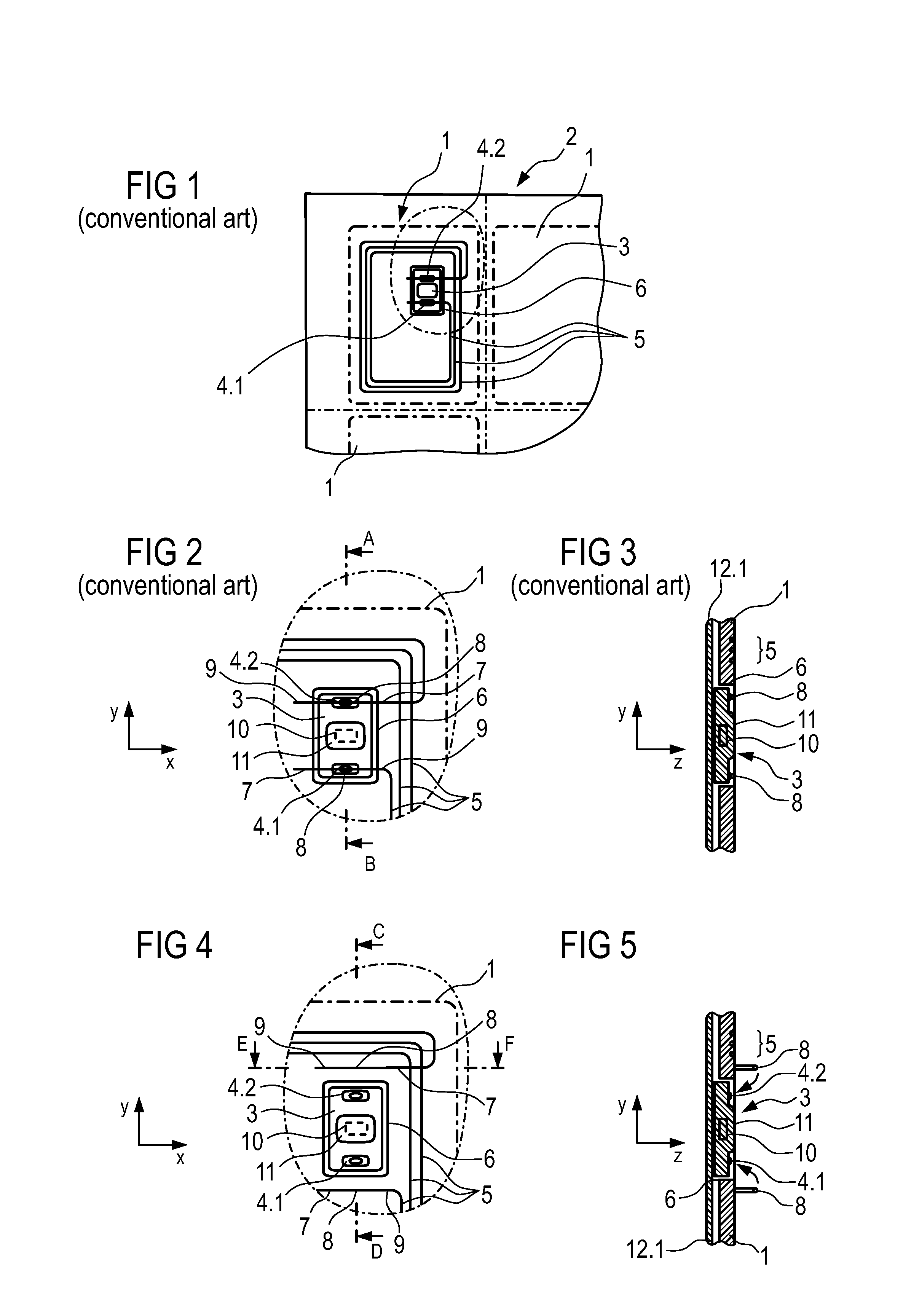

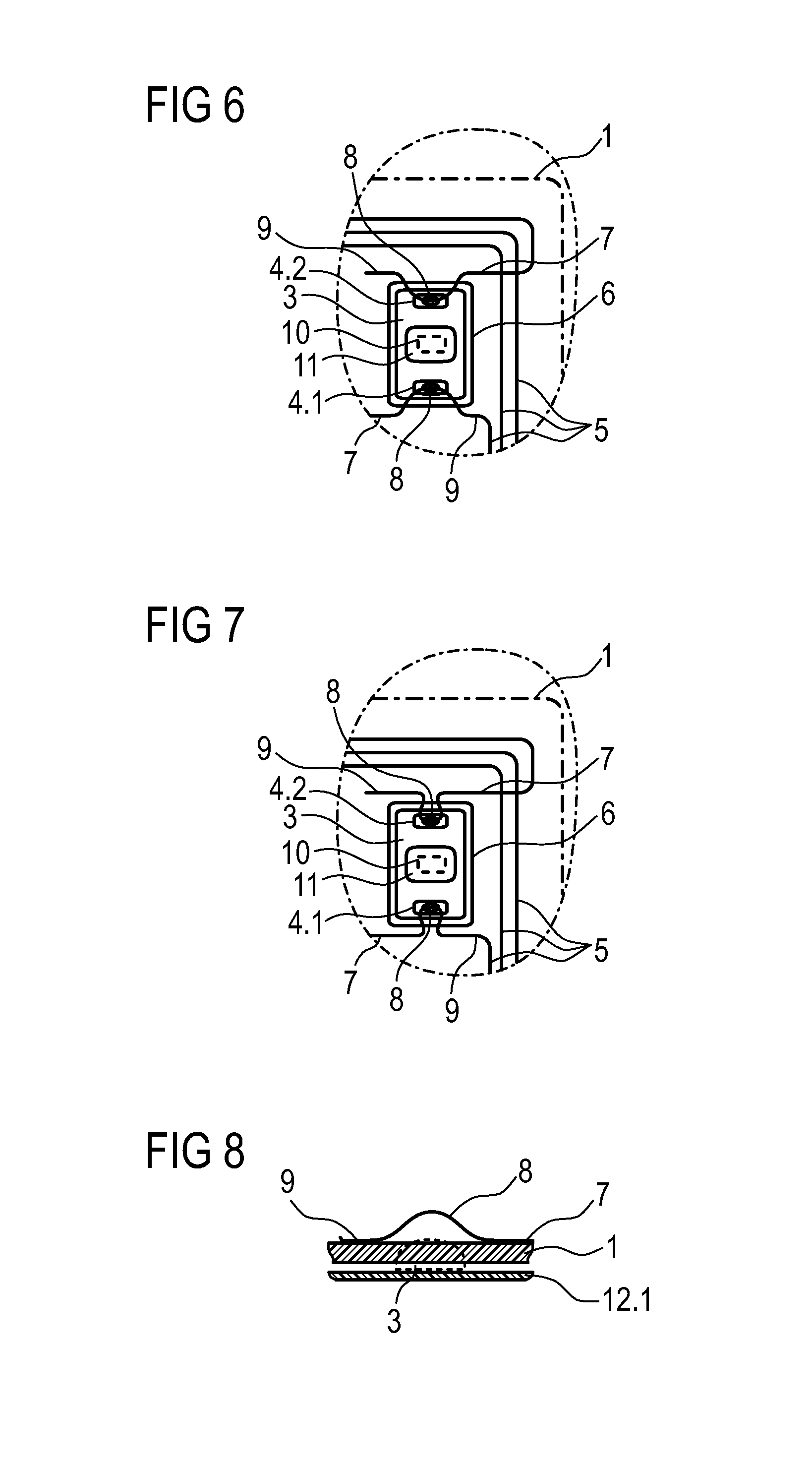

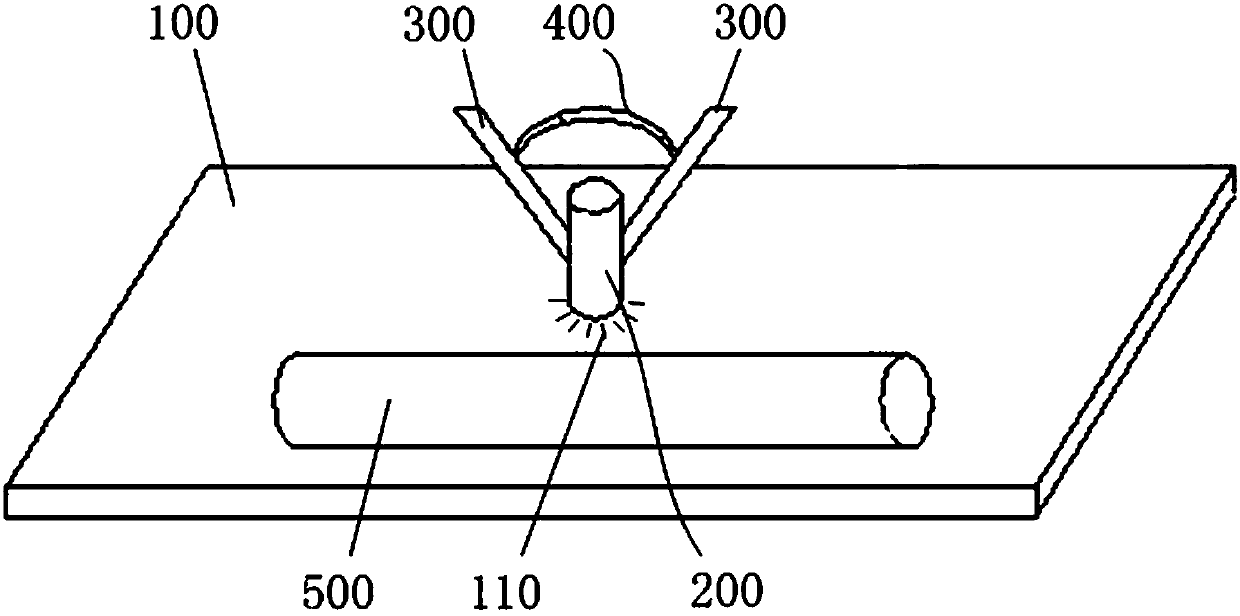

Method and arrangement for producing a smart card

ActiveUS20090000107A1Save headroomMore headroomPrinted circuit assemblingSemiconductor/solid-state device testing/measurementSmart cardEngineering

A method is provided for producing a smart card comprising a chip module with at least one contacting area, the chip module arrangeable in a mounting location of a substrate, wherein one contacting loop is formed from a wire connector fed by a wire guiding unit for at least one of the contacting areas, respectively by attaching a first section of the wire conductor to a surface of the substrate outside the mounting location, wherein a second section of the wire conductor proximate to the first section is guided to form the contacting loop along with and protruding from the surface, wherein a subsequent third section of the wire conductor is attached to the surface outside the mounting location, wherein the chip module is inserted into the mounting location and wherein the second section is bent over and electrically contacted to the contacting area.

Owner:RUHLAMAT

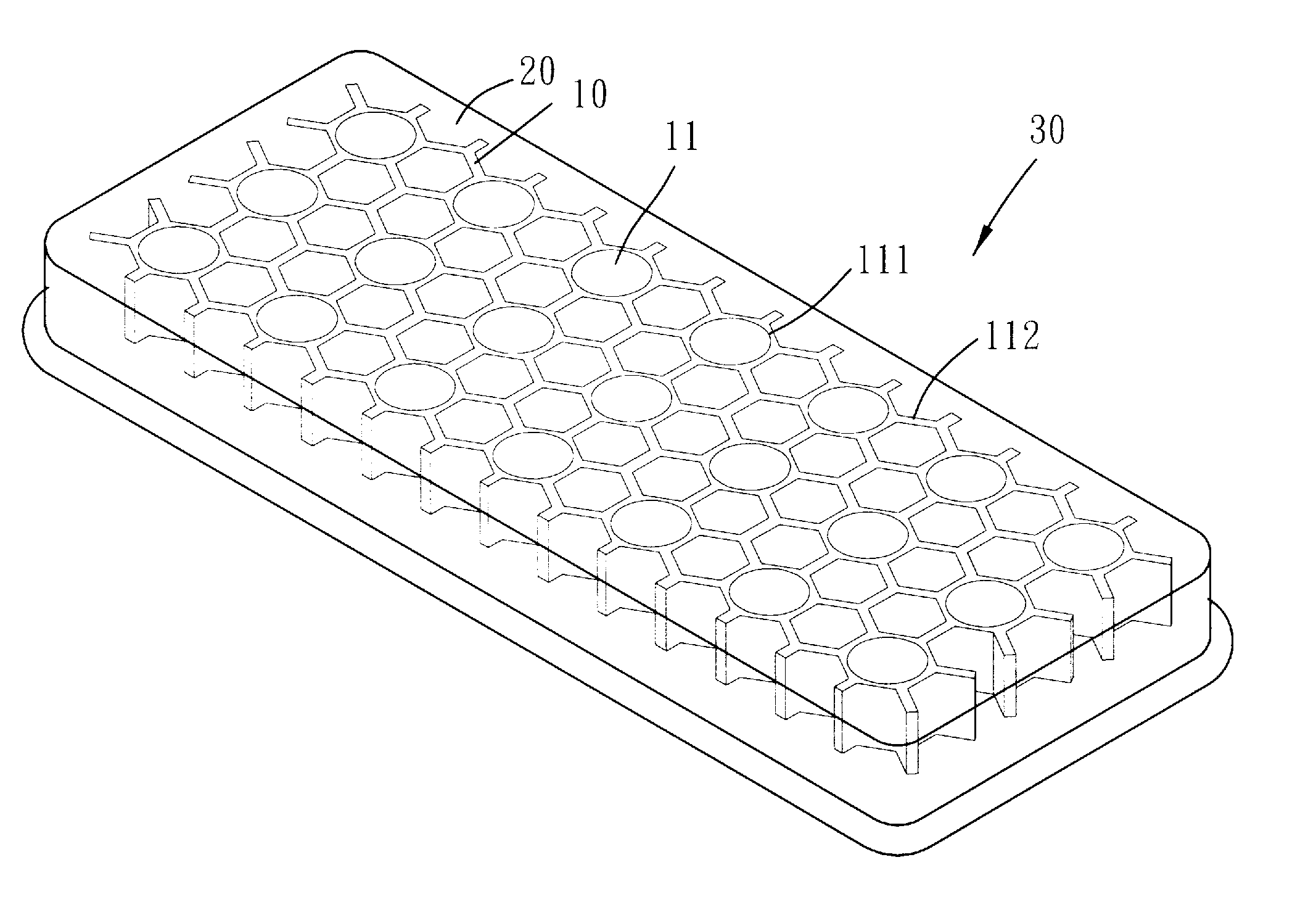

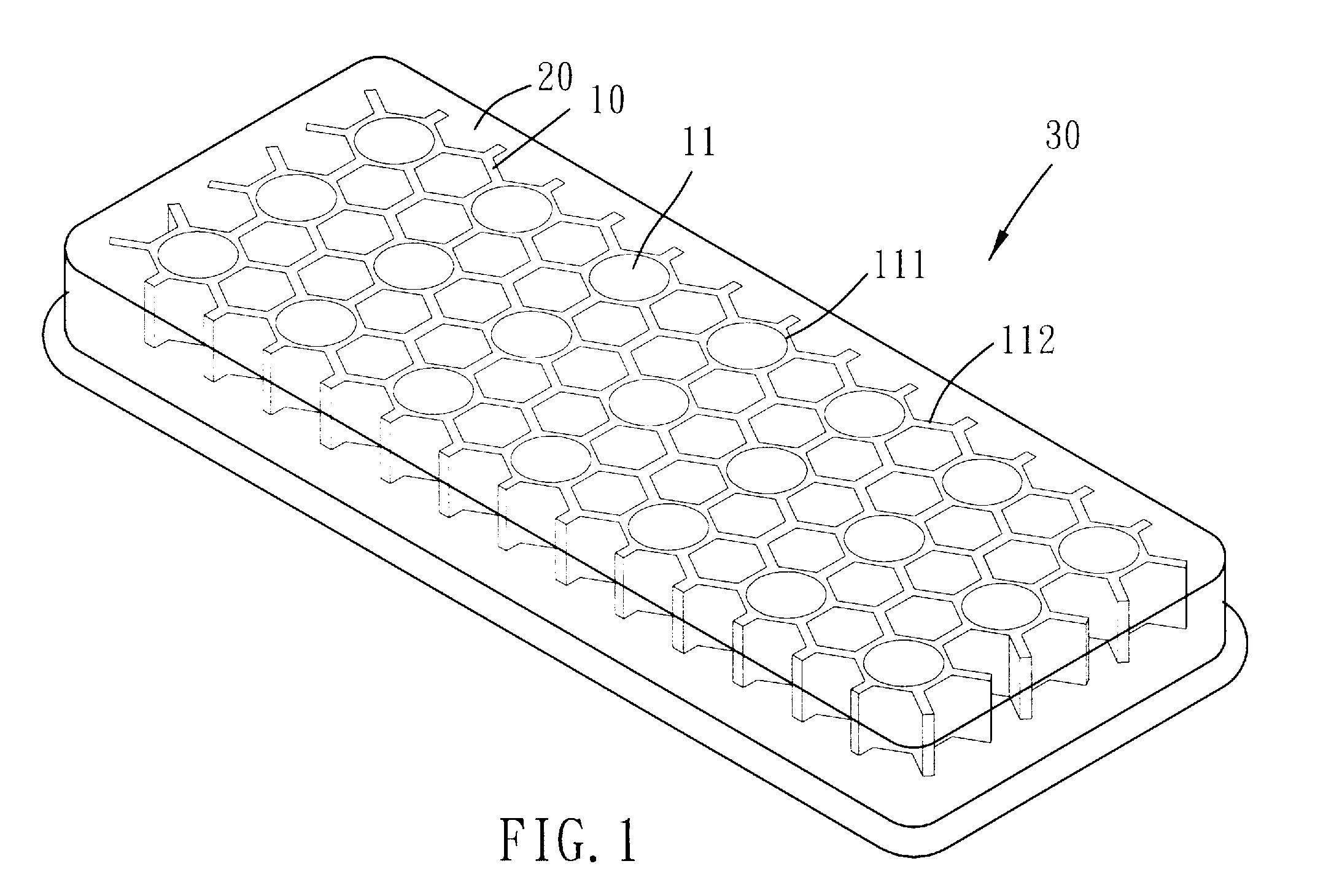

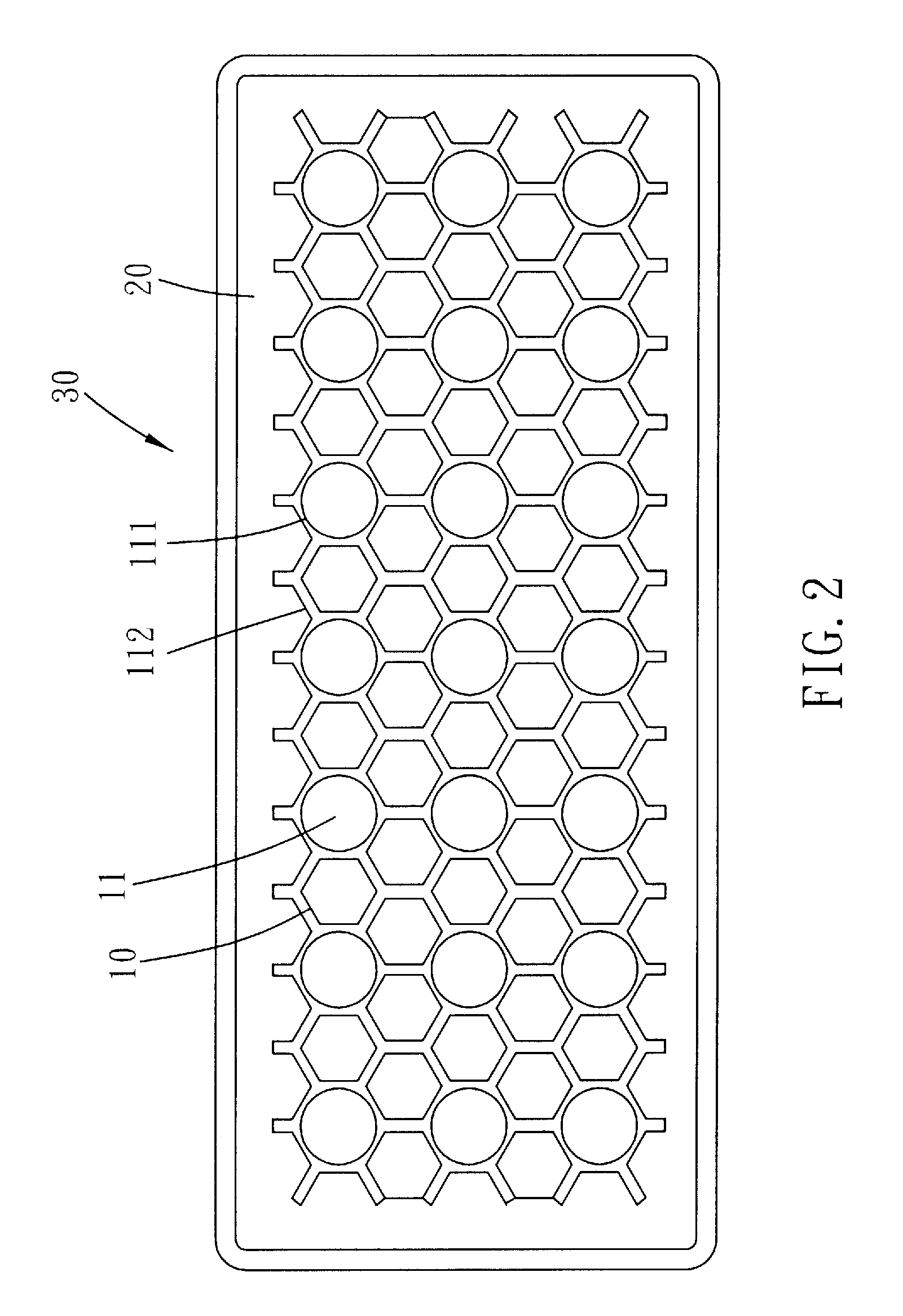

Soft cushion structure

InactiveUS20110064911A1Stable supportEffective distributionSolesLayered productsElastomerEngineering

A soft cushion structure of the present invention includes a soft foaming resilient supportive body and a soft elastomer. The soft foaming resilient supportive body has one or more penetrating holes which communicate upper and under gel rooms disposed on the soft foaming resilient supportive body. The soft elastomer is filled in the holes and at least a part of the upper and under gel rooms respectively, so as to combine the soft elastomer with the soft foaming resilient supportive body to form a composite structure.

Owner:KUO CHUN FU

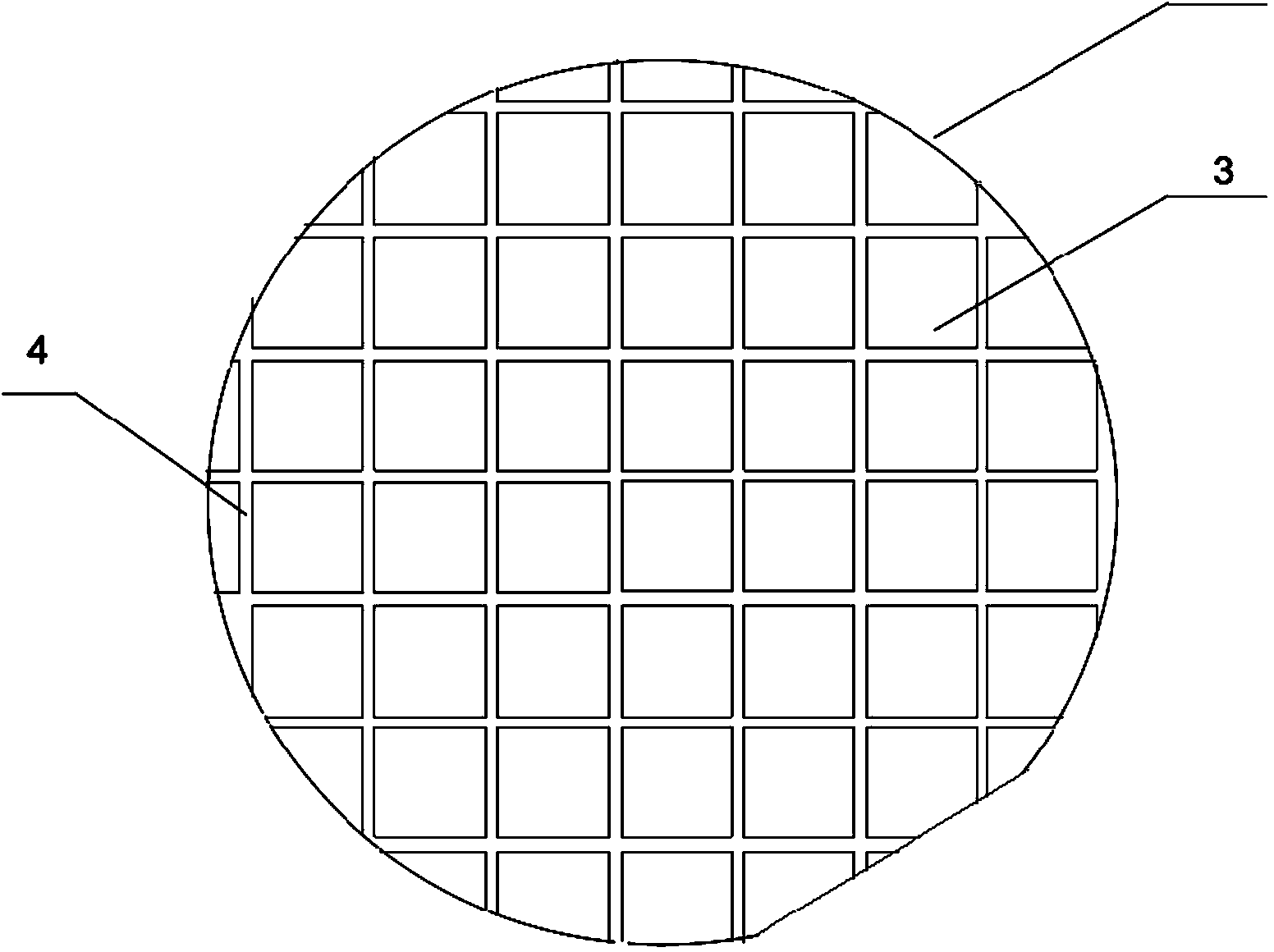

Rectangular patterned Si substrate AlN template for GaN semiconductor material epitaxy and preparation method of rectangular patterned Si substrate AlN template

ActiveCN104018214AAvoid destructionPrevent edge topography from deterioratingPolycrystalline material growthSemiconductor/solid-state device manufacturingSemiconductor materialsCrystal orientation

The invention relates to a rectangular patterned Si substrate AlN template for a GaN semiconductor material epitaxy. The rectangular patterned Si substrate AlN template comprises a Si substrate and an AlN template layer epitaxially growing on the Si substrate with a crystal plane (111) as a crystal orientation, a plurality of mutually perpendicular strip-shaped grooves are etched on the AlN template layer to form a plurality of rectangular platforms which are independent with each other. The invention also relates to a method for preparing the patterned Si substrate AlN template. The method comprises the following steps of cleaning the substrate, growing the AlN layer and etching the rectangular platform. According to the rectangular patterned Si substrate AlN template for the GaN semiconductor material epitaxy, the yield is high and the cost is low, the prepared products have good uniformity and high quality.

Owner:广州市艾佛光通科技有限公司

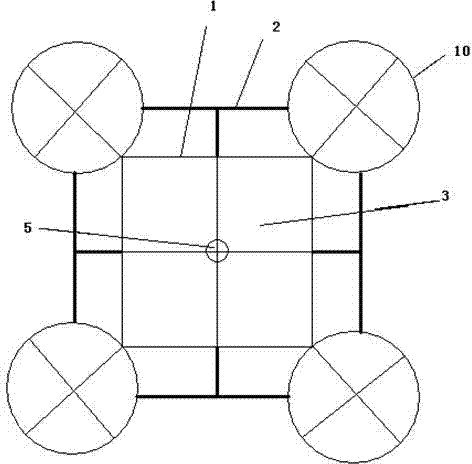

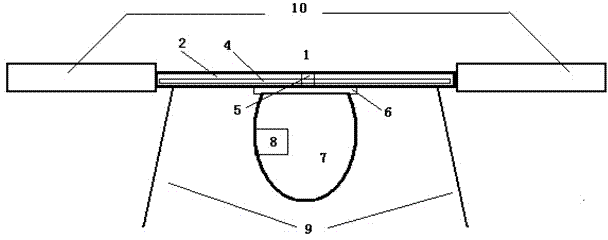

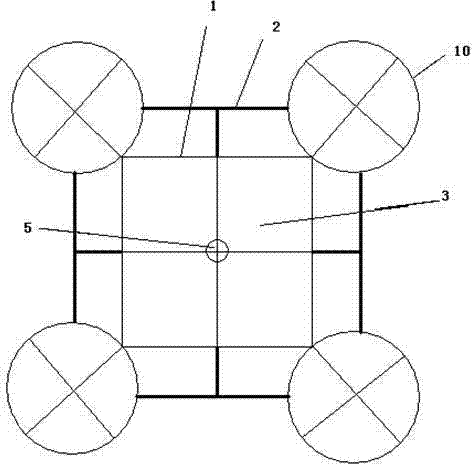

Solar electric helicopter

InactiveCN102602540AMeet environmental protection and energy savingImprove flight capacityEfficient propulsion technologiesDepending on number of propellersPropellerElectric equipment

The invention relates to a helicopter using solar energy and storage batteries, which comprises a body, a frame, a solar panel and a storage battery set. The frame is fixed on the body. The solar panel is disposed on the upper surface of the storage battery set which is mounted on the body and / or the frame. A propeller is fixed on the frame. A cab is hinged to the body through rotary shafts. A controller for controlling rotation of the propeller and the cab is disposed in the cab. A landing support for stabilizing the helicopter in landing is connected with the frame. The helicopter is powered by electric energy only, using the solar panel to generate power supplied to electric equipment in the helicopter in real time can meet the double requirements of environmental friendliness and energy conservation and greatly improved flying capacity, and the helicopter is low in manufacturing process requirements, simple and accurate in operation, convenient in management, low in maintenance, environment-friendly, energy-saving, high in flying capacity, long in airborne period, high in reliability, high in energy conservation rate, widely applicable to civil fields of practical flying training, aerial surveillance.

Owner:SOUTH CHINA NORMAL UNIVERSITY

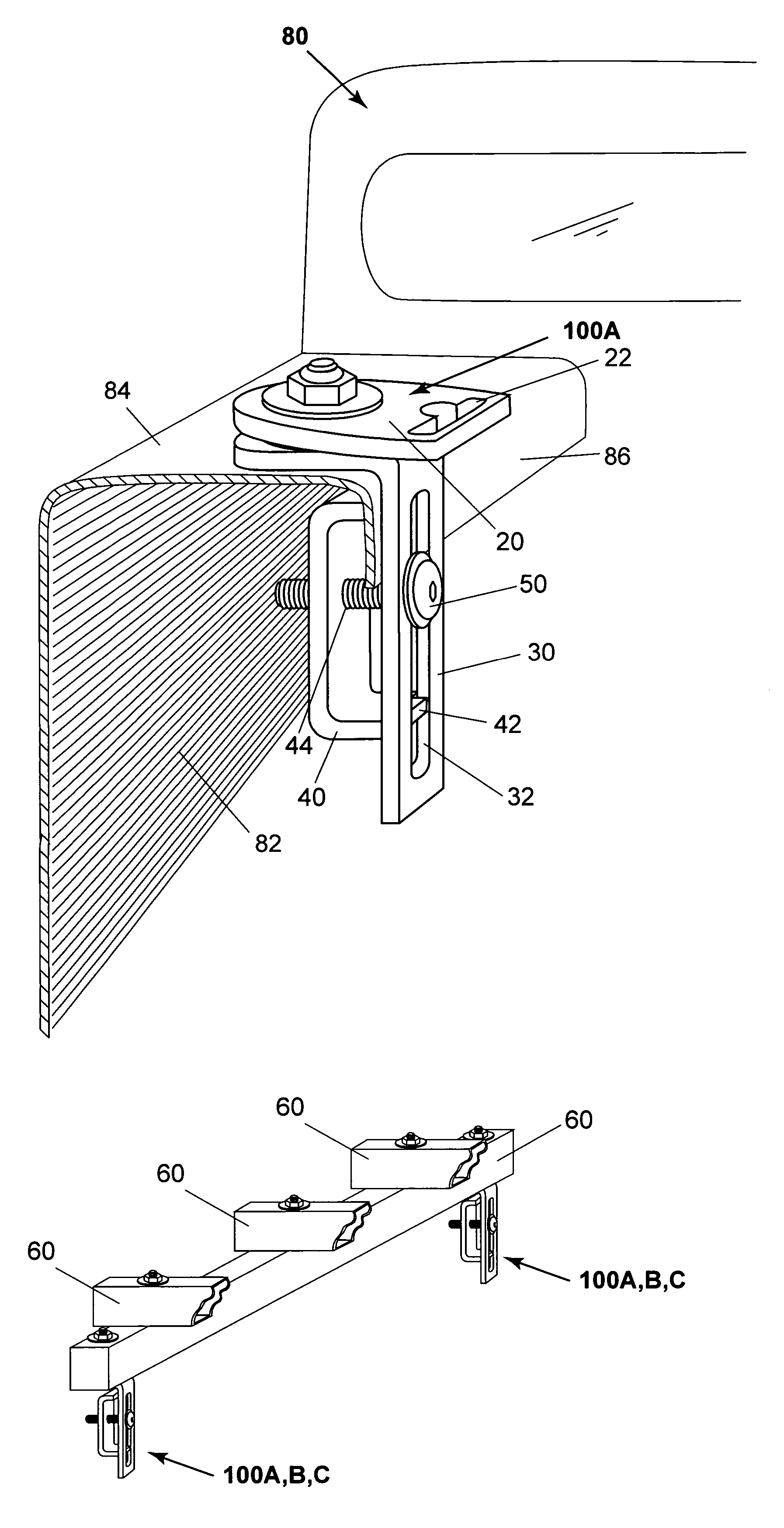

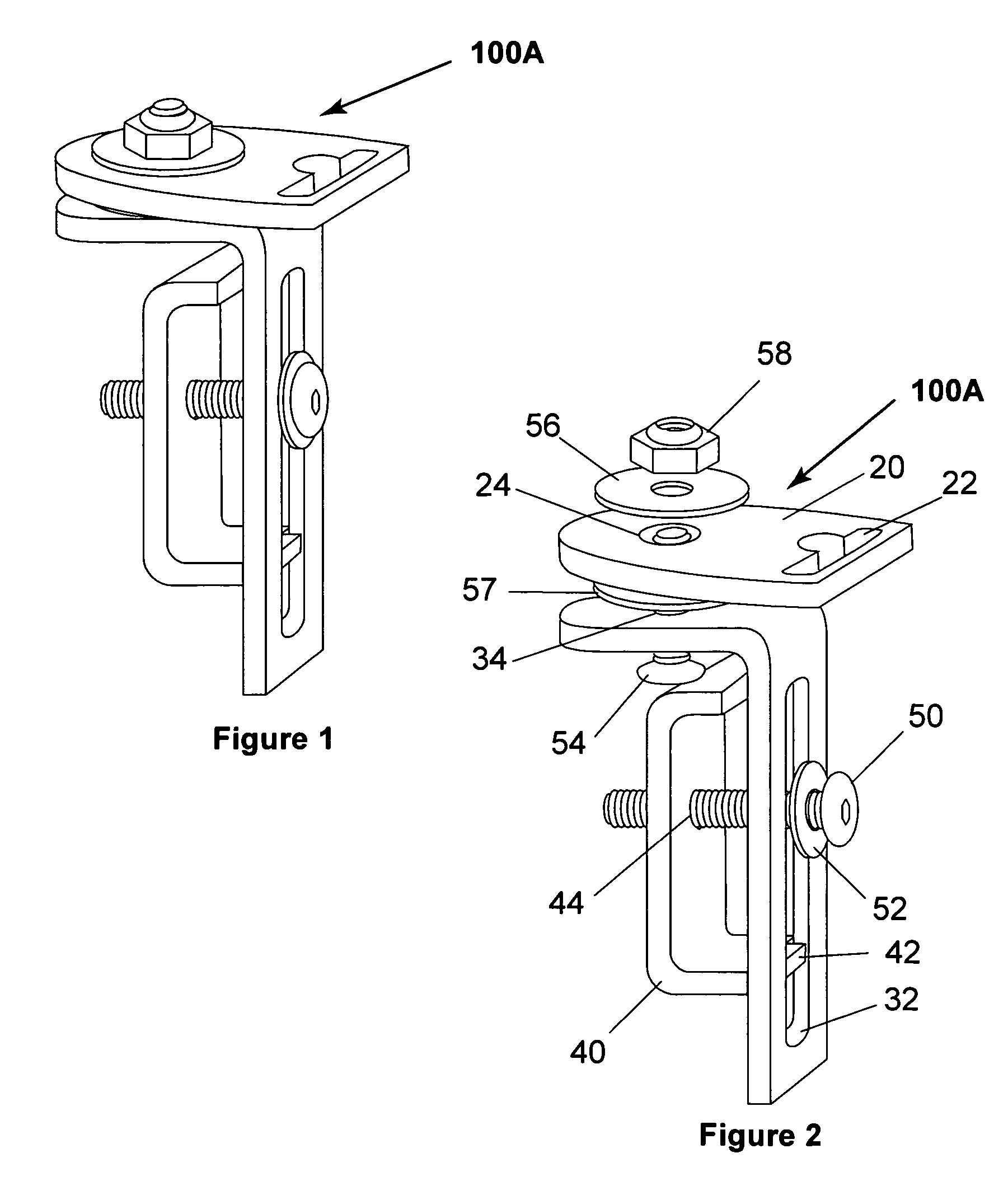

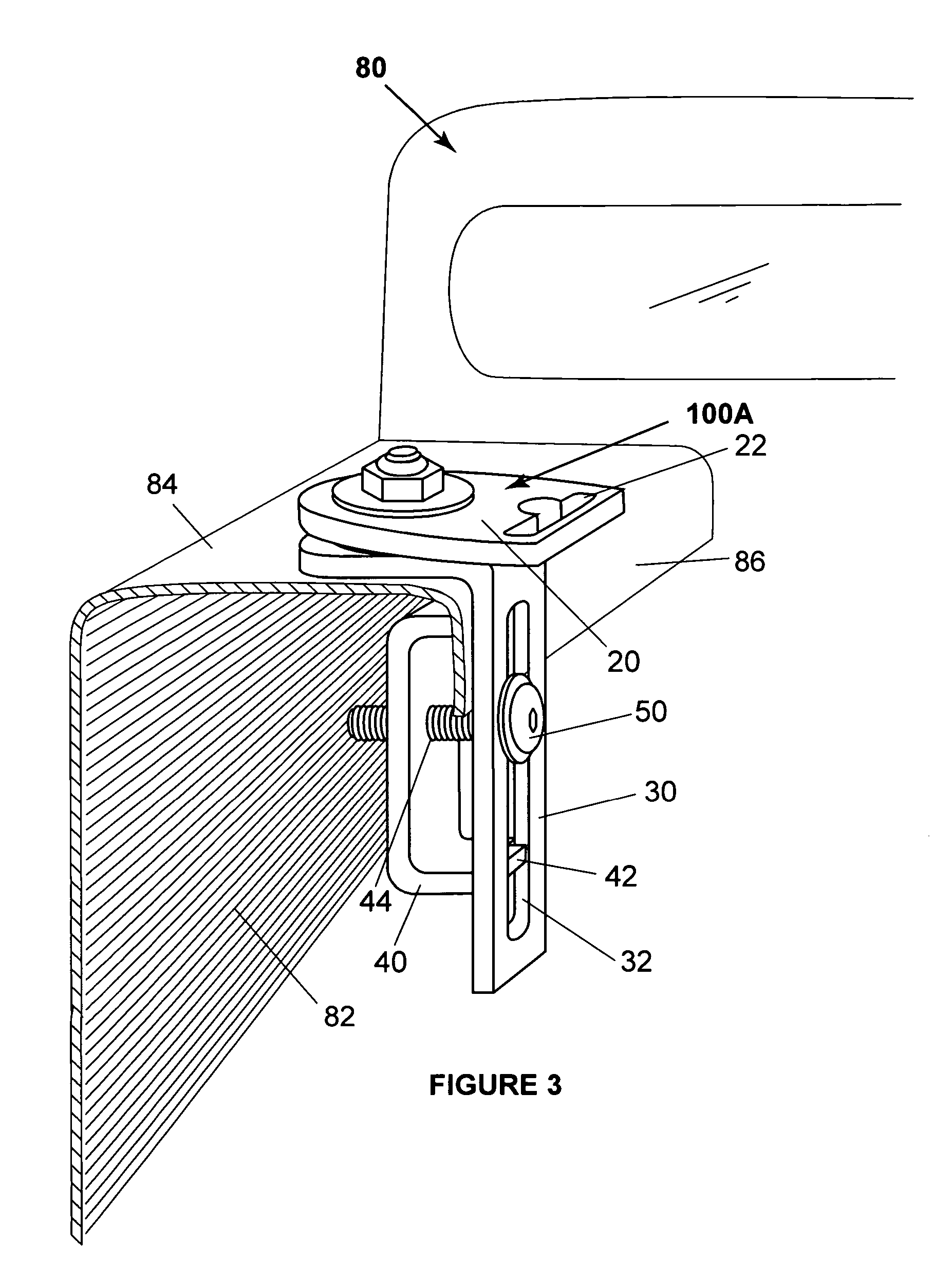

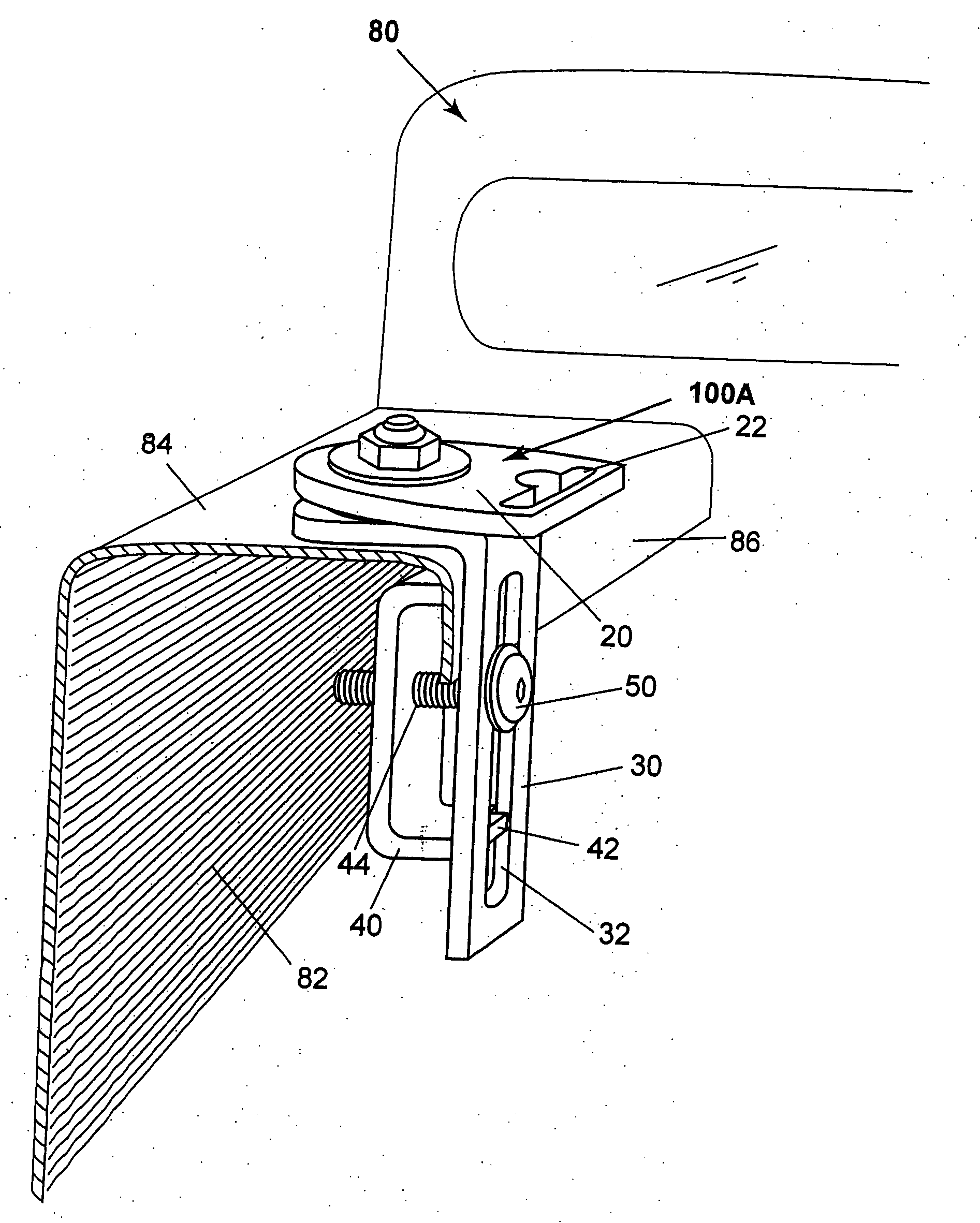

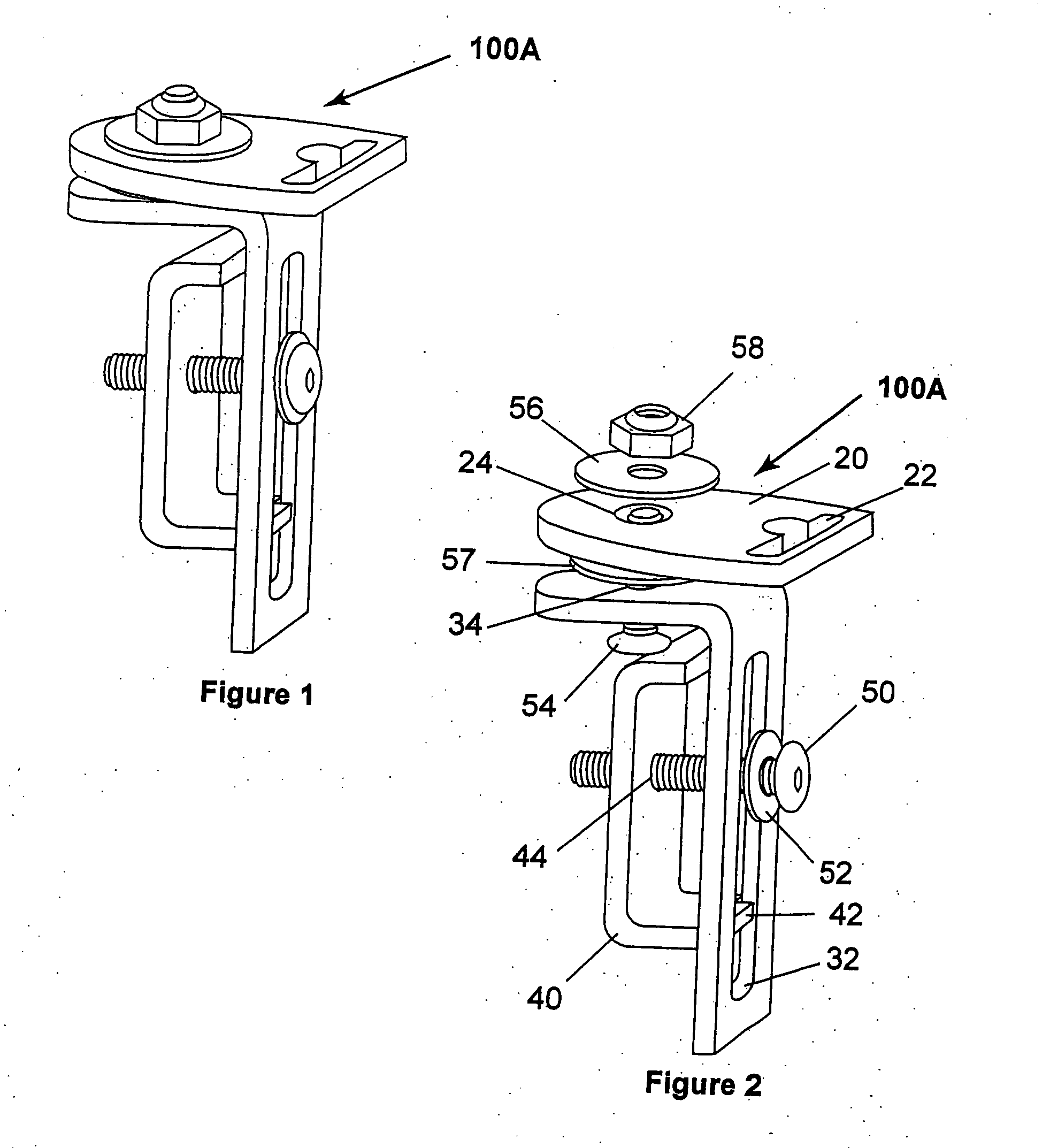

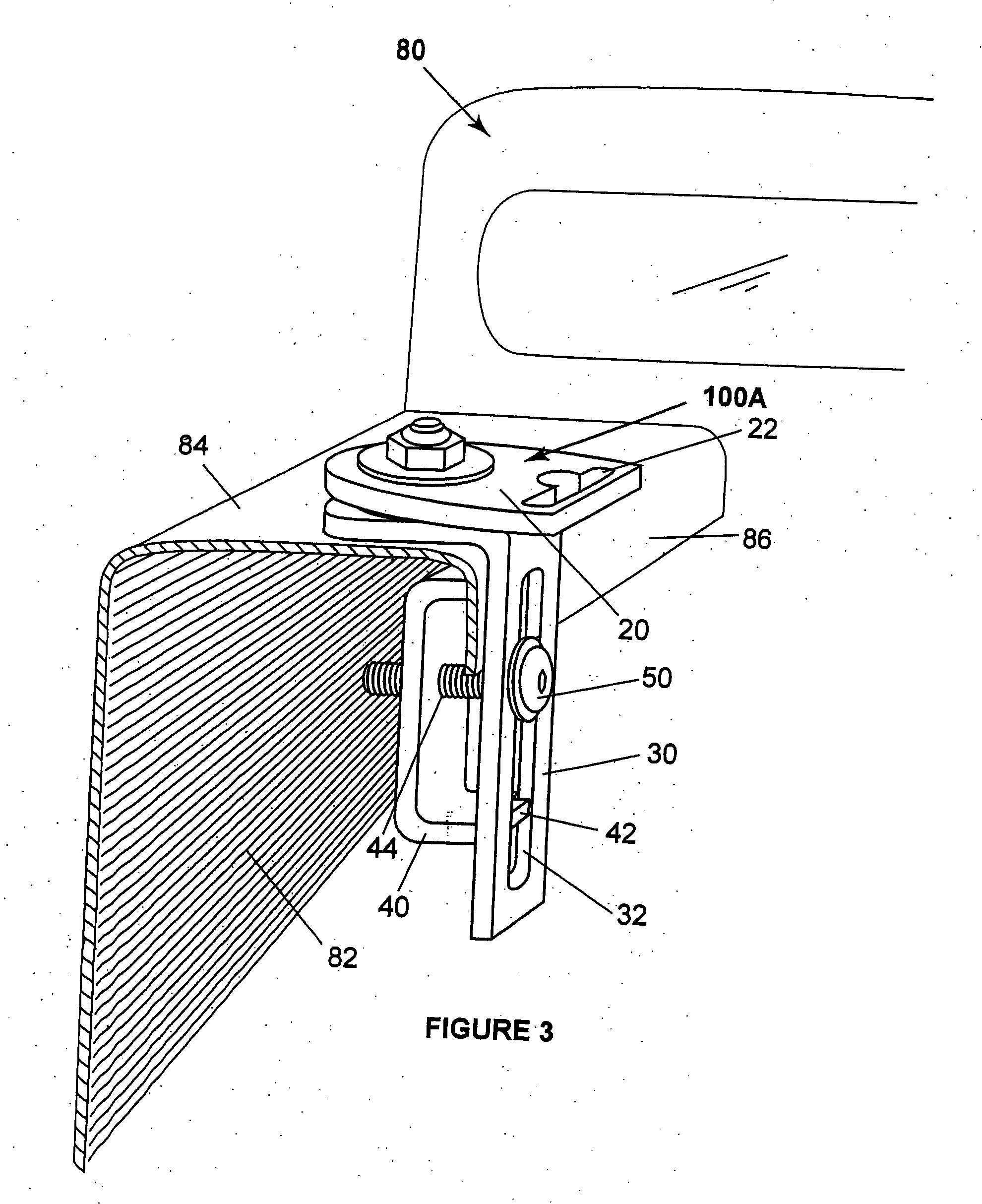

Cargo restraint anchor device for pick-up trucks

Herein is disclosed an improvement for a tie-down and attach-point anchor device for pickup truck beds that clamps to the downward protruding flange of a pickup truck's inner side rail or other similar available surface having an exposed edge. The anchor incorporating a slotted head capable of swiveling to accommodate different angles at which straps, bungees, ropes, and rigid members may be placed to secure or support cargo.

Owner:FISHING SCI

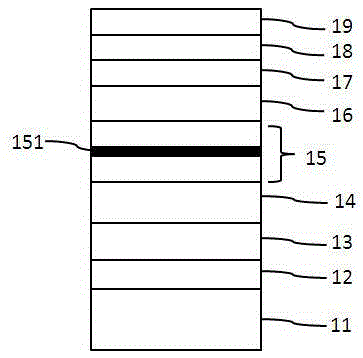

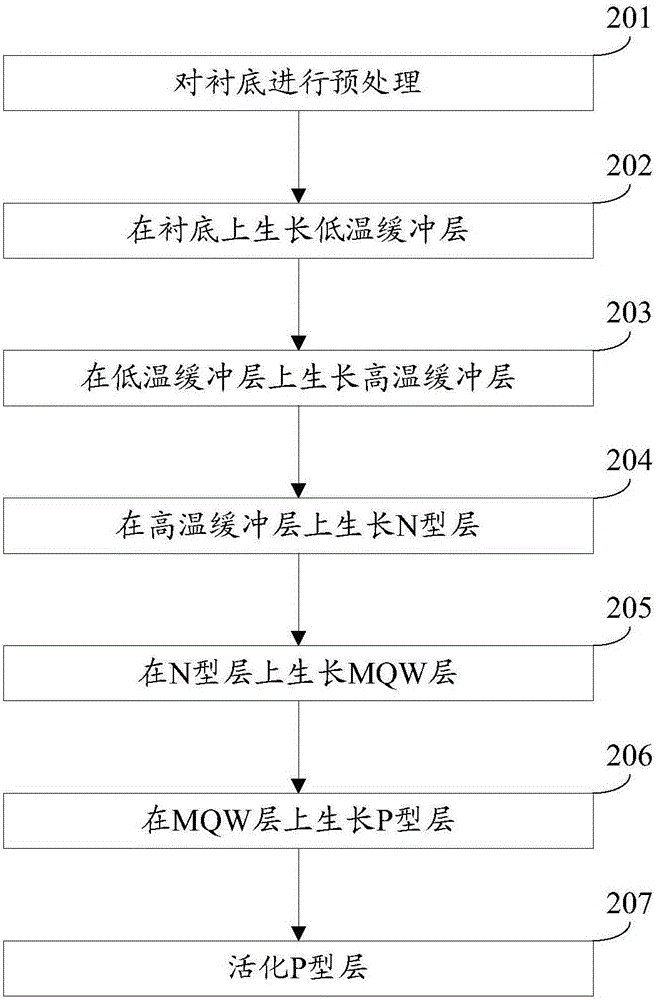

Growth method for light-emitting diode epitaxial wafer

ActiveCN106449915AWon't breakGood for stress reliefSemiconductor devicesQuantum wellLight-emitting diode

The invention discloses a growth method for a light-emitting diode epitaxial wafer, and belongs to the technical field of a semiconductor. The growth method comprises the steps of enabling a low-temperature buffer layer, a high-temperature buffer layer, an N type layer, an MQW layer and a P type layer to be grown on a substrate in sequence, wherein the MQW layer comprises an InGaN quantum well layer and a GaN quantum barrier layer which are laminated alternately; the quantum well layer comprises a first type quantum well, a second type quantum well, and a third type quantum well; the growth temperature of the quantum well layers in the first type quantum well is lowered layer by layer; the In content of the quantum well layers in the second type quantum well is changed layer by layer; the ratio of the In content to Ga content in the quantum well layers in the third type quantum well is decreased layer by layer; and the quantum well layers belong to the first type quantum well, the second type quantum well layer and the third type quantum well in the growth direction of the light-emitting diode epitaxial wafer in sequence. By adoption of the growth method, the overlapping degree of an electron wave function and a hole wave function can be effectively improved, and the light emitting efficiency of the LED is finally improved.

Owner:HC SEMITEK ZHEJIANG CO LTD

Acrylic pressure-sensitive adhesive composition for polarizing plate, containing a photo-initiator group

ActiveUS8337961B2Good for stress reliefImprove light leakageLiquid crystal compositionsEster polymer adhesivesPolymer scienceMeth-

The present invention relates to an acrylic pressure-sensitive adhesive composition which comprises a (meth)acrylic copolymer comprising an alkyl(meth)acrylic acid ester monomer, in which alkyl has 2 to 14 carbon atoms, and a (meth)acrylic acid ester monomer containing a copolymerizable photo-initiator group, wherein it has a gel fraction of 10 to 55% and a swelling ratio of 30 to 110, and a sol (uncross-linked polymer) eluted in final pressure-sensitive adhesive with a solvent (ethyl acetate) has a weight average molecular weight of 600,000 or more; and a polarizing plate and a liquid crystal display device, comprising the same. The polarizing plate according to the present invention has an excellent adhesion durability under a high temperature or a high temperature and humidity condition, has an excellent low light leakage property by effectively providing stress release property, and may greatly improve productivity for polarizing plates, by using photo-curing.

Owner:SHANJIN OPTOELECTRONICS (NANJING) CO LTD

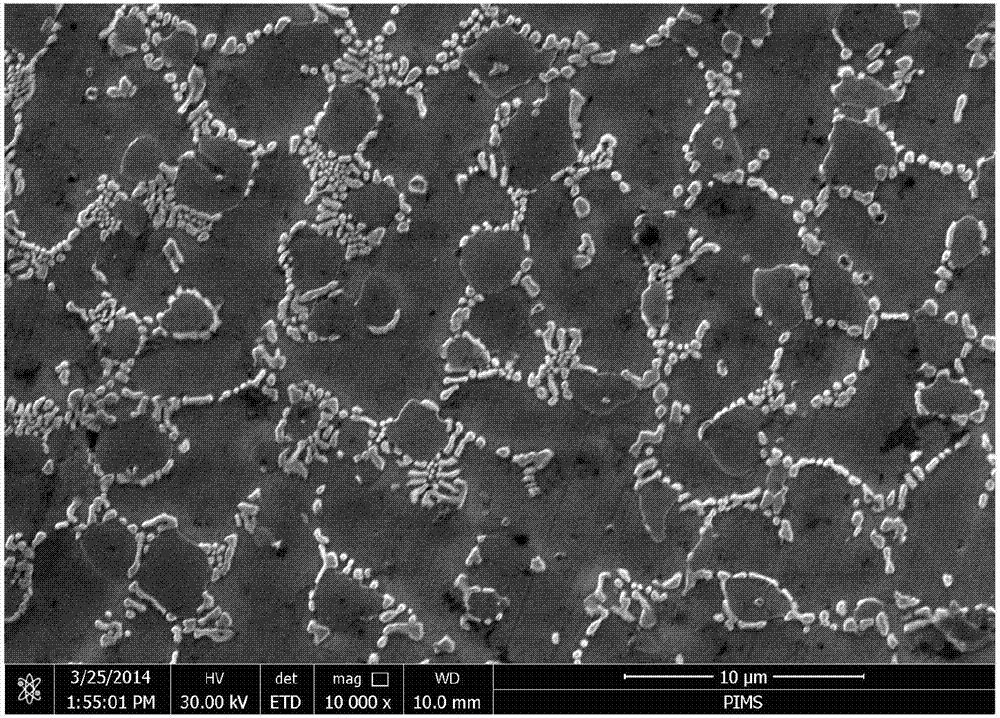

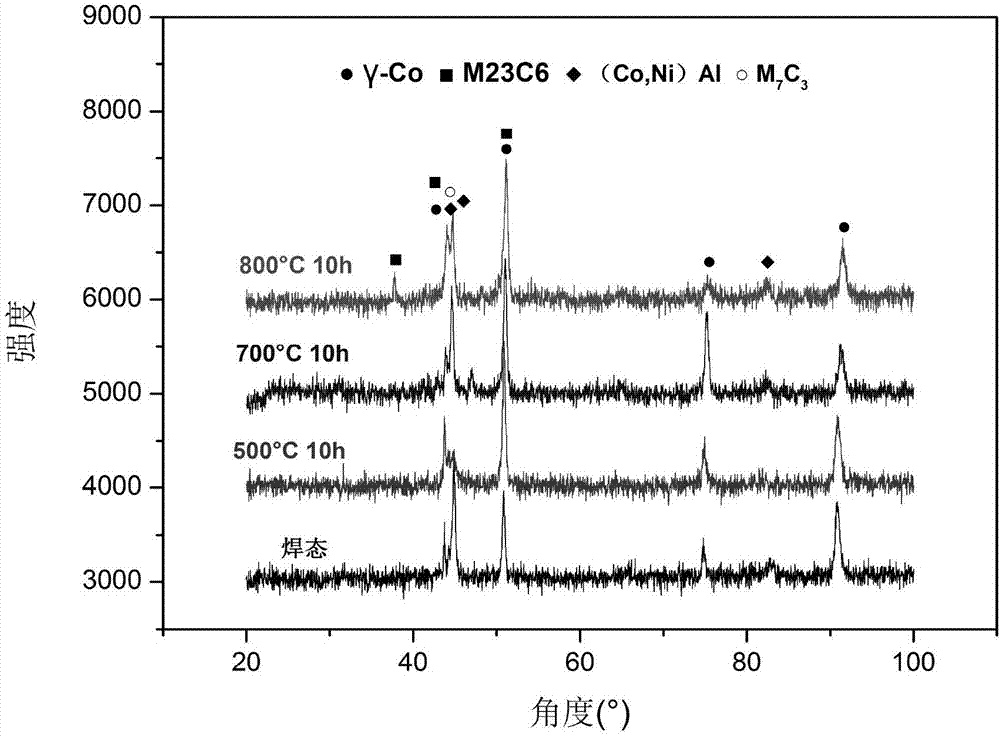

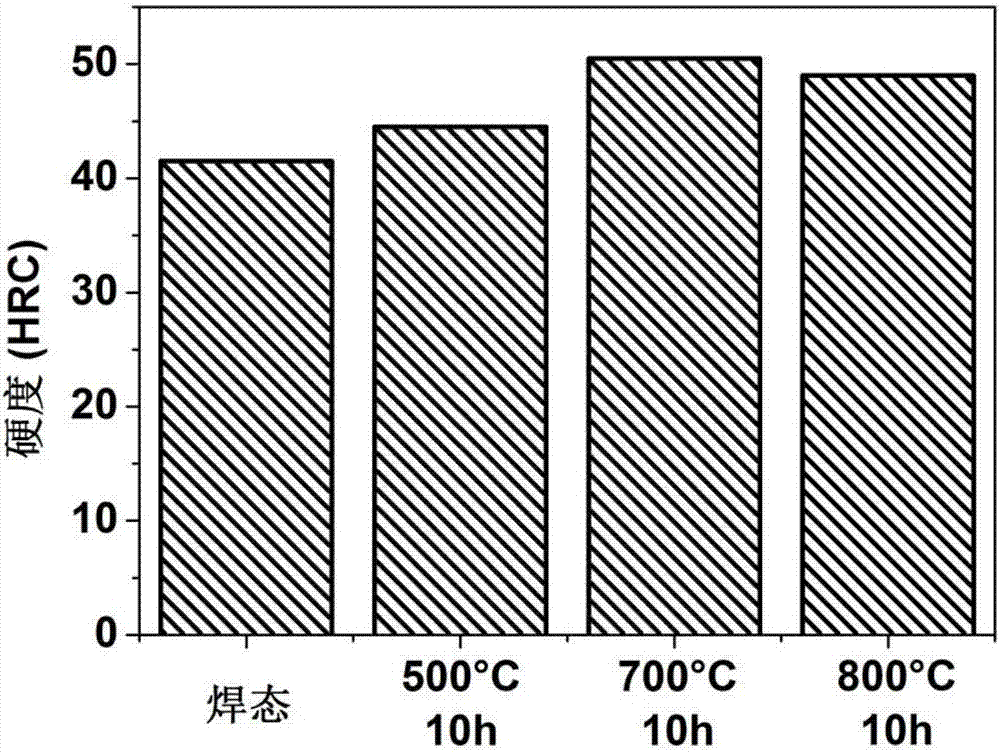

Cobalt-based alloy and cladding layer prepared from cobalt-based alloy

ActiveCN107326221AImproves abrasive wear resistanceBlock the path to rapid expansionMolten spray coatingChemical compositionMetallic materials

Provided are a cobalt-based alloy and a cladding layer prepared from the cobalt-based alloy. The cobalt-based alloy comprises Co, Ni, Cr, Fe, Si, W, C and Al. The cobalt-based alloy is specifically prepared from, by weight, 19-22.5% of Ni, 18-19.5% of Cr, 7.5-10.5% of Al, 0.8-1.1% of Fe, 0.7-1.0% of Si, 3.0-4.4% of W, 0.6-0.9% of C, and the balance Co and smaller than 0.1% of inevitable impurities, and the mass percent of Ni and Co is greater than 0.4 but smaller than 0.56, and the mass percent of Ni and Al is greater than 2 but smaller than 2.7. The cobalt-based alloy can be used for preparing the cladding layer with high abrasion resistance performance and heat fatigue resistance performance, and the cladding layer not only can be used for repairing and enhancing a friction layer of a brake disc, but also can be used as the friction layer of the brake disc and a protection layer on the surface of other metal materials needing to bear repeated heat impact and having friction abrasion in the environments like mold cavity linings, engine pistons and inner cylinders, petroleum pipeline valve inner walls.

Owner:SOUTHWEST JIAOTONG UNIV

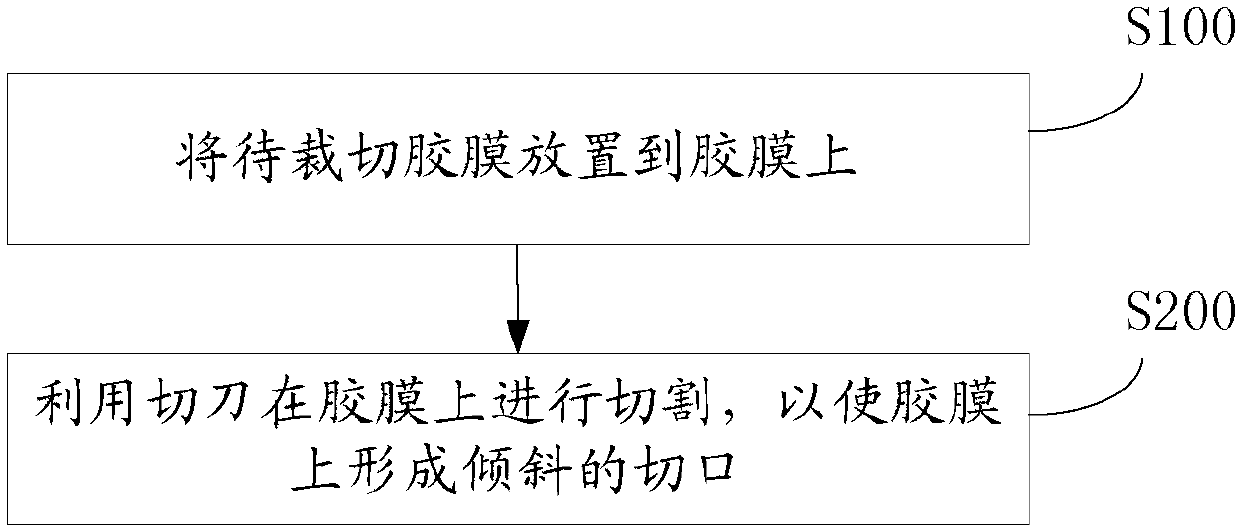

Method and device for releasing stress of flexible photovoltaic module packaging film

InactiveCN107768286AReduced risk of wrinklingImprove efficiency and cutting accuracySynthetic resin layered productsSemiconductor/solid-state device manufacturingFilm materialBiomedical engineering

The invention discloses a method and a device for releasing the stress of a flexible photovoltaic module packaging film. The method includes the following steps: placing a to-be-cut film on a feedingmechanism; using a cutter to cut the film to form an oblique cut on the film; and starting the feeding mechanism, driving the to-be-cut film roll to move along the axial direction thereof in order tomove the cut out of the cutting position of the cutter, and moving the next to-be-cut position of the to-be-cut film roll to the cutting position. According to the method and the device for releasingthe stress of a flexible photovoltaic module packaging film provided by the invention, the stress and shrinkage of a packaging film can be released without changing the amount of packaging film material used, and the risk of wrinkles is reduced. Meanwhile, through automatic packaging film feeding, the efficiency and precision of packaging film cutting are improved, and the stress release effect isstrengthened.

Owner:MIASOLE EQUIP INTEGRATIONFUJIANCO LTD

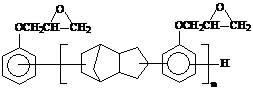

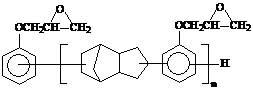

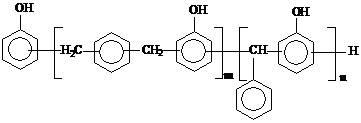

Epoxy resin composition for semiconductor packaging and preparation method thereof

ActiveCN102432980ALow costReduce stressSemiconductor/solid-state device detailsSolid-state devicesEpoxySemiconductor package

The invention discloses an epoxy resin composition for semiconductor packaging, which comprises epoxy resin, curing agent, curing agent promoter and inorganic filler, and is characterized in that: the epoxy resin is the epoxy resin with the formula (1) and / or the formula (2); the weight of the epoxy resin is 1-25% of the total weight of the epoxy resin composition; the curing agent is phenolic resin containing the phenolic resin with the formula (6) or any one or more of the phenolic resins represented by the formula (3), the formula (4) and the formula (5); and the invention further discloses a preparation method of the epoxy resin composition. By optimizing types of the epoxy resin and adding the curing agent with uniformly flexible segments, and the like, the invention provides the resin composition of the curing agent with low cost, low stress, high reliability and excellent flow property.

Owner:JIANGSU HHCK NEW MATERIAL CO LTD

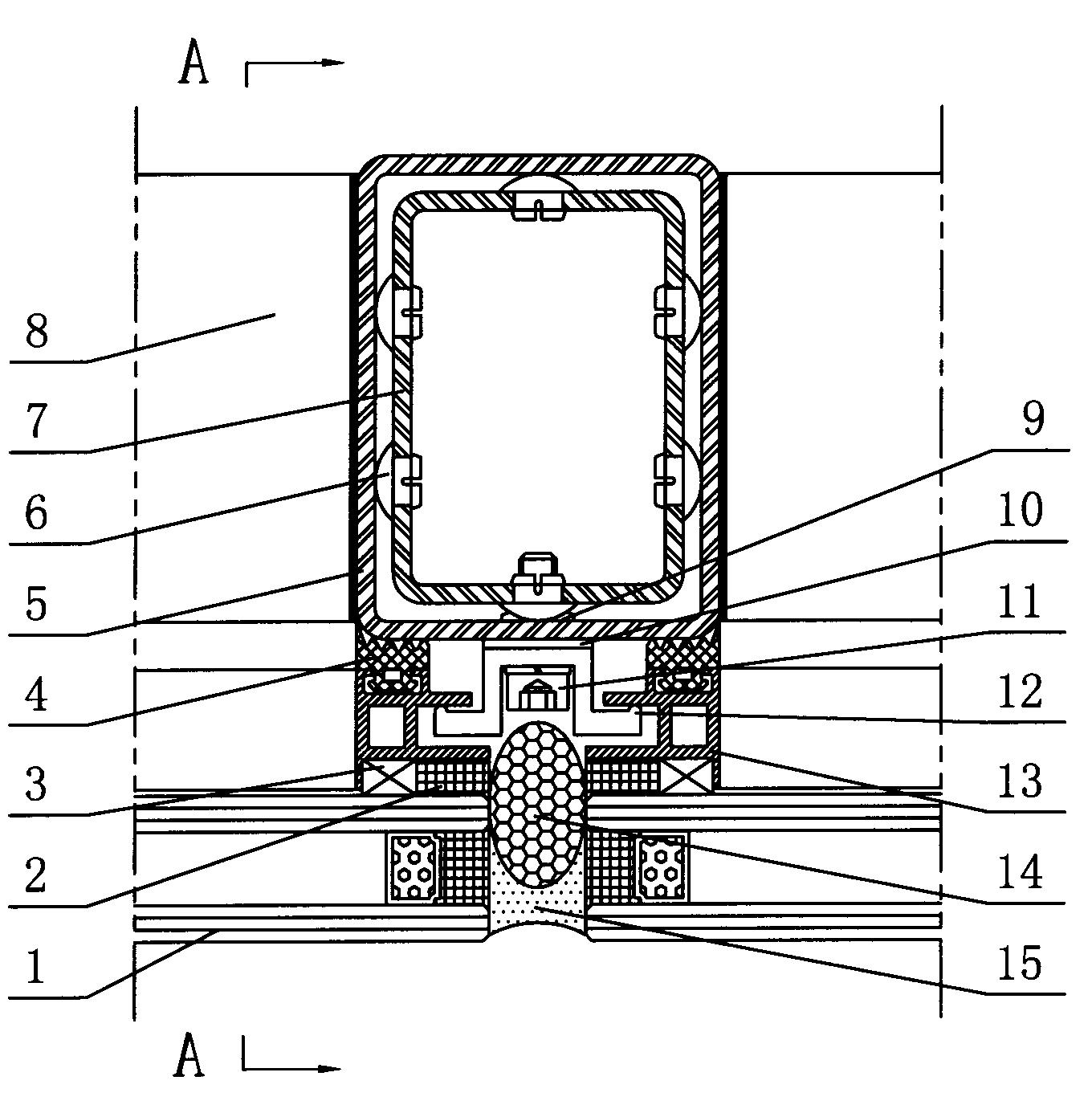

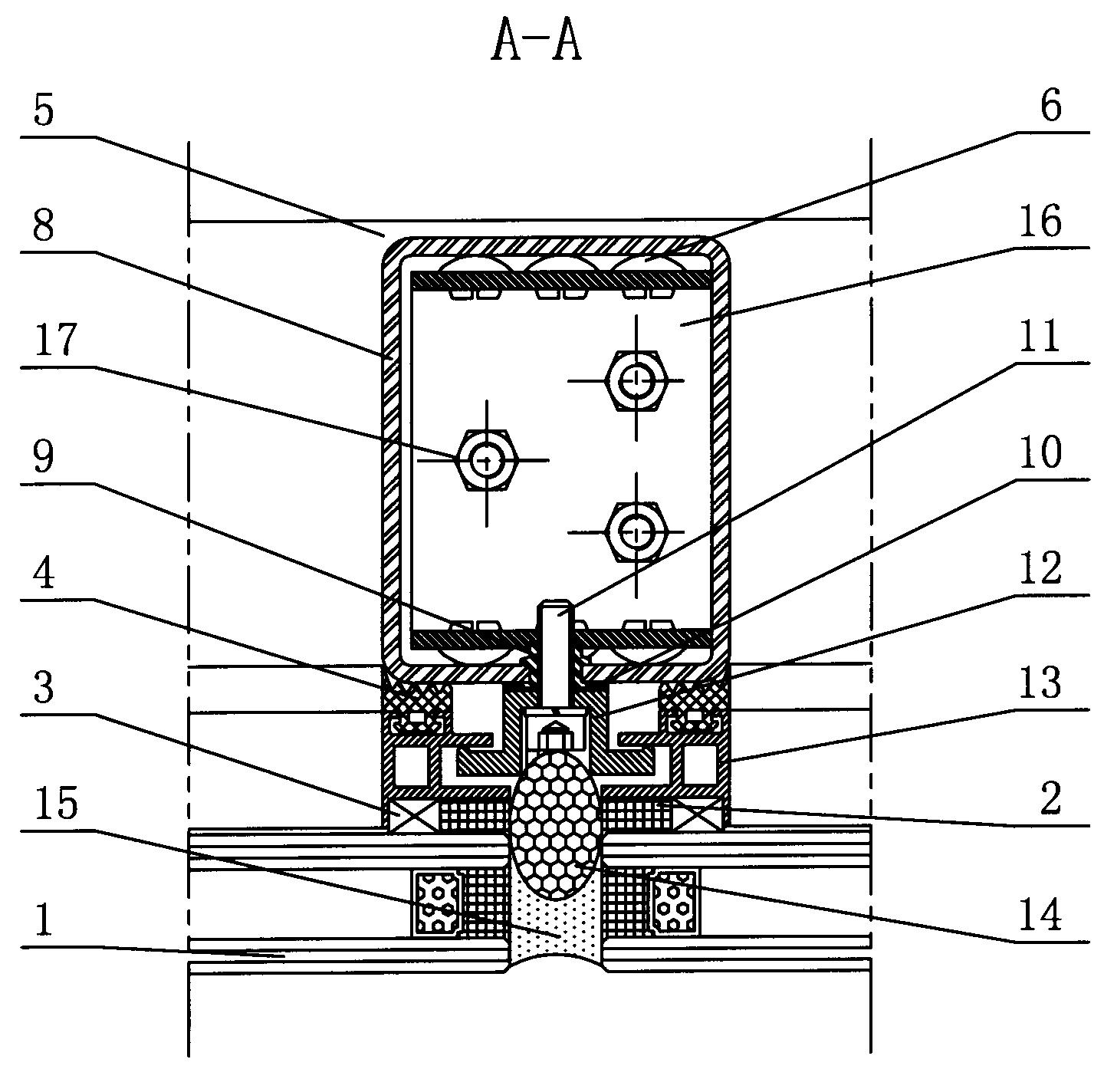

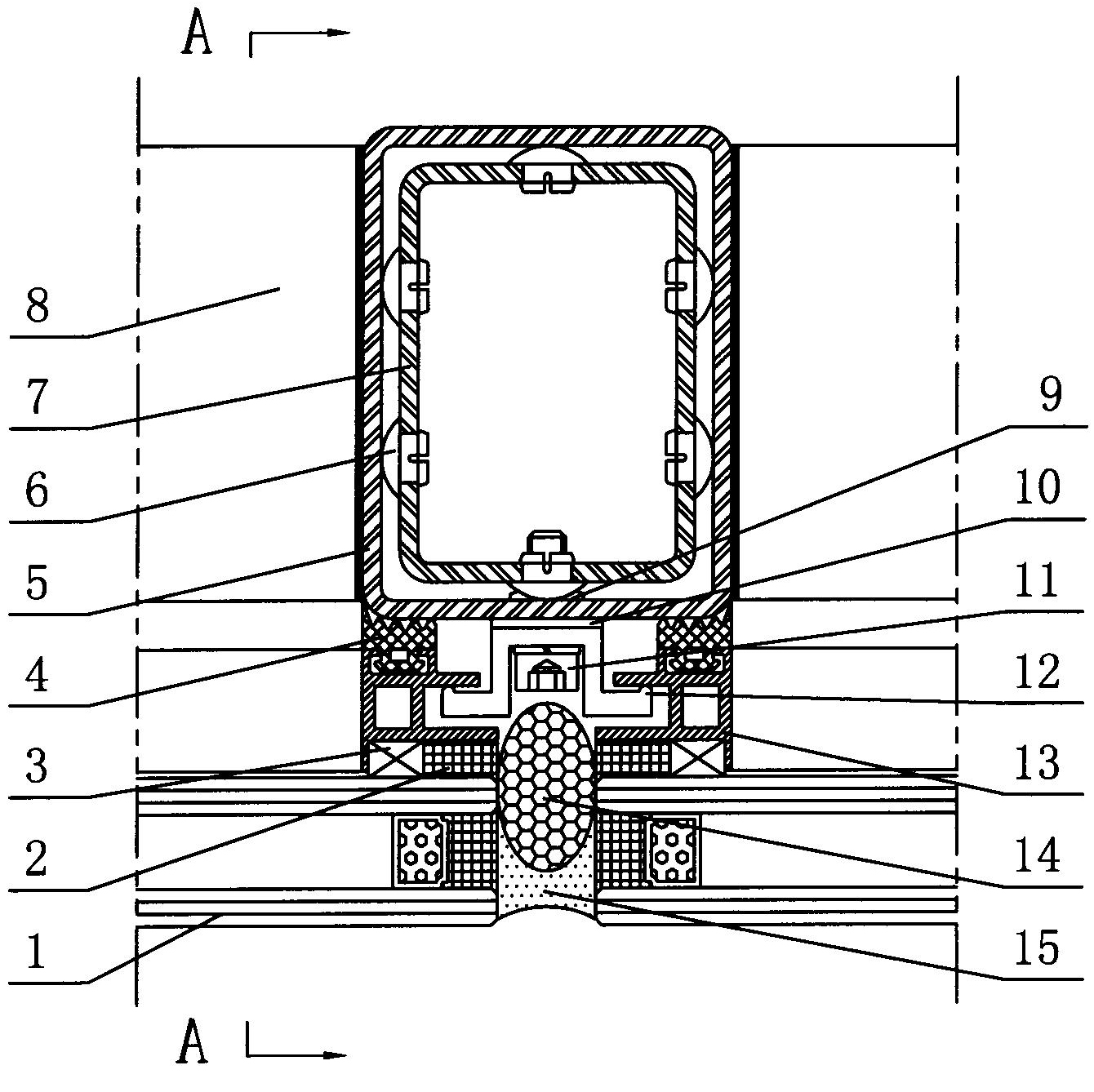

Hidden frame glass curtain wall with steel joist frame

The invention relates to a hidden frame glass curtain wall with a steel joist frame, which overcomes the defects such as poorer surface spraying effect of common steel profile, difficulty in installing inserting cores of a horizontal steel frame and a vertical steel frame of the frame, material waste and the like in the prior art. The hidden frame glass curtain wall with the steel joist frame comprises the steel joist frame, a glass plane material and a connecting assembly for fixing the glass plane material on the steel joist frame through a glass attached frame, wherein the horizontal steel frame and the vertical steel frame of the steel joist frame are made of rectangular steel profile rolled by steel plates and are spliced through an inserting core of the horizontal steel frame, the inserting core of the horizontal steel frame is made of U-shaped steel profile with two vertical surfaces and a bottom surface, which is rolled by the steel plates, an upper vertical steel frame and a lower vertical steel frame which are adjacent vertically are spliced by using the inserting core of the vertical steel frame, and the inserting core of the vertical steel frame is made of rectangular steel profile rolled by using the steel plates. The hidden frame glass curtain wall with the steel joist frame is reasonable in structural design and convenient and rapid to install, ensures the installing precision of the horizontal steel frame and the vertical steel frame of the curtain wall, is beneficial to the release of stress generated by expansion caused by heat and contraction caused by cold, is safe and reliable in use, reduces material and installing costs, and further improves the sealing property and the decoration effect of the curtain wall.

Owner:SHENYANG YUANDA ALUMINUM IND GROUP

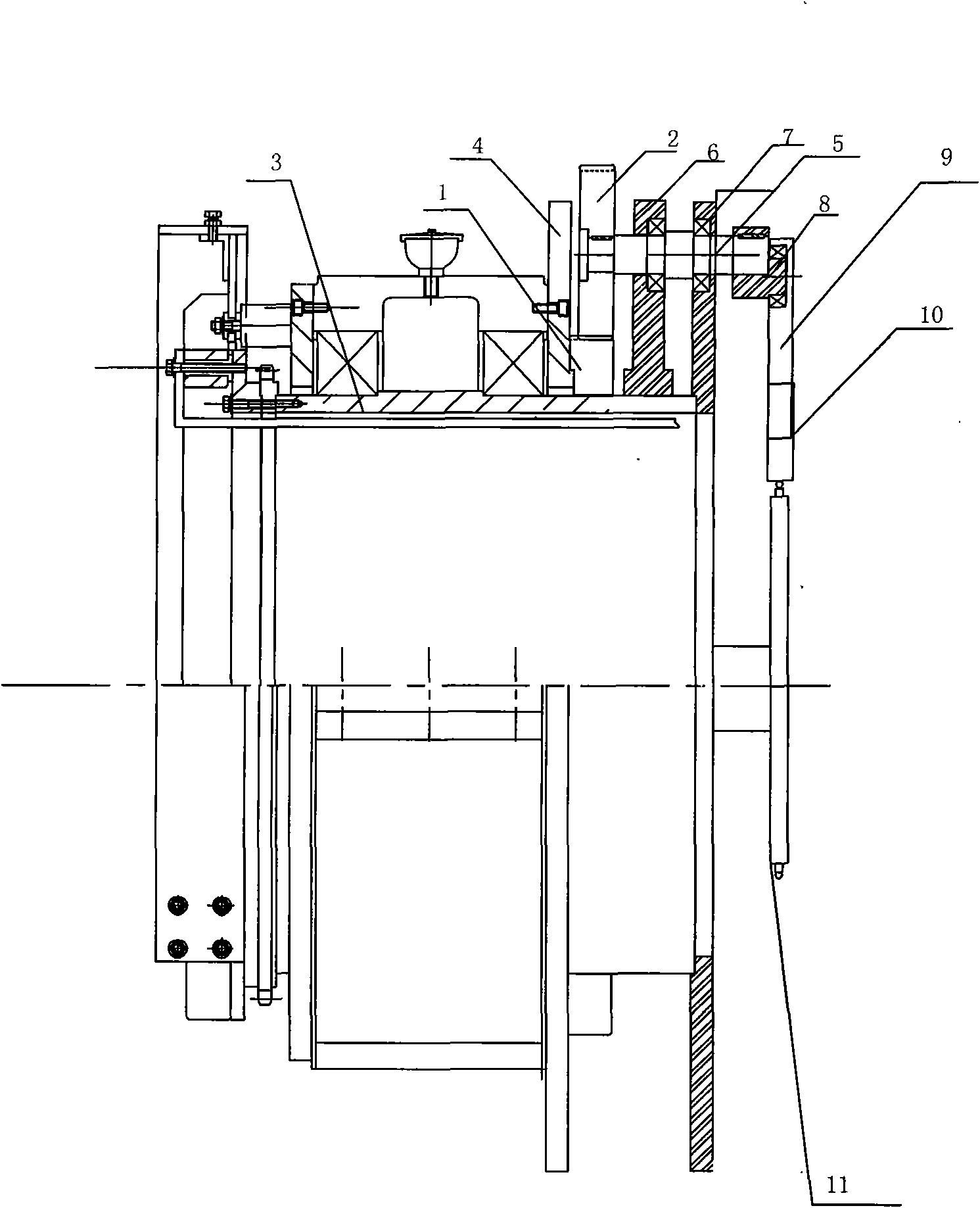

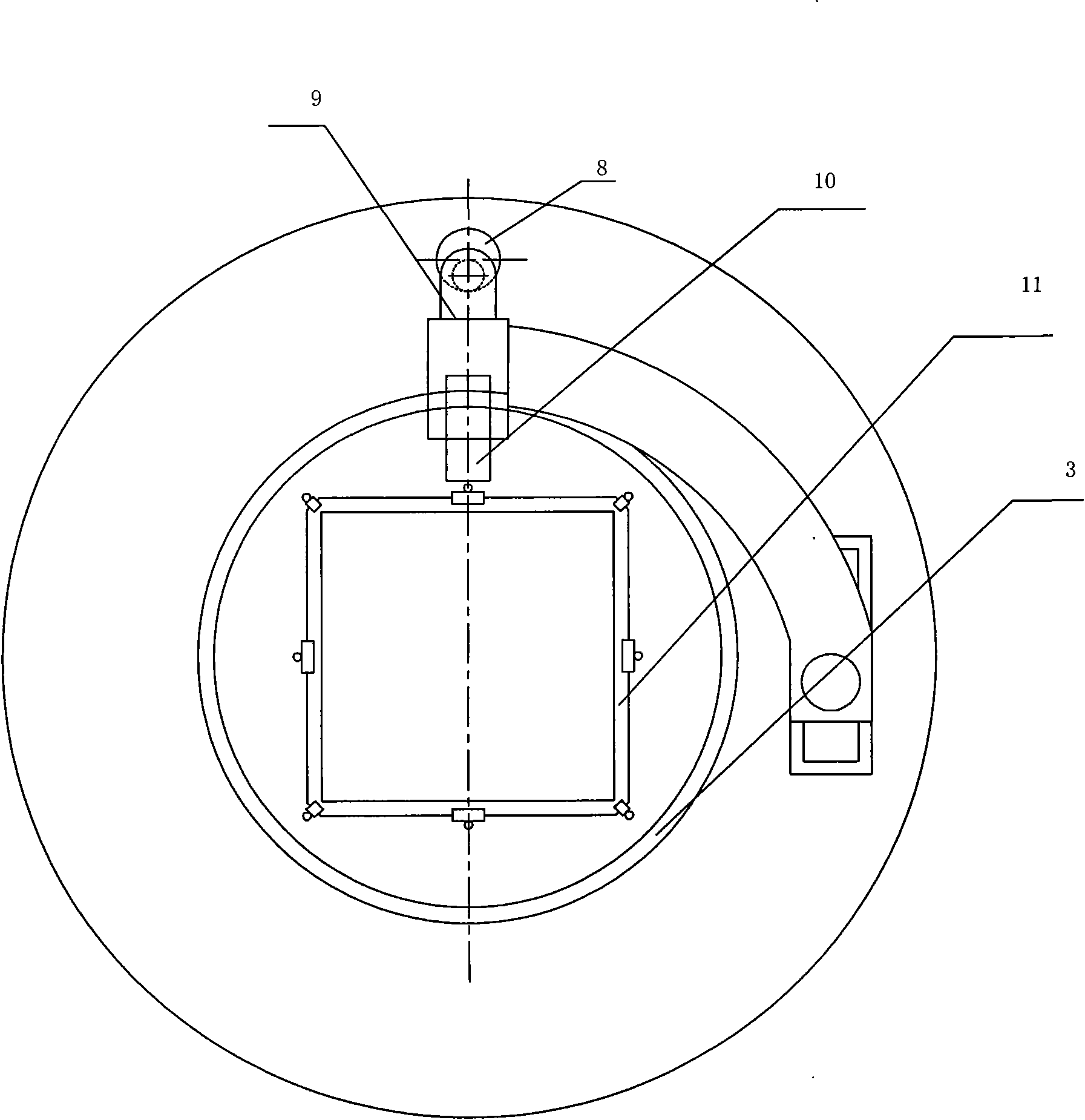

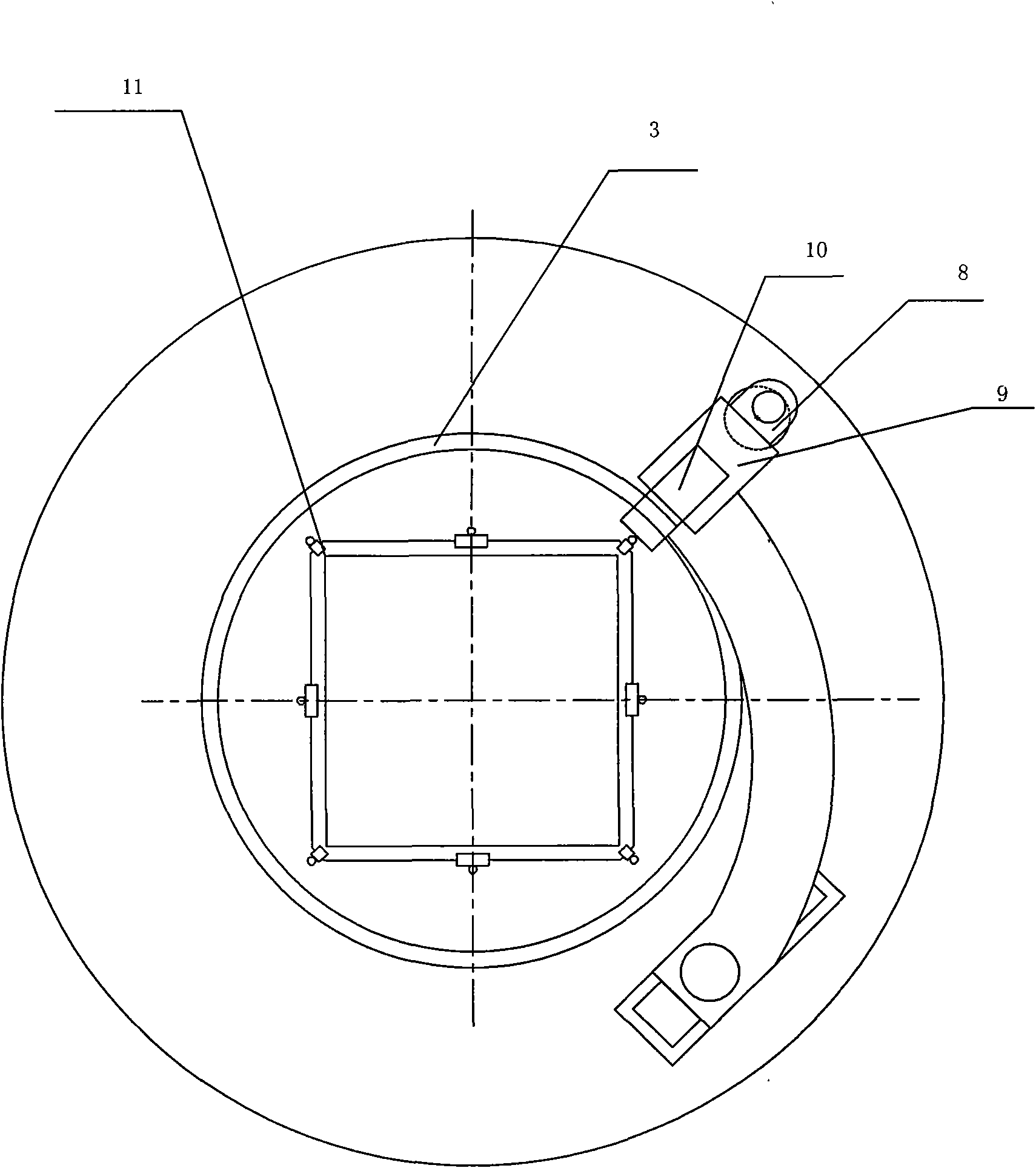

Welding automatic adjusting device for multifunctional seam welder

InactiveCN101590565AEnsure consistencyGood for stress reliefWelding with roller electrodesEngineeringSeam welding

The invention discloses a welding automatic adjusting device for a multifunctional seam welder. A master gear(1) is fixed on the outer surface of a seam welding cylinder(3); an auxiliary gear(2) is meshed with the master gear(1), and a rotary shaft(5) in the center of the auxiliary gear(2) is supported by a bearing(7) arranged in a bearing block(6); one end of the rotary shaft(5) is fixedly connected with the auxiliary gear(2), while the other end is connected with an eccentric wheel(8) connected with a connecting rod(9); one end of the connecting rod(9) is fixedly connected with the eccentric wheel(8), while the other end is connected with a movable electrode(10), which is opposite to a fixed electrode(11) of the seam welder; and the seam welding cylinder(3) drives the rotary shaft(5) to rotate through the master gear(1) and the auxiliary gear(2) orderly, the rotary shaft(5) drives the eccentric wheel(8) to rotate, and the eccentric wheel(8) drives the movable electrode(10) to move around the fixed electrode(11) through the connecting rod(9).

Owner:TAIZHOU HENGYUAN BUILDING MATERIALS MACHINERY

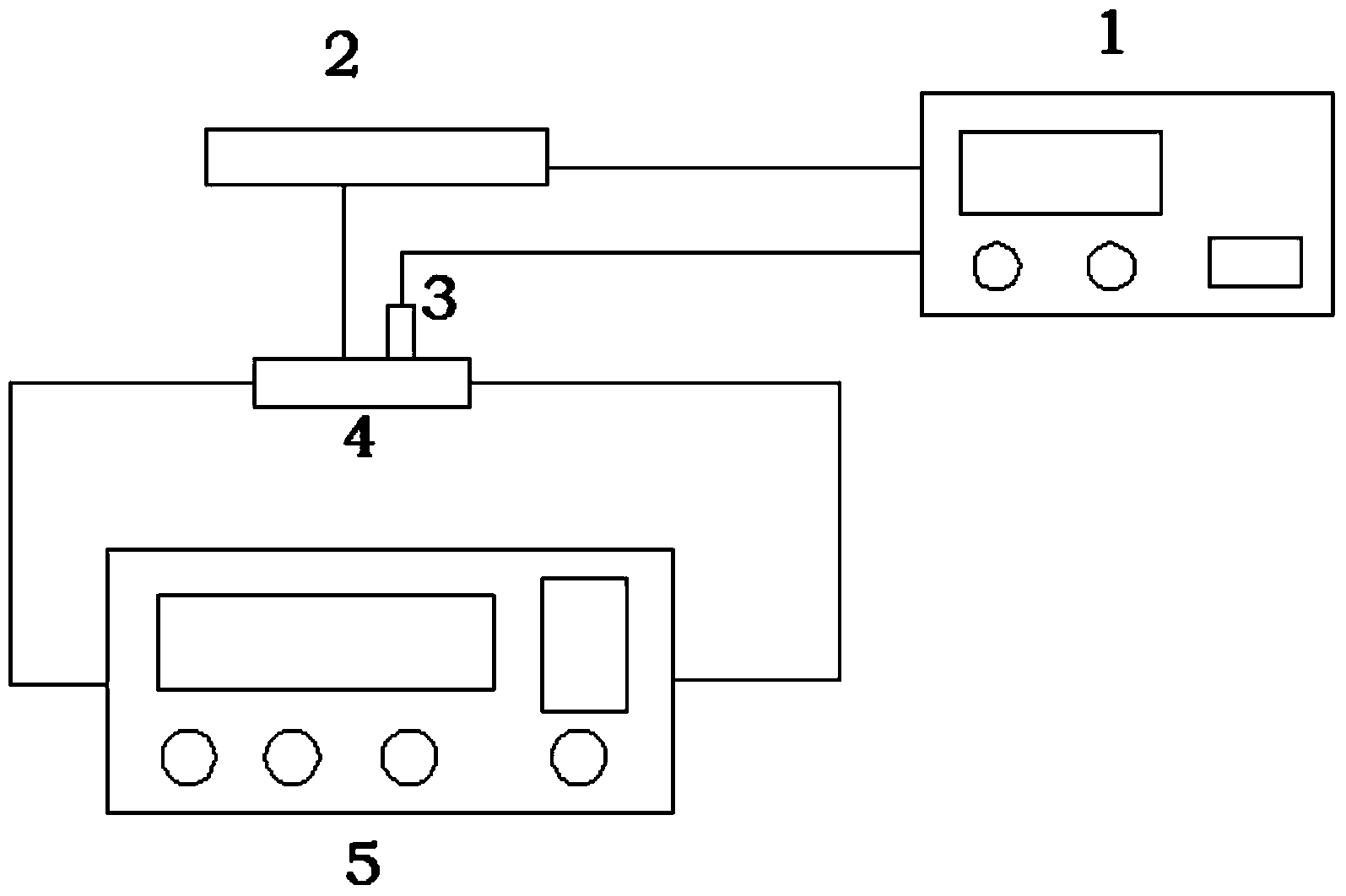

Thermoelectric composite treatment method suitable for reducing residual stress of metal materials

InactiveCN103805770AReduce residual stressIncrease mobilityProcess efficiency improvementHeating timeTest sample

The invention relates to a thermoelectric composite treatment method suitable for reducing residual stress of metal materials. The method comprises the following steps: 1, preparing a test sample; 2, placing a to-be-treated metal workpiece (4) at two ends of electrodes of a pulsed power supply; 3, placing an infrared heating pipe (2) near the surface of the to-be-treated metal workpiece (4); 4, starting an infrared heating controller (1) and setting the infrared heating temperature at 180-190 DEG C; 5, when the infrared heating temperature reaches 180 DEG C, starting the pulsed power supply (5) at the same time; and 6, simultaneously operating the infrared heating pipe (2) and the pulsed power supply (5) for 10 minutes till the whole treatment process is completed, thereby completing the treatment of the to-be-treated metal workpiece (4). The method disclosed by the invention has the advantages that temperature-controllable low temperature thermal field treatment is carried out on metal materials by using a portable movable infrared heating device, so that the problems that in the traditional heat treatment, the heating time is long, the whole workpiece needs to be put in and other operations are inconvenient to carry out are solved.

Owner:湖南高创海捷工程技术有限公司 +1

Acrylic pressure-sensitive adhesive composition for polarizing plate,containing a photo-initiator group

ActiveUS20100129568A1Good for stress reliefImprove light leakageLiquid crystal compositionsSynthetic resin layered productsPolymer scienceMeth-

The present invention relates to an acrylic pressure-sensitive adhesive composition which comprises a (meth)acrylic copolymer comprising an alkyl(meth)acrylic acid ester monomer, in which alkyl has 2 to 14 carbon atoms, and a (meth)acrylic acid ester monomer containing a copolymerizable photo-initiator group, wherein it has a gel fraction of 10 to 55% and a swelling ratio of 30 to 110, and a sol (uncross-linked polymer) eluted in final pressure-sensitive adhesive with a solvent (ethyl acetate) has a weight average molecular weight of 600,000 or more; and a polarizing plate and a liquid crystal display device, comprising the same. The polarizing plate according to the present invention has an excellent adhesion durability under a high temperature or a high temperature and humidity condition, has an excellent low light leakage property by effectively providing stress release property, and may greatly improve productivity for polarizing plates, by using photo-curing.

Owner:SHANJIN OPTOELECTRONICS SUZHOU CO LTD

Cargo restraint anchor device for pick-up trucks

InactiveUS20070207003A1Easy to installEnhanced inhibitory effectFlexible elementsCargo supporting/securing componentsPickup truckEngineering

Herein is disclosed an improvement for a tie-down and attach-point anchor device for pickup truck beds that clamps to the downward protruding flange of a pickup truck's inner side rail or other similar available surface having an exposed edge. The anchor incorporating a slotted head capable of swiveling to accommodate different angles at which straps, bungees, ropes, and rigid members may be placed to secure or support cargo.

Owner:ROH WARREN

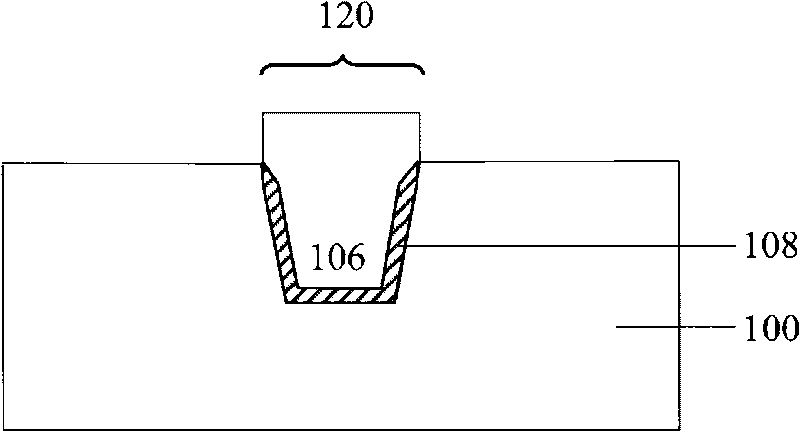

Forming method of silicon through hole

ActiveCN104576508AReduce layeringReduce crackingSemiconductor/solid-state device manufacturingLarge deformationDiffusion barrier

The invention relates to a forming method of a silicon through hole. The forming method comprises the following steps: providing a semiconductor substrate; forming a ring-shaped through hole in the semiconductor substrate, wherein the semiconductor substrate inside the ring-shaped through hole is an isolated semiconductor pillar; forming diffusion barrier layers on the side wall and at the bottom of the ring-shaped through hole; full filling the ring-shaped through hole with a conductive layer; removing all the semiconductor pillar or removing part of the semiconductor pillar to reserve part of a thickness until an opening with a depth-to-width ratio of greater than or equal to 20 is formed; and sealing the opening to form an air gap. According to the method, firstly the ring-shaped through hole is formed, the ring-shaped through hole is full filled with the conductive layer, then the semiconductor pillar formed inside the ring-shaped through hole in a surrounding manner is removed to form the opening and the opening is sealed to form the air gap; the air gap provides a large deformation space for plastic deformation of the conductive layer and is beneficial for releasing stresses in the conductive layer and an insulating layer; the possibility that a silicon through hole generates the layering and cracking phenomena is reduced; and reliability of the silicon through hole is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

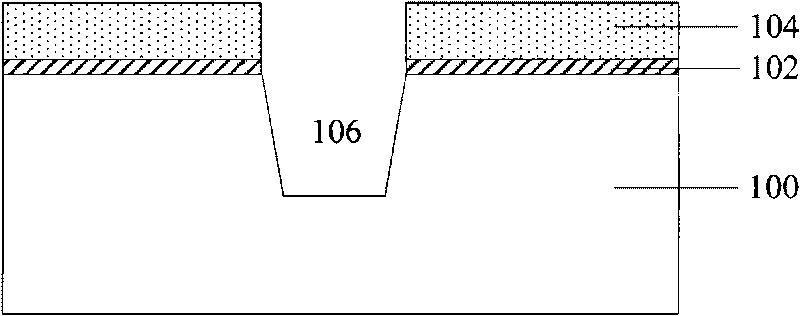

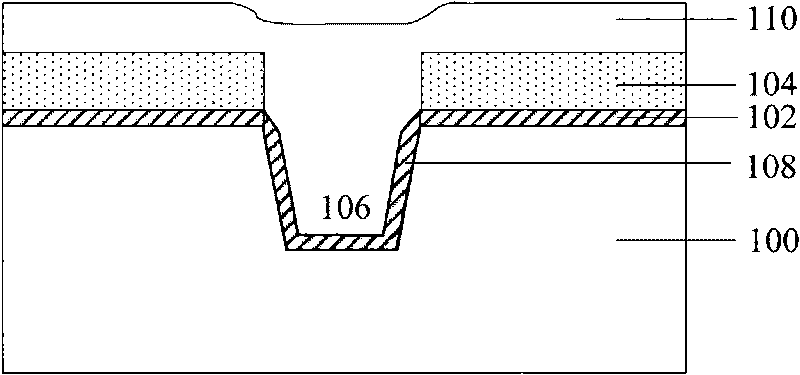

Method for manufacturing shallow trench isolation structure

InactiveCN101728308AShort exposure timeHigh strengthSemiconductor/solid-state device manufacturingCorrosionOxide

The invention provides a method for manufacturing a shallow trench isolation structure. The method comprises the following steps: forming a pad oxide layer and a corrosion barrier layer on a semiconductor substrate in sequence; etching the corrosion barrier layer, the pad oxide layer and the semiconductor substrate to form a shallow trench; carrying out laser heat treatment on the semiconductor substrate in the shallow trench, and introducing oxygen into the substrate to form a lining oxide layer; filling insulating oxide layers in the shallow trench; removing the corrosion barrier layer and the pad oxide layer until the semiconductor substrate is exposed so as to form the shallow trench isolation structure. The method improves the quality of the subsequent lining oxide layer, reduces leakage current, and improves the quality of semiconductor devices.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com