OTP (one-time programmable memory) device and manufacturing method thereof

A manufacturing method and device technology, which can be used in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve problems such as the reduction of memory area, and achieve the effect of improving compatibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

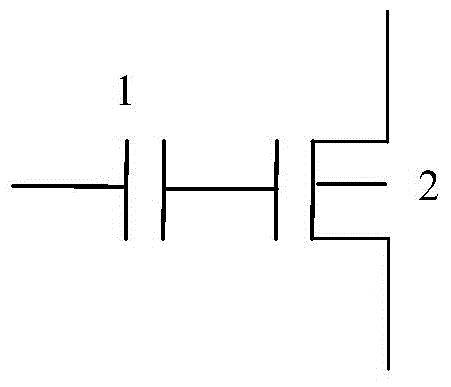

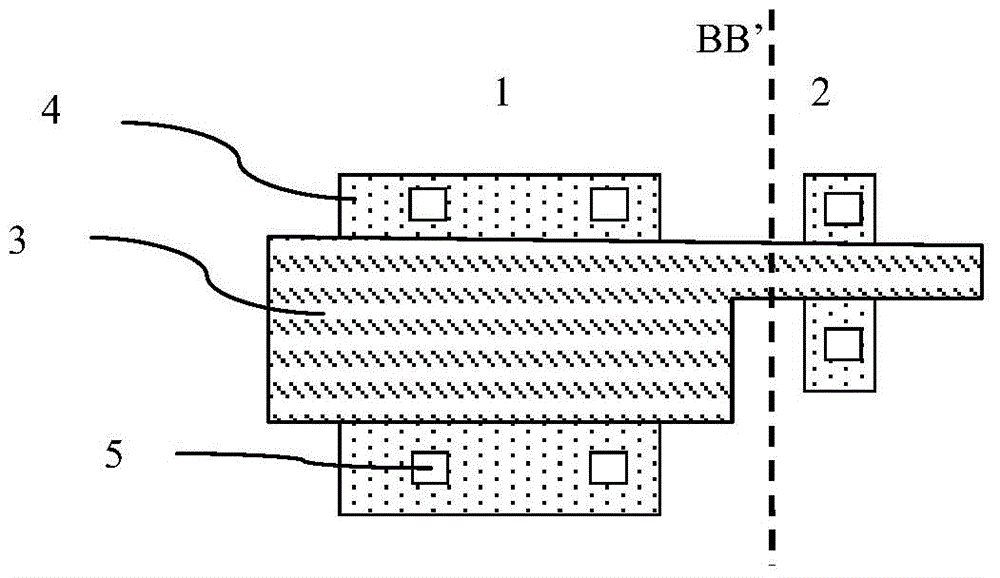

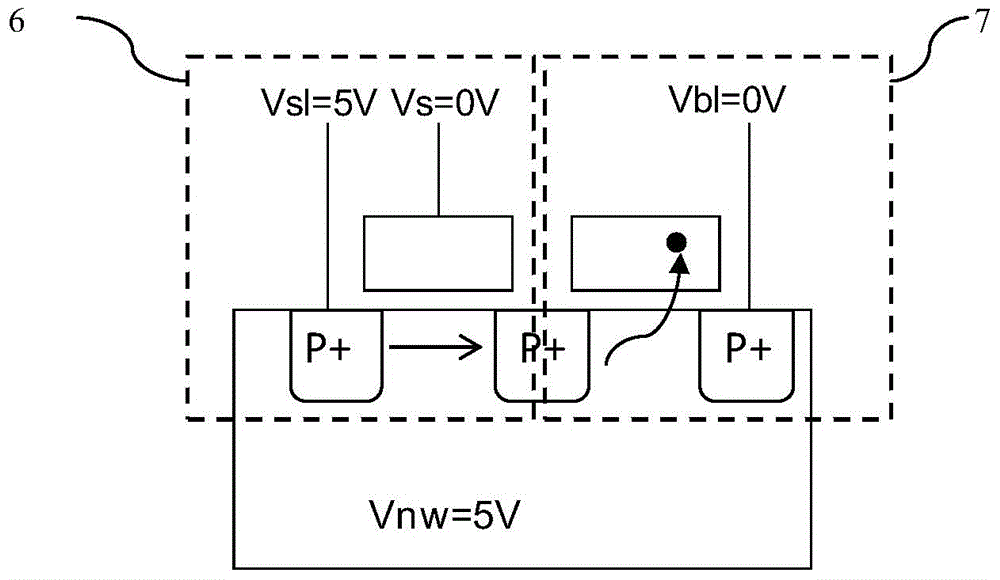

[0044] Such as image 3 Shown is a schematic structural diagram of an OTP device according to an embodiment of the present invention. The unit structure of the OTP device in the embodiment of the present invention includes a PMOS transistor and a PNPN thyristor.

[0045] The PMOS transistors include:

[0046] The N well 2 is formed in the semiconductor substrate 1 , and the N well 2 extends downward to a certain depth from the top surface of the semiconductor substrate 1 . Preferably, the semiconductor substrate 1 is a silicon substrate.

[0047] The gate structure includes a gate dielectric layer 3 and a polysilicon gate 4 sequentially formed above the semiconductor substrate 1; the surface of the N well 2 covered by the gate structure is used to form a channel region. Preferably, the gate dielectric layer 3 is a gate oxide layer.

[0048] P+ doped source region 7b and drain region 7a formed in the surface region of the N well 2, the surface region of the N well 2 is also...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More