A kind of ldmos transistor structure and preparation method thereof

A technology of transistors and semiconductors, applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve problems such as unstable working environment of LDMOS devices, large area occupied by LDMOS devices, uneven distribution of electric field in the gate region, etc. , to achieve the effects of reduced size, increased charge and discharge rate, and compact distribution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

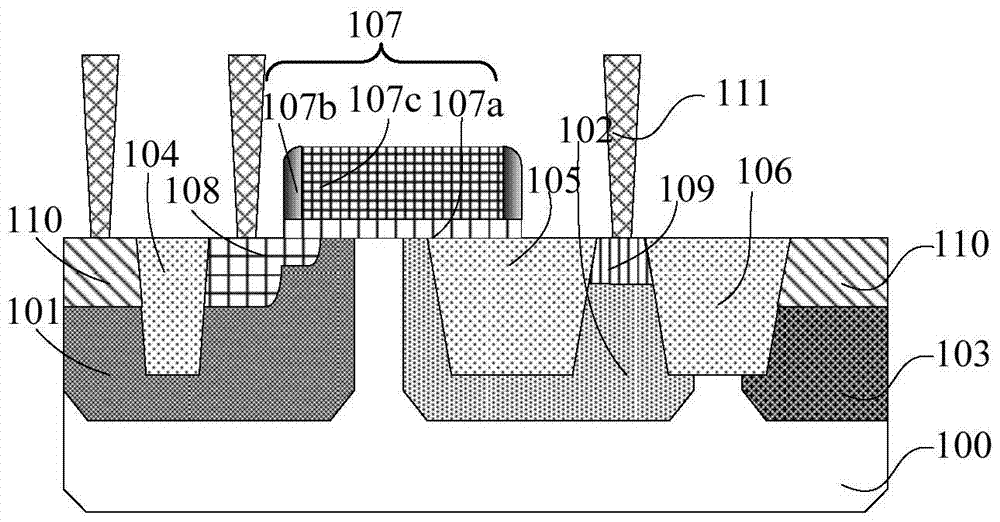

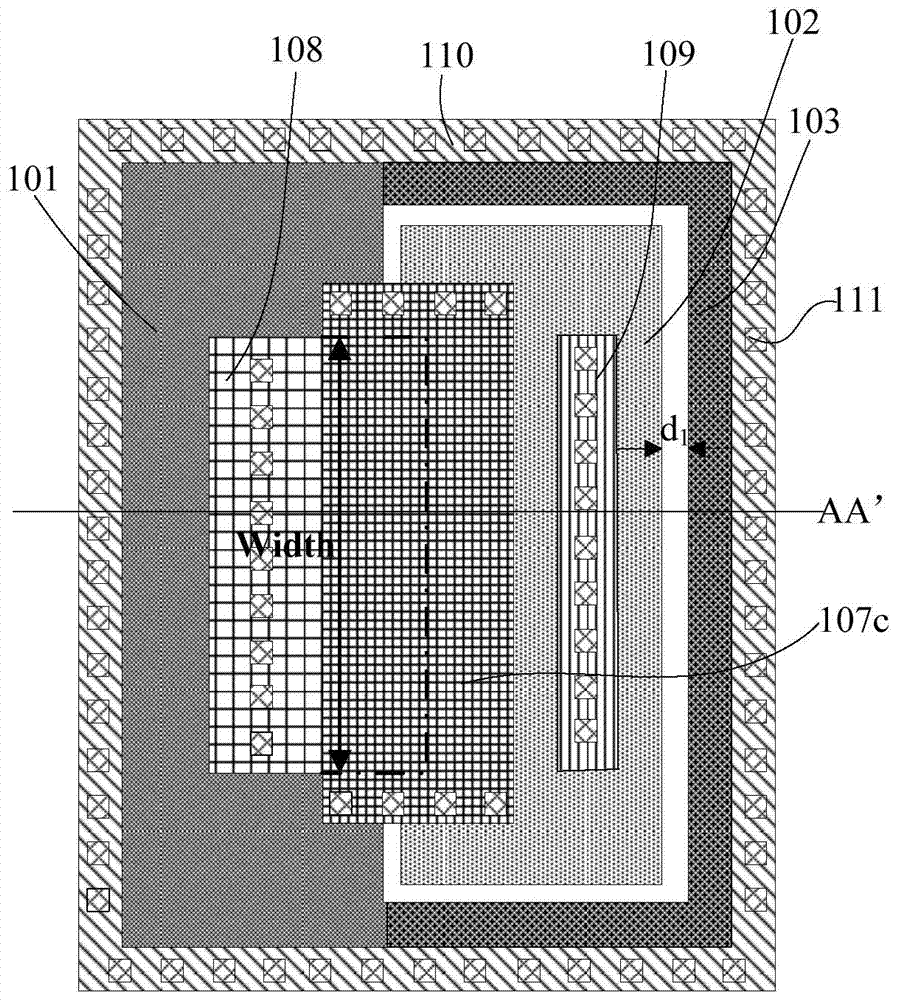

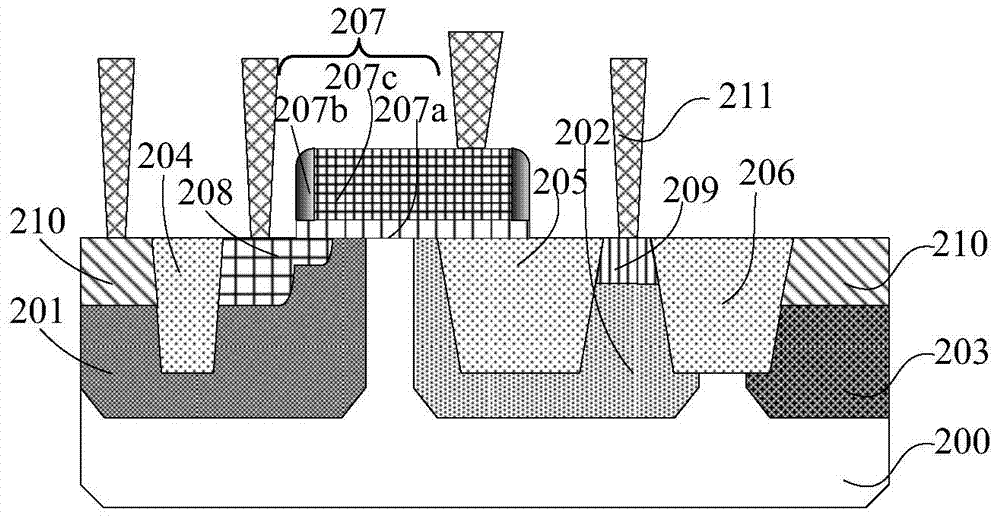

[0048] see figure 2 , is a schematic structural view of the LDMOS transistor of the present invention, the LDMOS transistor structure at least includes: a semiconductor substrate 200; a first high voltage well region 201, a second high voltage well region 202 and a first high voltage well region 202 formed in the semiconductor substrate 200 The third high-voltage well region 203; the doping type of the second high-voltage well region 202 is opposite to that of the first high-voltage well region 201 and the third high-voltage well region 203; formed in the first high-voltage well region The first shallow trench isolation region 204 in 201; the second shallow trench isolation region 205 formed in the second high voltage well region 202 and the second high voltage well region 202 and the third high voltage well The third shallow trench isolation region 206 between regions 203; the gate region 207 formed on the semiconductor substrate 200 and covering part of the first high volta...

Embodiment 2

[0092] In this embodiment, the preparation method of the PLDMOS transistor is taken as an example. The preparation steps of the PLDMOS transistor are exactly the same as the preparation steps of the NLDMOS transistor in Example 2. The difference between the two mainly lies in:

[0093] In step 1), the provided substrate is an N-type substrate. During the process of forming the first high-voltage well region 201 , the second high-voltage well region 202 and the third high-voltage well region 203 , the first high-voltage well region 201 and the third high-voltage well region 203 are formed. N-type ion implantation is performed on the third high-voltage well region 203, and P-type ion implantation is performed on the second high-voltage well region 202;

[0094] In step 4), during the process of forming the source region 208 and the drain region 209, P-type ion implantation is performed on them, and during the process of forming the body lead-out region 210, N-type ion implantatio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com