n-type ldmos device and process method

A process method, N-type technology, applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of unsatisfactory breakdown voltage, high surface electric field strength, no electric field distribution optimization, etc., to improve the potential distribution. , the effect of reducing the electric field strength and increasing the breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

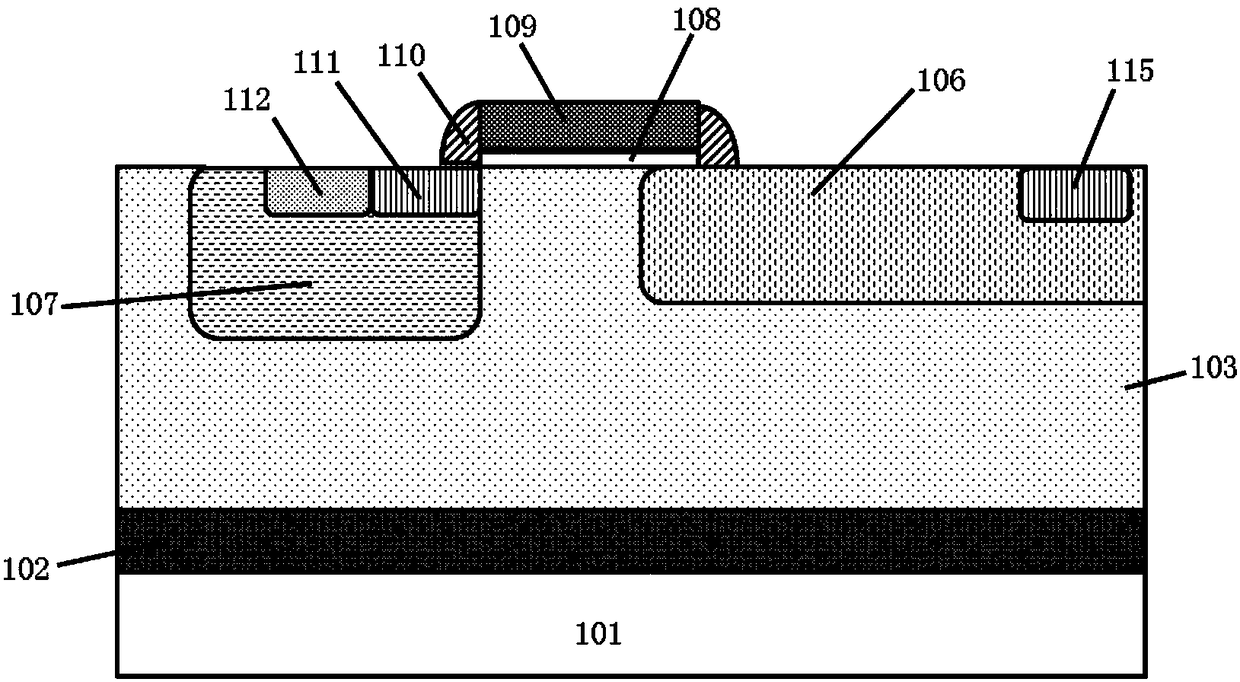

[0023] The N-type LDMOS device described in the present invention, such as Figure 7 As shown, there is an N-type buried layer 102 on the P-type substrate 101, and an N-type deep well 103 is on the buried layer 102; a P well 107 is provided in the N-type deep well 103, and the P well 107 contains heavily doped The P-type region 112 and the source region 111 of the LDMOS device, the silicon substrate surface has a gate oxide layer 108 and a polysilicon gate 109; the N-type deep well 103 also has a drain region 115 of the LDMOS device, and the lead 114 passes through the contact The hole 113 leads out the heavily doped P-type region 112, the source region 111 and the drain region 115; the heavily doped P-type region 112 and the source region 111 in the P well 107 are isolated by the STI field oxygen 104, and the LDMOS device In the drift region, there are STI field oxygen 104 on both sides of the drain region 115, and the drift region is a layered drift region with different dep...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More